### Vertical III-V nanowire tunnel field-effect transistors a circuit perspective

Rangasamy, Gautham

2023

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA): Rangasamy, G. (2023). Vertical III-V nanowire tunnel field-effect transistors: a circuit perspective. Electrical and Information Technology, Lund University.

Total number of authors:

Creative Commons License: CC BY

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 22. Dec. 2025

## Vertical III-V Nanowire Tunnel Field-Effect Transistors: A Circuit Perspective

**Doctoral Thesis**

Gautham Rangasamy

Department of Electrical and Information Technology Lund, December 2023

Academic thesis for the degree of Doctor of Philosophy, which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Friday, 15<sup>th</sup> December 2023, at 9:15 a.m. in lecture hall E:B, Department of Electrical and Information Technology, Ole Römers Väg 3, 223 63 Lund, Sweden. The thesis will be defended in English.

The Faculty Opponent will be Francis Balestra, Director of Research CNRS, Paris, France.

| Organisation: LUND UNIVERSITY Department of Electrical and Information Technology Ole Römers Väg 3 223 63 Lund Sweden  Author: Gautham Rangasamy | Document Type:<br>DOCTORAL THESIS                                              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

|                                                                                                                                                  | Date of Issue:<br>December 2023                                                |  |

|                                                                                                                                                  | Sponsoring Organisation(s):                                                    |  |

|                                                                                                                                                  | Swedish Foundation for Strategic Research (SS<br>Swedish Research Council (VR) |  |

Title:

Vertical III-V Nanowire Tunnel Field-Effect Transistors: A Circuit Perspective

#### Abstract:

The energy scaling of integrated circuits has reached a limit because the operating voltage of Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFET) based switches has reached its minimum value. MOSFETs are limited by thermionic emission and cannot achieve a subthreshold swing (SS) below 60 mV/decade at room temperature. Tunnel Field-Effect Transistors (TFET), which operate on field modulation of band-to-band tunneling (BTBT), can deliver SS less than 60 mV/dec and are considered as a potential alternative for MOSFETs to further scale down the supply voltage.

This thesis work studied the capabilities and limitations of n-type TFETs based on III-V vertical nanowires and their circuit implementation. TFETs were fabricated using vertical  $\ln A_S/GaSb$  or  $\ln A_S/InGaAsSb/GaSb$  nanowires of high material quality, switching from  $\ln A_S/GaSb$  to  $\ln A_S/InGaAsSb/GaSb$  allowed for optimization of the heterojunction, resulted in improvement of device metrics. Along with heterostructure optimization, the dopant introduction and concentration were systematically varied to achieve devices with record performance. These devices achieved a minimum subthreshold swing of 42 mV/decade and a record high  $I_{60}$  of 1.2  $\mu A/\mu m$  at a drive voltage of 0.5 V. The stability and high yield of the process allowed for statistical study of correlations between important device parameters such as  $I_{60}$ , on-current, subthreshold swing, and off-current. The implementation of circuits was also aided by sufficient process repeatability and yield.

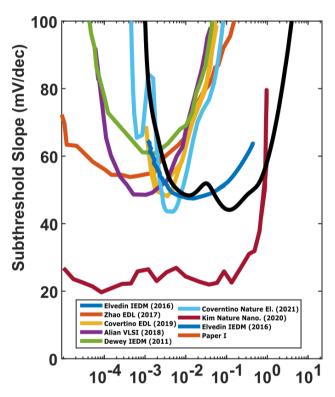

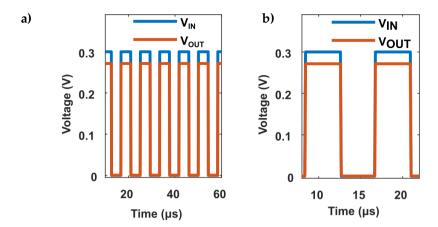

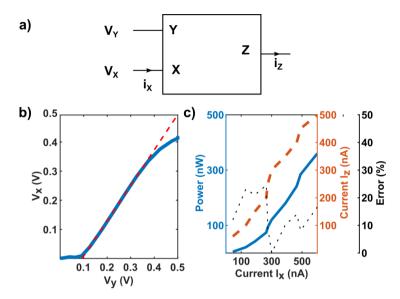

To implement circuits based on these TFETs, the fabrication process was optimized with introduction of vias and nonorganic spacers. Voltage based circuits in the following configurations were implemented: a current mirror, a diodeconnected inverter and a cascode buffer. Individual TFETs in the circuit operate well below 60 mV/dec operation with minimum achieved subthreshold swing (SS) of 30 mV/dec at drain voltage of 400 mV. In circuit operation, individual devices were connected via FEOL and are biased at 300 mV supply voltage, with an input frequency of 200 kHz. To explore current-mode based design principle, we have implemented a current conveyor circuit, which exhibits large-signal voltage gain of 0.89 mV/mV, a current gain of 1 nA/nA and an operating frequency of 320 kHz.

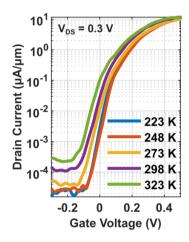

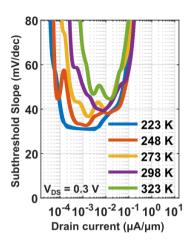

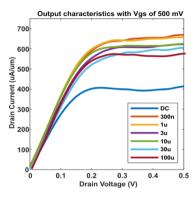

Additionally, self-heating in a vertical nanowire device was examined using pulsed IV methodology. The results indicate that the intrinsic temperature rises to 385 K when the device is operated in DC at room temperature (300 K) with a thermal time constant of 1  $\mu$ s. We find that self-heating is a limiting factor for device performance.

#### Keywords:

Low-Power Electronics, Self-Heating, Steep Slope Devices, Tunnel Field-Effect Transistors, Vertical Nanowire, III-V Semiconductors.

| Classification System and/or Index Terms Language:                                  |                                      |                                      |

|-------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|

| Electronic Engineering, Nanotechnology                                              | English                              |                                      |

| Supplementary Bibliographical Information:                                          | ISBN (printed):<br>978-91-8039-887-9 |                                      |

| Key title and ISSN:<br>Series of Licentiate and Doctoral Theses; ISSN 1654-790X 166 |                                      | ISBN (digital):<br>978-91-8039-886-2 |

| Recipient's Notes:  Number of Pages: ???  Security Classification: Unclassified     |                                      | Price:                               |

|                                                                                     |                                      | •                                    |

#### General Permissions

I, the undersigned, being the copyright owner and author of the above-mentioned thesis and its abstract, hereby grant to all reference sources permission to publish and disseminate said abstract.

Signature: Gautham Rangasamy Date: 15 December 2023

# Vertical III-V Nanowire Tunnel Field-Effect Transistors: A Circuit Perspective

**Doctoral Thesis**

Gautham Rangasamy

Department of Electrical and Information Technology Lund, December 2023 Gautham Rangasamy

Department of Electrical and Information Technology

Lund University

Ole Römers Väg 3, 223 63 Lund, Sweden

Series of Licentiate and Doctoral Theses ISSN 1654-790X 166 ISBN 978-91-8039-887-9 (printed) ISBN 978-91-8039-886-2 (digital)

#### © 2023 Gautham Rangasamy

This thesis is typeset using  $\LaTeX$  with the body text in Palatino and Goudy Initials, headings in Helvetica, text in figures in Arial, and the body text in Appendix A in Computer Modern.

Frontispiece: Array of nanowires

Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden.

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without restriction.

## To Yalini

"It's true that everything we wish for will not come to be, but things that we must do must always begin with a wish"

- Kishimoto

## **Abstract**

HE energy scaling of integrated circuits has reached a limit because the operating voltage of Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFET) based switches has reached its minimum value. MOSFETs are limited by thermionic emission and cannot achieve a subthreshold swing (SS) below 60 mV/decade at room temperature. Tunnel Field-Effect Transistors (TFET), which operate on field modulation of band-to-band tunneling (BTBT), can deliver SS less than 60 mV/dec and are considered as a potential alternative for MOSFETs to further scale down the supply voltage.

This thesis work studied the capabilities and limitations of n-type TFETs based on III-V vertical nanowires and their circuit implementation. TFETs were fabricated using vertical InAs/GaSb or InAs/InGaAsSb/GaSb nanowires of high material quality, switching from InAs/GaSb to InAs/InGaAsSb/GaSb allowed for optimization of the heterojunction, resulted in improvement of device metrics. Along with heterostructure optimization, the dopant introduction and concentration were systematically varied to achieve devices with record performance. These devices achieved a minimum subthreshold swing of 42 mV/decade and a record high I<sub>60</sub> of 1.2  $\mu$ A/ $\mu$ m at a drive voltage of 0.5 V. The stability and high yield of the process allowed for statistical study of correlations between important device parameters such as I<sub>60</sub>, on-current, subthreshold swing, and off-current. The implementation of circuits was also aided by sufficient process repeatability and yield.

To implement circuits based on these TFETs, the fabrication process was optimized with introduction of vias and non-organic spacers. Voltage based circuits in the following configurations were implemented: a current mirror,

a diode-connected inverter and a cascode buffer. Individual TFETs in the circuit operate well below 60 mV/dec operation with minimum achieved subthreshold swing (SS) of 30 mV/dec at drain voltage of 400 mV. In circuit operation, individual devices were connected via FEOL and are biased at 300 mV supply voltage, with an input frequency of 200 kHz. To explore current-mode based design principle, we have implemented a current conveyor circuit, which exhibits large-signal voltage gain of 0.89 mV/mV, a current gain of 1 nA/nA and an operating frequency of 320 kHz.

Additionally, self-heating in a vertical nanowire device was examined using pulsed IV methodology. The results indicate that the intrinsic temperature rises to 385 K when the device is operated in DC at room temperature (300 K) with a thermal time constant of 1  $\mu$ s. We find that self-heating is a limiting factor for device performance.

## Popular Science Summary

HE unimaginable proliferation of electronics in our daily life, be it computing, healthcare, communication, transport, or leisure has fundamentally changed our way of living. The convenience and improvement in quality of our daily life is enabled by terabytes in data storage, data processing, data communication enabled by trillions of transistors, guzzling terawatts of power. With the emergence of new fields in AI, Neuromorphic Computing, Quantum Computing, Internet of Things, to name a few, we can be rest assured of further increase in electronic systems in our daily life. It puts us in an fascinating time, quasi -science fiction even, as we speculate on the enormous potential the field will bring. The caveat, of course, is the enormous increase in data produced and the accompanying energy consumption.

As all the electronics system are made with transistors, designing more energy efficient transistors could be one way of mitigating the increasing energy consumption. Transistor, in essence, is an electronic switch, which controls the flow of charges between two charge reservoirs, source and drain. The gate, the controlling terminal, determines the amount of current flow between the terminals. This concept can be implemented by exploiting a variety of physical phenomena, material systems, and device architectures. Over the past decades, Si based Metal-Oxide-Semiconductor Field-Effect Transistors working on principles of thermionic emissions were favored. This emerged in part due to their ability to maintain their functionality when their physical dimensions and supply voltages were scaled down, leading to lower power consumption. Below 10 nm, miniaturization of transistors hit a roadblock due

to the degradation of the transistor to switch between the on- and off-states due to quantum effects.

With this view in mind, a simple proposition can be made. Instead of suppressing these quantum effects at low dimensions, we could exploit them to solve our power consumption issues. Tunnel FET is one such device where we use our adversity to our advantage and utilize quantum mechanical tunneling to make low power switches. This proposition forms the basis of the thesis work. We explore the feasibility of TFETs in low-power domain and how they would perform compared to conventional transistors. Building on the knowledge that III-V materials offer better performance and vertical structure improves packing density, vertical III-V TFETs were employed. These TFETs achieved in the thesis work are state-of-the-art, lowering the energy consumption with respect to MOSFETs. We pushed on study their circuit performance in voltage and current modes of operation, across military temperature range, from −55 °C to 125 °C. We found TFETs were able to maintain the same functionality as MOSFETs at lower power consumption. This feels like an important step for TFETs to go from being a promising candidate to a credible compliment for MOSFETs in energy efficient systems.

## Acknowledgments

s is hard not to compare my PhD journey with that of Test cricket. The principles remain the same for both. Take the failures, don't blame the circumstance and keep ploughing away as conditions will change favourable. The biggest similarity though is both of them are a team sport. I would like to begin by thanking my captain/ supervisor Lars-Erik. I appreicate your guidance and support throughout this journey. Yoru leadership skills are par none and hoepfully I imbibed some of it.

I would like to thank Lars Ohlsson Fhager, my co-supervisor, for the abundant time we spent discussing ideas, some great, some good and rest forgotten. Of your many admirable qualities, your approach of explaining complex ideas and attention to detail are the ones I admired the most. I would also like to thank my other co-supervisor Johannes Svensson. I am grateful for his help in structuring my thesis and innumerable advice in both the technical and personal front. Thank you Erik, for all the conversations we had over the years. It was delightful.

Of course, the journey is not worth taking without your fellow mates. I would like to thank Zhongyunshen Zhu for the infinite discussions we had about TFET, processing, career and life. Abinaya Krishnaraja for introducing me to fabrication process. Heera Menon, for the friendship, patience and lots of dinners. You are the best cook ever. Navya and Anton, for all the time we spent in the badminton court and the conversations.

I would also like to extend my gratitude to all the remarkable colleagues within the division who made the work environment not only vibrant but also relaxing with full of fun. So a great thanks goes to you, Marcus, Saketh, Phillipp, André, Hannes, Karthik, Ben, Ngoc Duc, Heera, Lars, Mattias, Anette, Navya, Patrik, Louise, Lasse, Markus, Fredrik, Karl-Magnus,

Stefan, Sebastian, Olli-Pekka, Paula, Niklas, Daniel, Mats, Johan, Andrea, and Alexandros.

Furthermore, I want to thank all the engineers and technicians in both NanoLund and EIT lab. My thesis wouldn't be possible to be completed without your tremendous help.

A shout out to my boys for all the adventures and a fond memories. Sekase, Chetase, Bangase, Thagapps, Wasim, Shaafi, Kamalesh, Krishnamoorthy, Anand, Satish, Vishal, Balaji G, Sanjay, Stephen, Gurunathar, Balaji R, Sandeep, Vivek, Yasser, Murali, Mohan, Prasanna, Nishant and Kamal. Thank you to Ferdinand, for introducing me to the wonderful sport of kickboxing and all the long conversations and mentorship.

Finally, I would like to thank my family for your unconditional love and forever support in my entire life.

Gautham Rangasamy Lund, December 2023

## Contents

| Abstract                              | V    |

|---------------------------------------|------|

| Popular Science Summary               | vii  |

| Acknowledgments                       | ix   |

| Contents                              | xi   |

| Preface                               | xv   |

| Structure of the Thesis               | XV   |

| Included Papers                       | xv   |

| Acronyms and Symbols                  | xvii |

| Acronyms and Abbreviations            | xvii |

| Latin Symbols                         | XX   |

| Greek Symbols                         | xxi  |

| Functions and Operators               | xxi  |

| INTRODUCTION                          | 1    |

| 1 Introduction                        | 3    |

| 1.1 Motivation for Conducted Research | 3    |

| 1.2 TFET Operation                    | 5    |

| 1.2.1 Band-to-Band Tunneling          | 7    |

| 1.2.2 Negative Differential Region    | 9    |

| 1.2.3 TFET Quadrants of Operation                                                  | 10 |

|------------------------------------------------------------------------------------|----|

| 1.3 Geometries                                                                     | 10 |

| 1.4 Materials and Device Performance                                               | 12 |

| 1.5 Metrics for Transistor Performance                                             | 14 |

| 1.5.1 Drive Current                                                                | 14 |

| 1.5.2 Transconductance                                                             | 15 |

| 1.5.3 Output Conductance                                                           | 16 |

| 1.5.4 Threshold Voltage                                                            | 16 |

| 1.5.5 Subthreshold Slope                                                           | 16 |

| $1.5.6 \; I_{60}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 16 |

| 2 TFET Fabrication and Heterostructure engineering                                 | 19 |

| 2.1 Nanowire Growth                                                                | 19 |

| 2.2 Fabrication Process of Vertical Nanowire Transistors                           | 20 |

| 2.2.1 Current Status of TFETs                                                      | 21 |

| 2.3 Improving the Current Levels                                                   | 23 |

| 2.3.1 Heterostructure Engineering                                                  | 23 |

| 2.3.2 Dopant Levels                                                                | 24 |

| 2.4 Benchmarking of Devices                                                        | 26 |

| 3 TFET based Circuits                                                              | 29 |

| 3.1 Voltage Mode Devices                                                           | 30 |

| 3.1.1 Current Mirror                                                               | 30 |

| 3.1.2 Inverter                                                                     | 31 |

| 3.1.3 Cascode buffer                                                               | 33 |

| 3.2 Current Mode Devices                                                           | 35 |

| 3.3 Temperature Effects                                                            | 38 |

| 4 Self-Heating in Vertical Nanowires                                               | 43 |

| 4.1 Measurement Setup                                                              | 43 |

| 4.2 Pulsed IV Based Self-Heating Extraction                                        | 44 |

| 4.3 Self-Heating in Vertical III-V Nanowire                                        | 46 |

|                                                                                    | 47 |

| 4.4 Self Heating Analysis at Cryogenic Temperature                                 |    |

| 5 Final words and Outlook                                                          | 51 |

| Bibliography                                                                       | 53 |

| APPENDICES                                                                                                                      | 63         |

|---------------------------------------------------------------------------------------------------------------------------------|------------|

| A Fabrication Steps of Vertical Nanowire Transistors                                                                            | 65         |

| PAPERS                                                                                                                          | 71         |

| I High Current Density Vertical Nanowire TFETs with I $_{60}$ > 1 $\mu$ A/ $\mu$ m                                              | <b>7</b> 3 |

| II Impact of Source Positioning and Doping on Performance<br>of Vertical III-V Nanowire Tunneling Field Effect Tran-<br>sistors | 81         |

| III $g_m/I_d$ Analysis of vertical nanowire III–V TFETs                                                                         | 89         |

| IV TFET Circuit Configurations Operating below 60 mV/dec                                                                        | 95         |

| V Self-Heating in Gate-All-Around Vertical III-V InAs/InGaAs MOSFETs                                                            | 105        |

## Preface

HIS thesis is a summary of five-year work in Nanoelectronics Group (belonging to Division of Electromagnetics & Nanoelectronics since 2022) at Department of Electrical and Information Technology, Lund University. This work presents systematic investigation of III-V based vertical nanowire tunnel field-effect transistors, their circuit implementation and their self-heating investigation for low-power systems. The work was supervised by Professor Lars-Erik Wernersson, Dr. Lars Ohlsson Fhager and Dr. Johannes Svensson.

#### STRUCTURE OF THE THESIS

#### INTRODUCTION

The Introduction provides a broad and comprehensive view of the included publications and combines related work together. The Introduction is intended to be comprehensible for aspiring readers with a Master's degree in physics, electrical engineering or a related subject.

#### APPENDICES

#### A Fabrication Steps of Vertical Nanowire Tunnel Field-Effect Transistors

Appendix A provides detailed steps of vertical device fabrication included in this thesis.

#### PAPERS

The papers forming the main body of the thesis are reproduced in the back and listed in the following.

#### **INCLUDED PAPERS**

The following papers form the main body of this thesis and are appended in the back of the thesis.

- **Paper I:** <u>G. Rangasamy</u>, Z. Zhu, and L.-E. Wernersson, "High Current Density Vertical Nanowire TFETs with  $I_{60} > 1$   $\mu A/\mu m$ ", *IEEE Access*, vol. 11, pp. 95692–95696, 2023, doi: 0.1109/ACCESS.2023.3310253.

- ► I developed the process scheme, fabricated the device, did the characterization, and wrote the paper.

- Paper II: G. RANGASAMY, Z. ZHU, AND L.-E. WERNERSSON, "Impact of Source Positioning and Doping on Performance of Vertical III-V Nanowire Tunneling Field Effect Transistors", IEEE Transactions on Electron Devices, (Manuscript)

- ► I developed the process scheme, fabricated the device, did the characterization, and wrote the paper.

- Paper III: G. RANGASAMY, Z. ZHU, L.O. FHAGER, AND L.-E. WERNERSSON, "g<sub>m</sub>/I<sub>d</sub> Analysis of vertical nanowire III–V TFETs", *Electronics Letters*, vol. 59, no. 18, pp.e12954, Jul. 2023, doi: 10.1049/ell2.12954.

- ▶ I developed the process scheme, fabricated the device along with the circuits, did the characterization and circuit analysis and wrote the paper.

- Paper IV: G. RANGASAMY, Z. ZHU, L.O. FHAGER, AND L.-E. WERNERSSON, "TFET Circuit Configurations Operating below 60 mV/dec", IEEE Transactions on Nanotechnology, (Under Review)

- ► I developed the process scheme, fabricated the device along with the circuits, did the characterization and circuit analysis and wrote the paper.

- Paper V: G. RANGASAMY, M.S. RAM, L.O. FHAGER, AND L.-E. WERNERSSON, "Self-Heating in Gate-All-Around Vertical III-V InAs/InGaAs MOSFETs", *IEEE Electron Device Letters*, vol. 44, no. 7, pp. 1212–1215, Jul. 2023, doi: 10.1109/LED.2023.3273785.

- ▶ I developed the measurement scheme, did the characterization, self-heating analysis and wrote the paper.

## Acronyms and Symbols

Here, important acronyms, abbreviations, and symbols are listed, which are recurring throughout the thesis. Some parameters, which only occur in a narrow context, are intentionally omitted; some parameters are used in more than one way, but the context is always explicitly clarified in the corresponding text. Some (compound) units are provided with prefixes to reflect the most commonly encountered notations in the literature.

#### **ACRONYMS AND ABBREVIATIONS**

3D Three Dimensional

Al<sub>2</sub>O<sub>3</sub> Aluminium Oxide

ALD Atomic Layer Deposition

$\begin{array}{ccc} \textbf{Ar} & & \text{Argon} \\ \textbf{As} & & \text{Arsenic} \\ \textbf{AsH}_3 & & \text{Arsine} \\ \textbf{Au} & & \text{Gold} \end{array}$

**BEOL** Back-End-of-Line

BOE Buffered Oxide Etchant

BTBT Band-to-Band Tunneling

$C_4F_8$  Octafluorocyclobutane

CH<sub>3</sub>COOH Acetic acid

CMOS Complementary Metal-Oxide-Semiconductor

DC Direct Current

DEDigital EtchDEZnDiethylzincDIDeionized

**DIBL** Drain Induced Barrier Lowering

**DOS** Density Of States

EBL Electron-Beam Lithography

EOT Equivalent Oxide Thickness

FEOL Front-End-of-Line

FET Field-Effect Transistor

**Ga** Gallium

GAA Gate-All-Around

GaAs Gallium Arsenide

GaSb Gallium Antimonide

Ge Germanium

$egin{array}{ll} H & Hydrogen \\ H_2O & Water \end{array}$

$H_2SO_4$ Sulphuric acid $H_3PO_4$ Phosphoric acidHClHydrochloric acid

**Hf** Hafnium HfO<sub>2</sub> Hafnium dioxide Nitric acid

IC Integrated circuit

ICP Inductively Coupled Plasma

In Indium

InAs Indium Arsenide

InGaAs Indium Gallium Arsenide

InGaAsSb Indium Gallium Arsenide Antimonide

InPIndium PhosphideIoTInternet-of-ThingsIPAIsopropyl Alcohol

Mo Molybdenum

MoS<sub>2</sub> Molybdenum disulphide

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MOVPE Metal-Organic Vapor-Phase Epitaxy

N<sub>2</sub> Nitrogen

NaOH Sodium hydroxide

NDR Negative Differential Resistance

Ni Nickel

$\mathbf{O}_2$  Oxygen  $\mathbf{O}_3$  Ozone

PVCR Peak-to-Valley Current Ratio

RIE Reactive-Ion Etch

SEM Scanning Electron Microscopy

SF<sub>6</sub> Sulfur hexafluoride

SiGe Silicon Germanium

SiO Silicon monoxide

SiO<sub>2</sub> Silicon dioxide

Sn Tin

SS Subthreshold Swing

TASE Template Assisted Selective Epitaxy

TAT Trap Assisted Tunneling

TDMAHf Tetrakis(dimethylamido)hafnium(IV)

TEM Transmission Electron Microscopy

**TESn** Tetraethyltin

TFET Tunnel Field-Effect Transistor

Ti Titanium

TiN Titanium Nitride

TMAH Tetramethylammonium hydroxide

TMAl Trimethylaluminum

TMD Transition metal dichalcogenides

TMGa Trimethylgallium

TMIn Trimethylindium

TMSb Trimethylantimony

ULP Ultra Low Power

UV Ultraviolet

VLS Vapor Liquid Solid

W Tungsten

WKB Wentzel-Kramers-Brillouin

WZ Wurtzite

| XEDS | Energy-dispersive X-ray spectroscopy |

|------|--------------------------------------|

| XPS  | X-ray Photoelectron Spectroscopy     |

| XRD  | X-Ray Diffraction                    |

| ZB   | Zincblende                           |

| Zn   | Zinc                                 |

#### **LATIN SYMBOLS**

| $C_{\mathrm{ins}}$ | F                                | Insulator Capacitance                                       |

|--------------------|----------------------------------|-------------------------------------------------------------|

| $C_{\rm s}$        | F                                | Semiconductor Capacitance                                   |

| $E_{\mathbf{F}}$   | eV                               | Fermi Level Energy                                          |

| $E_{\mathbf{g}}$   | eV                               | Band Gap                                                    |

| $E_{\rm c,c}$      | eV                               | Channel Conduction Band Energy                              |

| $E_{ m v,s}$       | eV                               | Channel Valence Band Energy                                 |

| $E_{\mathrm{F,s}}$ | eV                               | Source Fermi Level Energy                                   |

| f                  | Hz                               | Frequency                                                   |

| <i>8</i> d         | S, $\mu$ S $\mu$ m <sup>-1</sup> | Output Conductance, often normalised by gate width          |

| g <sub>m</sub>     | S, $\mu$ S $\mu$ m <sup>-1</sup> | Transconductance, often normalised by gate width            |

| $I_{D}$            | A, $\mu$ A $\mu$ m <sup>-1</sup> | Drain Current, often normalised by the gate width           |

| $I_{\mathrm{DS}}$  | A, $\mu$ A $\mu$ m <sup>-1</sup> | Source-to-Drain Current, often normalised by the gate width |

| $I_{G}$            | A, $\mu$ A $\mu$ m <sup>-1</sup> | Gate Current, often normalised by the gate width            |

| $I_{S}$            | A, $\mu$ A $\mu$ m <sup>-1</sup> | Source Current, often normalised by the gate width          |

| $I_{\text{OFF}}$   | A, $\mu$ A $\mu$ m <sup>-1</sup> | Off-current, often normalised by the gate width             |

| $I_{ON}$           | A, $\mu$ A $\mu$ m <sup>-1</sup> | On-current, often normalised by the gate width              |

| $k_{\rm B}$       |       | $\approx 1.381 \times 10^{-23} \ \text{kg m}^2  \text{K}^{-1}  \text{s}^{-1}$ , Boltzmann Constant |

|-------------------|-------|----------------------------------------------------------------------------------------------------|

| $L_{G}$           | m     | Gate Length                                                                                        |

| $m_0$ $m^*$       | $m_0$ | $\approx 9.109 \times 10^{-31}$ kg, Electron Rest Mass Effective Mass                              |

| q                 |       | $\approx 1.602 \times 10^{-19}$ C, Elemental Charge                                                |

| $R_{on}$          | Ω     | Drain-to-Source Voltage                                                                            |

| T                 | K     | Temperature                                                                                        |

| $V_{ m DS}$       | V     | Drain-to-Source Voltage                                                                            |

| $V_{ m GD}$       | V     | Gate-to-Drain Voltage                                                                              |

| $V_{\mathbf{GS}}$ | V     | Gate-to-Source Voltage                                                                             |

| $V_{\mathrm{T}}$  | V     | Threshold Voltage                                                                                  |

| $V_{Th}$          | V     | Thermal Voltage                                                                                    |

#### **GREEK SYMBOLS**

$\alpha$  eV<sup>-1</sup> Non-Parabolicity Factor

$\varepsilon$  eV<sup>-1</sup> Electric field

$\kappa$  Dennard Scaling Factor, Relative Permittivity

#### **FUNCTIONS AND OPERATORS**

**ln(·)** Natural logarithm

$\log(\cdot)$  Logarithm to the base 10

$sin(\cdot)$  sine

## **INTRODUCTION**

## Introduction

Electronics applications permeate our lives and most human societies in countless ways. From smartphones to computers, from networks to databases, from AI to quantum computing, these inventions and their constant enhancements have enabled many possibilities. Transistors are the essential component of electronics, and their impact is so immense that they are the most widely manufactured human product ever. The transistor, a three-terminal device, which controls the flow of electrons between two electron reservoirs have been implemented in myriad of ways exploiting different physical phenomena and plethora of material systems. In this chapter, we provide look into one such transistor which works on quantum mechanical tunneling, the Tunnel Field-Effect Transistors (TFET). We discuss its operation, figures of merit, and provide a context and motivation for investigations taken in this thesis work.

#### 1.1 MOTIVATION FOR CONDUCTED RESEARCH

A transistor operates as a current regulator over several decades of magnitude by controlling a voltage between the terminals. This functionality has led to design and implementation of various kinds of transistors, which form the essential building block in most electronic systems. A daily example is the billions of transistors that make up every single processor in our computers, laptops, and smartphones. Transistors are also used in audio and wireless communication amplifiers, in power supply controllers or as sensors.

The rapid development of the metal-oxide-semiconductor field-effect transistor (MOSFET) since its invention in the 1950s has been driven mainly

by the continuous miniaturisation of the device dimensions and by the occasional introduction of a new material or a change in the device geometry. Feature sizes have now decreased to the thickness of only a few atomic layers, thereby, geometric scaling is facing fundamental physical limits. Since about the beginning of the 21st century, for further improvement of the device performance in terms of energy efficiency and speed, new materials, new architectures, have been the the focus of research efforts [1,2].

One of the challenges for future transistor design is the so-called "Boltzmann tyranny" that limits the scaling of the supply voltage as CMOS technology approaches its thermal and reliability limits [3]. The MOSFET works by using the gate electrode to change the potential barrier between the source and the channel, which controls the injection of charge carriers into the channel. However, the carriers follow Boltzmann statistics and there is a small fraction of high-energy carriers that can cross the barrier. This fraction increases with temperature T and makes the MOSFET operate at the thermionic limit of kT/q (where k is Boltzmann's constant and q is the charge of an electron). The gate voltage needs to change by at least 60 mV at room temperature to cause a tenfold change in source-to-drain current, and this sets a lower bound on the minimum threshold voltage of about 200 mV to keep the offstate leakage current low. The need for a minimum gate overdrive voltage of about 300 mV above the threshold voltage to provide enough on-state current sets the minimum operating voltage of the MOSFET at 500 mV. The inability to scale supply voltage below 500 mV will prevent CMOS technology from reaching low switching energies and sets a practical limit for hyperscaling. To overcome this, we need radical changes in the fundamental switching mechanisms of MOSFETs.

TFET devices are one approach to achieve subthermal switching while operating at low supply voltages. A TFET uses a reverse biased p-i-n interband tunnel junction instead of a conventional n-MOSFET, which is made of n-type sources and p-type channels. The subthreshold slope in such a device is not limited to 60 mV per decade. Here, the thermal tail of the electrons in the valence band of the p+ source is abruptly truncated by the band edge of the channel and can lead to steeper switching characteristics as the TFET is turned on. Operation of TFETs will be elaborated later in the chapter.

This thesis summarises detailed fabrication and characterisation work on III-V nanowire TFETs, in vertical device architectures, which employ both new materials with respect to the industry standard Si, and a new device architecture with respect to the conventional lateral device orientation, all while being compatible with existing Si fabrication technology. For TFETs to be competitive in low power domian, it's current levels has to be substantially improved.

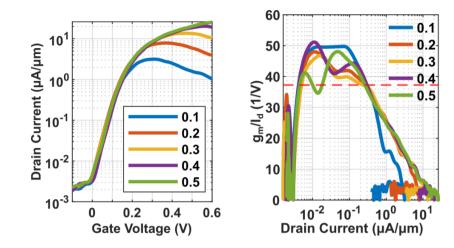

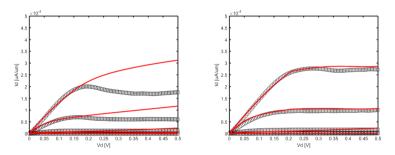

The first part of the thesis discusses the heterostrucuture engineering adopted to improve the device characteristics. A TFET can, in principle, operate with larger transconductance to current ratio than traditional field effect transistors in the sub-threshold region. In addition, the higher output resistance offered by TFET-based designs allows achieving significantly higher intrinsic voltage gain and higher maximum-oscillation frequency at low current levels. Moreover, TFET-based circuits exhibit superior performance advantages in trackand-hold circuits, ambient radio-frequency power scavenging and digital to analog converters [4–8]. All these findings indicate that the TFET based circuits has a good application prospect in the low-power domain. Despite these advantages, circuit design based on TFETs haven't been experimentally verified. This thesis work try to tackle this deficiency in research landscape as well. By adopting a vertical architecture, the gate length is decoupled from the footing area, which greatly improves the packing density. The improvement in packing density, affects the heat transport in the chip. The final section of the thesis studies the self-heating behaviour of vertical nanowires.

#### 1.2 TFET OPERATION

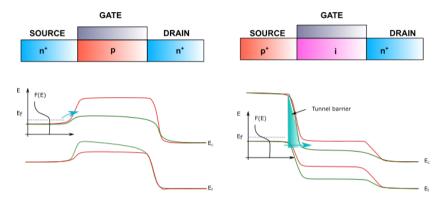

Before exploring the operation of TFETs, a brief introduction on MOSFET operation is warranted, so that we can compare and contrast their operating behaviour. Both transistors transport charges between the source and the drain terminals, with gate terminal modulating the amount of charge transfer albeit with a different operating principle. For easier analysis, we are going to consider only n-type for both devices. The schematic cross section and band diagram of both devices are shown in Fig. 1.1. Let's take the operating principle of MOSFETs. The doped n-type source and the drain terminals are reservoirs of charges. The p- type channel constitutes an energy barrier between these terminals. By applying a gate voltage, an electric field is created in the channel which modulates this energy barrier. As gate voltage increases, the barrier energy decreases, and electrons can surmount the lowered energy barrier and move from source to drain. To improve current levels, the drain-source voltage can be increased.

TFET, on the other hand, rely on band-to-band tunneling (BTBT) to transfer the charges between the terminals [9–11]. This is enabled by the device structure of the TFET, which consists of lightly doped p-type source, an intrinsic channel and a highly doped n-type drain, not unlike an p-i-n diode. Structurally, the TFET has asymmetric doping of the drain and source when compared to a conventional MOSFET. The corresponding band diagrams of an nTFET transitioning from the off- to the on-state are shown in Fig. 1.2b

**Figure 1.1:** The cross section and the band diagram at on- and off-state for a) a MOSFET and b) a TFET are shown.

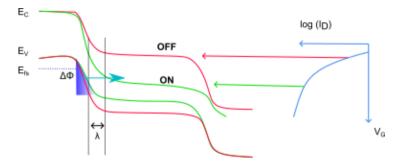

under positive  $V_{DS}$  bias. As in a backward diode, the interband overlap of the source and channel regions enables the conduction of carriers by means of band-to-band tunneling. However, in the off-state, the band gap in the channel acts as an energy filter, cutting off the availability of states for tunneling. As a consequence, I<sub>OFF</sub> in a TFET results ideally only from thermionic emission above a barrier approximately equal to the energy band gap,  $E_G$ . Other processes that contribute to the OFF-state leakage currents are associated with Shockley-Read-Hall (SRH) generation and trap-assisted tunneling (TAT). Referring again to Fig. 1.2b, if a positive gate voltage is applied, the bands in the channel move to lower energies reaching a crossing point where the conduction band in the channel begins to overlap with the valence band in the source. This corresponds to the onset of BTBT where electrons tunnel from the source valence band into the channel through a tunneling barrier. The tunneling probability is exponentially dependent on the tunneling distance. The BTBT generation processes can result either from direct transition between the maximum of the valence band and the minimum of the conduction band at the tunneling window or via a phonon-meditated indirect transition [6].

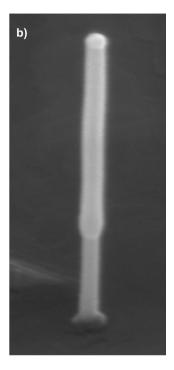

The gate voltage modulates both the tunneling probability and the availability of states to tunnel into, within a tunneling window given by the interband overlap. These two contributions allow for two different mechanisms for realizing SS steeper than 60 mV/dec. Unlike the MOSFET where the slope of the  $I_D$ – $V_{GS}$  transfer characteristic has a fixed swing in the subthreshold regime, the SS of a TFET is not constant but depends on  $V_{GS}$ . The key current defining the upper bound of this region is defined as sub-threshold current at SS = 60 mV/dec and is denoted by  $I_{60}$ . SS and  $I_{60}$  metrics form the basis of benchmarking TFETs in this work.

**Figure 1.2:** a) Energy band diagrams for off- and on-state for a TFET. Each band diagram variation corresponds to a specific point in the  $I_D$ – $V_{GS}$  characteristic indicated in b) the right panel.

#### 1.2.1 BAND-TO-BAND TUNNELING

In this section, a simple analytical theory is derived to lay out some general TFET design rules and to illustrate under what circumstances subthermal SS can be achieved. As illustrated in Fig. 1.2a, only carriers within the tunneling window can contribute to the transport. Using Landauer formalism [12], the drain current per unit width can be written as

$$I_{\rm D} = \frac{2q}{h} \int_{E_{\rm CCH}}^{E_{\rm VS}} T_{\rm BTBT}(E) \left[ f_{\rm S}(E) - f_{\rm D}(E) \right] dE, \tag{1.1}$$

where h is Planck's constant,  $f_S(E)$  and  $f_D(E)$  are the source and drain Fermi distribution functions, and  $T_{BTBT}(E)$  is the BTBT tunneling probability. The direct BTBT probability can be evaluated analytically by means of the Wentzel-Kramers- Brillouin (WKB) approximation,

$$T_{\text{BTBT}} = \exp\left(-2\int_{x_1}^{x_2} k_X(x, E) \, \mathrm{d}x\right),\tag{1.2}$$

where  $x_1$  and  $x_2$  are the classical turning points defining the tunneling path length and  $k_X$  is the imaginary wave vector obtained through the Kane two-band model [13]. Assuming a triangular potential barrier at the source/channel interface, i.e., constant electric field over the tunneling path, the transmission probability can be written as

$$T_{\text{BTBT}} = \exp\left(-\frac{4\Lambda\sqrt{2m^*}E_{\text{G}}^{3/2}}{3q\hbar\left(\Delta\phi + E_{\text{G}}\right)}\right). \tag{1.3}$$

In the above equation,  $\Lambda$  is the width of the transition region at the source/channel interface, i.e., the tunneling width, m\* is the reduced tun-

neling mass, h is the reduced Planck's constant, and  $E_G$  is the semiconductor energy gap. The tunneling width is given by the sum of the depletion width in the source,  $W_D$ , and the scaling length of the gated region,  $\lambda$ , i.e.,  $\Lambda = W_D + \lambda$  [14]. It is useful to relate the source depletion width and channel scaling lengths to the device parameters; we can approximate  $W_D$  with the Debye length in the source region

$$W_{\rm D} = \sqrt{\frac{\varepsilon_{\rm S} k_{\rm B} T}{q^2 N_{\rm D}}},$$

where  $\epsilon_s$  is the semiconductor permittivity and  $N_D$  is the doping in the source. The expression for the channel scaling length depends on the channel geometry. In the case of a vertical gate-all-around (GAA) nanowire structure assuming a non- parabolic expansion of the vertical potential distribution, and assuming a very thin nanowire channel, the natural length is given by

$$\lambda \approx \pi \frac{t_{ox} + r_{nw}}{2.4}$$

where  $r_{nw}$  is the nanowire radius and  $t_{ox}$  is the oxide thickness [15].

The BTBT current is determined by both the transmission probability and the occupation functions at the two sides of the tunnel junction within the tunneling window. If we assume a drain-source bias large enough to suppress any back injection from the drain to the source [16],

$$I_{D} \approx \frac{2q}{h} T_{BTBT} k_{B} T \left[ F_{0} \left( \frac{E_{FS} - E_{C,CH}}{k_{B}T} \right) - F_{0} \left( \frac{E_{FS} - E_{V,S}}{k_{B}T} \right) \right]$$

$$I_{D} = \frac{2q}{h} T_{BTBT} k_{B} T \ln \left[ \frac{1 + \exp\left( \frac{E_{FS} - E_{V,S} + \Delta \phi}{k_{B}T} \right)}{1 + \exp\left( \frac{E_{FS} - E_{V,S}}{k_{B}T} \right)} \right]$$

$$(1.4)$$

In the off-state, leakage contributions dominate TFET current. Eq. 1.3 indicates that narrow band gap materials are necessary to achieve BTBT transmission probability close to unity. When a narrow band gap material is employed,  $I_{ON}$  increases according to Eq. 1.2.1, but the thermionic current,  $I_{TH}$ , becomes significant as well.

$$I_{\text{TH}} = \frac{2q}{h} \int_{E_{\text{C,S}}}^{+\infty} f_{\text{S}}(E) dE$$

$$\approx \frac{2q}{h} k_{\text{B}} T \exp\left(-\frac{E_{\text{G}} + E_{\text{V,S}} - E_{\text{F,S}}}{k_{\text{B}} T}\right)$$

(1.5)

A TFET has two tunneling junctions, one at the source-channel interface and the other at the drain-channel interface. When an negative gate voltage is applied, the valence band of channel and conduction band at the drain opens up, leading to hole injection into the channel. This ambipolar behaviour is undesirable as it increases the off-state conduction, leading to higher power dissipation. In this work, the ambipolar behaviour is suppressed by reducing the drain doping at the expense of the channel resistance. A weaker gate control on the drain-side by introduction of field-plate is adopted as well [17,18]. The fabrication techniques used are discussed further in Chapter 2 while the effects of ambipolarity in circuit operation are discussed in Chapter 3.

For 1D TFETs, direct source-drain tunneling dominates the off-state leakage, especially for low  $E_G$  and small  $m^*$  materials. Trap-assisted tunneling is another important parasitic conduction mechanism often called into play to explain the deviations observed between simulated and measured TFET characteristics. A comprehensive study on affects of these leakages in TFET performance is shown in previous studies conducted in our group [19].

#### 1.2.2 NEGATIVE DIFFERENTIAL REGION

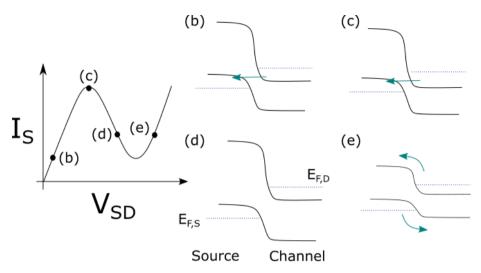

A common feature of TFETs is the negative differential resistance (NDR) that occurs when the source and drain are reversely biased ( $V_{SD} > 0$ ) in a common drain configuration (Fig. 1.3). This indicates the presence of a tunneling junction in the device, similar to what happens in Esaki diodes, which are p-n junctions with reverse bias [20,21]. The mechanism behind this phenomenon is explained in Fig. 1.3 b–e. As  $V_{SD}$  increases, the source band edges move downward and create a larger tunneling window. This results in a higher tunneling current until the source valence band aligns with the channel conduction band, reaching the peak current at  $V_{SD} = V_P$ .

If  $V_{SD}$  continues to increase, the tunneling path is blocked and the current drops (Fig. 1.3d), creating an NDR region (Fig. 1.3a). When the source bands are lowered enough that carriers can thermally overcome the energy barrier (Fig. 1.3 e), the current rises sharply again. Therefore, a typical TFET shows a peak and a valley in the current, and their ratio (PVCR) is used as a measure of the quality of the tunnel junction. However, not all TFETs exhibit NDR, and this depends on the design and material of the structure.

**Figure 1.3:** NDR I-V curve of a TFET at a fixed  $V_G$ .  $V_P$  is the corresponding voltage at the current peak and the peak-valley current ratio (PVCR) typically describes how strong the NDR effect is. (b)-(e) The corresponding changes in band diagram.

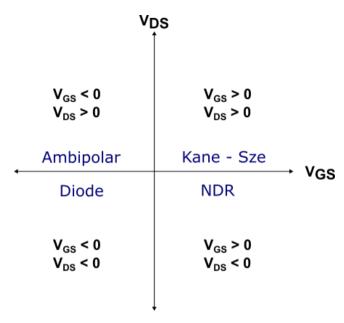

#### 1.2.3 TFET QUADRANTS OF OPERATION

Fig. 1.4 summaries the varies modes of operation of a TFET under different biasing conditions. Designing circuits with TFET is tricky as a slight variation in baising conditions, changes the device operation of the transistor. On the other hand, the versatility offered by TFETs finds application in various low-power systems. To explore this further, we look into voltage-mode and current-mode operations of TFET circuits in chapter 3.

#### 1.3 GEOMETRIES

In 1974, Dennard formulated that the transistor operating characteristics are preserved if all the transistor dimensions and supply voltage are scaled by the same factor [22]. This came to be known as Dennard's law and preserving constant power density became a guiding principle in scaling the transistor and associated interconnects. Reducing the area of the transistor reduces the necessary drive voltage and the capacitance thereby allowing circuits to operate at higher frequencies at the same power density. Beginning with the 65 nm node size, the supply voltage reduction became unfeasible due to non-scalability of the threshold voltage. The effects were further exasperated by the increasing leakage currents with scaling, with power supply voltage

Figure 1.4: The operation of n-type TFET based on the bias voltages applied.

saturating at 0.5 V. The power wall led to multicore scaling whereby the number of cores per die was increased to maintain the performance growth. The power constraints prevent all cores to be utilized simultaneously, leading to an interesting scenario where even though the number of transistors in a chip can be increased, in accordance with Moore's law, they cannot be fully utilized.

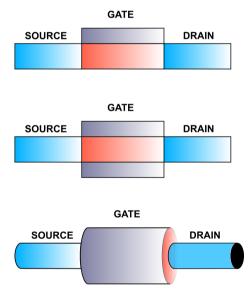

The transistor scaling though continued unabated thanks to the introduction of new channel materials like SiGe, strained-Si; high-k gate oxide, metal stack and new process development schemes such as self-aligned multi-patterning lithography techniques [23–27]. A different trend also emerged, known as More-than-Moore (MtM), where the focus is functional diversification of devices for niche applications in automotive, medical, communication, infotainment, security etc. Here, device architectures consisting of multi-gate architecture, 3D stacked nanosheets/ribbons with gate-all-around configuration in lateral devices to improve gate control on the channel are explored for reducing leakage. The gate control over the channel must be as efficient as possible. Initially, it was achieved by increasing the coupling of gate voltage with the channel potential by reducing the effective oxide thickness. Once the near defect free high-k material was utilized for gate oxide, further the enhancement of gate control over the channel can be attained by using

a double gate or gate all around configurations, rather than a single gate configuration [28–30]. The gate configurations are shown in the Fig. 1.5.

A transition from horizontal to vertical transport has also been suggested to reduce device footprint. Such vertical devices have recently been demonstrated by IBM, Zurich, CQEST, Japan, KAIST, South Korea, among others [30–32]. In this thesis work, we concentrate on such a vertical nanowire structure with gate-all-around geometry. Due to high current density and low cross-sectional area, the local temperature may be higher in a vertical transistor structure due the limited volume for heat dissipation from the nanowire into the substrate [44]. Furthermore, due to the confined geometry and larger surface-to-volume ratio, the phonon-boundary scattering in III-V vertical nanowire is expected to be more prominent than in FinFETs and we may expect increased thermal resistance. Chapter 4 studies the effect of self-heating on device performance.

**Figure 1.5:** (a) Single-gate (SG), (b) double-gate (DG), and (c) gate-allaround (GAA) geometries.

#### 1.4 MATERIALS AND DEVICE PERFORMANCE

Silicon has been the mainstay of semiconductor industry due to it's abundance, ease of forming insulating oxides and high density of state (DOS). The use of silicon in MOSFETs have worked remarkably well, even in MtM era. With regards to TFET though, they suffer from low on-currents. To improve

the current levels, materials with lower effective mass, narrower band-gap and shorter transition length is needed, as dictated by the tunneling probability equations. III-V semiconductors are one such class of direct band gap material that allows for band gap engineering and optimization of the junction to reach higher on- currents than what TFETs made of group IV are able to achieve. Table 1 shows the BTBT material parameters for Si, Ge and different III-V materials. Referring to Eq. 1.2, we prefer materials with narrower bandgap and  $\Lambda$ , i.e. higher values for parameters A and B.

Using III- V semiconductors, TFETs with homojunction or heterojunction (staggered or broken band-gap alignment) have been demonstrated. However, due to a higher number of defects in the bulk and at the interfaces, no device have demonstrated ability to operate well below the thermal limit while maintaining high subthermal current levels. Both, Ahn et. al. and Alain et. al. has fabricated planar InGaAs TFETs with homojunction, which were able to reach a minimum subthreshold swing of 57 and 54 mV/decade at  $V_{GS}$  = 0.1 V, respectively [33,34]. To improve the current further, usage of staggered heterojunction is necessary. So far the TFETs with staggered heterojunction have demonstrated the best combination of currents and subthreshold swing. Dewey et. al. used a undoped In<sub>0.7</sub>Ga<sub>0.3</sub>As pocket to form a staggered heterojunction in an InGaAs TFET, which resulted in three times higher current levels than comparable TFET with a homojunction [35]. Zhou et. al. demonstrated vertical TFETs with broken heterojunction implemented using InAs/GaSb. These devices reached 180  $\mu$ A/ $\mu$ m at  $V_{GS} = V_{DS} = 0.5$ V, with a minimum subthreshold swing of 200 mV/decade. Dit could be reduced by using forming gas annealing, which improved the minimum subthreshold swing to 150 mV/decade [36]. By using template-assisted growth, lateral InAs/GaSb nanowire TFETs with gate-all-around were demonstrated by Cutaia et. al [37]. nTFETs achieved an average subthreshold swing of 140 mV/decade and an on-current of 40  $\mu$ A/ $\mu$ m at  $V_{GS} = V_{DS} = 0.5$  V. The oncurrent and subthreshold swing of these devices were limited by the undoped source, which resulted in source depletion. Tomioka et. al. demonstrated vertical nanowire InAs/Si TFETs with minimum subthreshold swing of 21 mV/decade at  $V_{GS} = 1 \text{ V}$  and on-current of  $1 \mu A/\mu m$  at  $V_{GS} = V_{DS} = 1 \text{ V}$ . InAs nanowires, with a diameter of 30 nm, were in these devices grown on a Si-wafer utilizing template-assisted growth [38].

As these presented publications show, there are several challenges to overcome when designing TFETs based on group IV or III-V semiconductors. An abrupt tunneling junction is required both for composition and doping. The interface between III-Vs and high-k needs to exhibit a very low Dit to reduce defect assisted tunneling (DAT) [19,39]. Furthermore, an ultrathin geometry is needed for robust electrostatic control. TFETs based on

| Semiconductor                            | Eg(eV) | me( *mo) | $A(cm^{-3}s^{-1})$    | $B(cm^{-3}s^{-1})$   |

|------------------------------------------|--------|----------|-----------------------|----------------------|

| Si                                       | 1.12   | 0.2      | 4*10 <sup>14</sup>    | 19*10 <sup>6</sup>   |

| InAs                                     | 0.35   | 0.023    | 1.7*10 <sup>20</sup>  | 1.3*106              |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As | 0.74   | 0.043    | 1.6 *10 <sup>20</sup> | 5.6 *10 <sup>6</sup> |

| In <sub>0.73</sub> Ga <sub>0.27</sub> As | 0.77   | 0.045    | 1.7 *10 <sup>20</sup> | 6.3 *106             |

| GaAs <sub>0.5</sub> Sb <sub>0.5</sub>    | 1.34   | 0.08     | 1.6 *10 <sup>20</sup> | 18 *10 <sup>6</sup>  |

**Table 1.1:** BTBT parameters from Kane's formalism. Data is taken from [45, 46].

two-dimensional materials (2DMs) show some desirable properties, however these novel materials also require more material research and development to improve the currents [40–42]. In this work, we take established III-V materials as a base for improving the current levels in a TFET. A meticulous control of heterojunction is needed to improve the device performance, thereby III-V materials which offer extensive options on band-structure engineering are preferred. Furthermore, in Lund University, we have been able to make near-defect free heterostructures, which improves device off-state performance [43,44].

#### 1.5 METRICS FOR TRANSISTOR PERFORMANCE

In a transistor, the current is controlled using a gate, drain and source voltages. All data presented in this thesis is measured using common-source configuration, which means that the source is the common voltage reference for the gate and drain voltages. Thereby, the gate voltage is written as  $V_{GS}$  and drain to source voltage as  $V_{DS}$ . To make a proper characterization of the transistor there are a number of metrics that are used, and these will be described below.

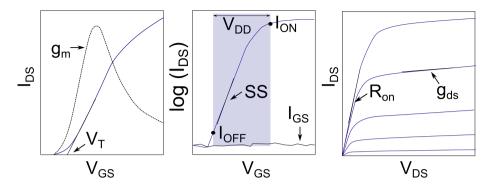

#### 1.5.1 DRIVE CURRENT

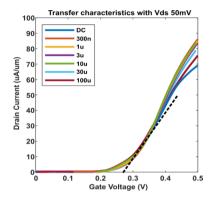

Transfer (linear and logarithmic) and output graphs are shown in Fig. 1.6 a, b and c, respectively. These two graphs describe the dependence of the current, that flows between the source and drain, on the gate and drain voltages. As the transistor switches from off- to on-state, the current will change its magnitude with several orders, thereby to study the off-characteristics the current in the transfer graph is plotted using a logarithmic scale, Fig. 1.6 b.

**Figure 1.6:** Electrical characteristics of a vertical InAs nanowire TFET (a) Transfer curves of a transistor in linear scale, where  $g_m$  is the transconductance and  $V_T$  is the threshold voltage. (b) Transfer curve in logaramithic scale, indicating on- and off-currents, gate current and subthreshold swing and (c) Output characteristics, where  $g_{ds}$  is the output conductance and  $R_{on}$  is on-resistance.

Using these graphs, metrics that are important for transistors performance can be determined. For the digital circuits, the ratio between the off- and on-current is of importance, thus it is important to clearly see the difference between the zero and one state. In general, when discussing currents for digital applications, usage of  $I_{OFF}$  and  $I_{ON}$  is common.  $I_{ON}$  is usually determined with reference to  $I_{OFF}$ , in this work  $I_{OFF}$  is always taken as 1 nA/ $\mu$ m. The currents are normalized to diameter of InAs drain, which is between 20-22 nm, depending on the specific device.

#### 1.5.2 TRANSCONDUCTANCE

From the transfer curve, the transconductance  $(g_m)$  can be extracted. Definition of the transconductance is partial derivative of the drain current with respect to the gate voltage.

$$g_{\rm m} = \partial I_{\rm D}/\partial V_{\rm G}$$

This metric describes how effective a transistor amplifies a small voltage on the gate, which is an important metric for analog applications where the transistor is used to amplify signals. However, also in digital circuits high  $g_m$  is beneficial, as a high  $g_m$  and low subthreshold swing allows for large on-current.

#### 1.5.3 OUTPUT CONDUCTANCE

The dependence of the output current on a change of the drive voltage ( $V_{DS}$ ) is described by output conductance, defined as

$$g_{\rm ds} = \partial I_{\rm D}/\partial V_{\rm DS}$$

.

The output conductance ( $g_{ds}$ ) is extracted in the saturated region of the output graph as shown in Fig. 1.6 c. Preferably this value should be as low a possible to ensure linearity and a good gain when the transistors are used as amplifiers. For an ideal MOSFET, the value is zero. However, in real devices drain-induced-barrier lowering (DIBL) and channel length modulation will increase the output conductance.

#### 1.5.4 THRESHOLD VOLTAGE

The threshold voltage  $(V_T)$  is used as a reference point when the transistor switches between its off- and on-state. The threshold voltage of a device is in one definition extracted by fitting a line to the point at  $g_{m,max}$  and extrapolating the line down to the x-axis as shown in Fig. 1.6 a. Depending if the  $V_T$  is positive or negative the transistor is said to be an enhancement or depletion mode device, respectively. If the gate voltage is zero, a depletion mode device is in the on-state and a enhancement mode device is in the off-state. Enhancement mode transistors are important for both digital and analog circuits so that the transistor is turned off when no gate is applied. This ensures that the static power consumption is minimal.

#### 1.5.5 SUBTHRESHOLD SLOPE

The subthreshold slope is a partial derivative of the drain current on a logarithmic scale with respect to the gate voltage in the subthreshold region of the transistor. In the literature, the numbers that are provided for this metric represents the inverse subthreshold slope which is also referred to as subthreshold swing [10].

$$\mathrm{SS} = \frac{\partial V_{\mathrm{G}}}{\partial log(I_{\mathrm{D}})} = \ln(10) \frac{k_{\mathrm{B}}T}{q} (1 + \frac{C_{\mathrm{dep}}}{C_{\mathrm{ox}}}) \geq \ln(10) \frac{k_{\mathrm{B}}T}{q} \approx 60\,\mathrm{mV/dec}\,(300\,\mathrm{K})$$

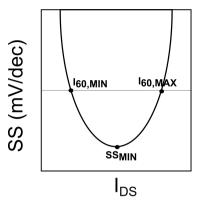

#### 1.5.6 I<sub>60</sub>

For TFETs to compliment MOSFETs at low power applications, SS must be maintained below 60 for several decades of current levels. Furthermore, the highest current level where the subthreshold characteristics exhibit a transition from sub- to super-60 mV/decade behavior should be greater than

1  $\mu$ A/ $\mu$ m. To quantify these current levels under 60 mV/dec, we use  $I_{60,min}$  and  $I_{60,max}$  as defined in Fig. 1.7.

**Figure 1.7:** Subthreshold swing vs drain current, showing the definition of minimum SS,  $I_{60,min}$  and  $I_{60,max}$ .

# TFET Fabrication and Heterostructure engineering

In chapter 1, we discussed the superior TFET performance offered by III-V material with respect to group IV elements. This is achieved in part due to near defect free growth of the III-V nanowire, along with optimal band strucuture engineering. In this chapter, we elaborate on the nanowire growth, TFET fabrication process, and the optimization of heterostructure to improve the device performance.

#### 2.1 NANOWIRE GROWTH

There are two favoured approaches for the growth of semiconductor nanowires; top-down or bottom-up processing. In the top-down approach, thin-films of the desired structure are grown on the wafer and then are selective etched to provide the desired nanowire. In the bottom-up approach, seed-particles are used to catalyze the growth in desired region [47]. Nanowires of both group IV and III-V materials have been grown using this method, including Si, Ge, InAs, InP, GaAs, GaSb, InGaAs, etc [48–50].

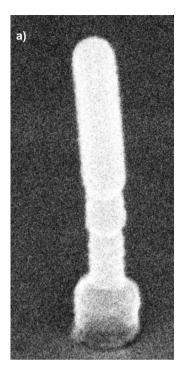

In the bottom-up method, gas-phase precursors of the desired material composition and are used to grow the nanowire in the presence of nanoparticle catalyst. In this work, a bottom-up method is used with Au-seed as catalysts that are positioned on an InAs layer on top of a Si-wafer. The use of Si wafers make it compatible with existing processing techniques and an simple way to integrate III-V materials in Si. Nanoparticle dimensions of the catalyst particle which is the basis for the growth are defined with EBL. The size of the particles is determined by the electron dose, the resist thickness, and the thickness of the evaporated metal layer.

This process allows for simple scaling of the numbers of nanowires in every device. The growth of the nanowires is performed using metalorganic vapor phase epitaxy (MOVPE). Group III-precursors (TMGa, TMIn) and group V-precursors (TMSb, AsH<sub>3</sub>) are used as source materials. In theory, the composition and crystal structure of the nanowires are controlled by the growth temperature, and the amount of and ratio between the precursors in the chamber. However, this picture is more complicated in reality since the ratio that matters is the ratio between the precursors in the direct proximity of the seed particles. This ratio is influenced by the surface of the sample and the distance between the seed particles as they are competing against each other for the material. The growth direction for the nanowires is <111>, with the crystal structure being either zincblende (ZB) or wurtzite (WZ). It should be mentioned that the crystal structure a material exhibits in bulk is not necessarily the same within the nanowires grown with the bottom-up method. InAs have ZB in bulk, but for certain growth conditions it could be WZ. Furthermore, some of the regions of the nanowires need to be doped to reduce resistance and suppress ambipolarity and related properties. These dopants are introduced during the growth using TESn for n-doping and DEZn for p-doping. Adding these materials can further complicate the growth and influence the morphology of the nanowires [51,52].

#### 2.2 FABRICATION PROCESS OF VERTICAL NANOWIRE TRANSISTORS

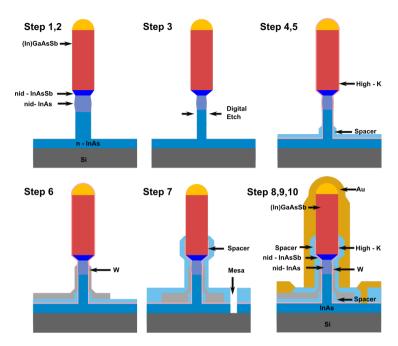

TFET devices in this work were fabricated by the steps described in this section. For interested readers there is a more detailed description in Appendix A.

- 1. **Digital etching**: A method to reduce the size of InAs nanowires is to oxidize them with ozone and then remove the oxide layer with citric acid. This is called digital etch. The procedure is repeated until the InAs nanowires reach the desired diameter. The GaSb shell that forms during the synthesis is also eliminated.

- 2. **High-k**: After the digital etch step, the nanowire is covered in a trilayer high-k dielectric consisting of of 1 nm Al<sub>2</sub>O<sub>3</sub>/ 3 nm HfO<sub>2</sub>/ 30 nm Al<sub>2</sub>O<sub>3</sub>. High-k are deposited using atomic layer deposition (ALD) at temperatures of 300 °C, 120 °C, and 100 °C, respectively. Prior to the start of the deposition of the Al<sub>2</sub>O<sub>3</sub>, a couple of Al pulses are used to clean the surface thereby improving the interface between the high-k and III-V material.

- 3. **Bottom-spacer**: A number of different materials (S1800 photo-resist, Silicon oxide (SiOx) and bilayer-stack of HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> with effective

- oxide thickness of 1 nm have been used to form the bottom-spacer for the transistors in this work.

- 4. **InAs-mesa**: A mesa formation step was introduced to etch away the first spacer with HF (1:400) and the underlying InAs (H<sub>3</sub>PO<sub>4</sub>) to isolate the individual nanowires.

- 5. **Gate**: A 30-nm-thick tungsten (W) film was sputtered on the nanowires. The physical gate-length was set by spin-coating the sample with organic photo-resist (S1800) which covers the nanowires completely. Using Oxygen plasma, the thickness of the resist was reduced to the desired gate length. Using reactive ion etching (RIE), the tungsten was removed from the exposed surfaces with a SF<sub>6</sub> in Argon atmosphere.

- 6. **Top-spacer**: The top-spacer for all transistors fabricated in this work is produced using 10 nm Al<sub>2</sub>O<sub>3</sub>. This differs from the previous generation TFETs produced in the group where organic spacers were preferred. An inorganic spacer was preferred to make it suitable to circuit design and more temperature resilient.

- 7. **Via-holes**: Using S1800 and UV-lithography the via holes are defined. The holes through the spacers are made using reactive etching and wet etching.

- 8. **Removing of the high-k**: The high-k on the top of the nanowire and in the drain via-hole is removed with HF(1:400).

- 9. **Top-metal and contact-pads**: The top-metal is made of Ni and Au, applied by either sputtering or evaporation. S1813 and UV-lithography is used to mask areas where the pads would be. The metal film in uncovered areas is removed using wet-etching.

- 10. To facilitate circuit design, contacts between TFETs are made using UV-lithography connecting individual transistors in the front-end-of-line (FEOL).

#### 2.2.1 CURRENT STATUS OF TFETS

Esaki diodes form the basis for TFETs, as covered in Chapter 1. In 2004, Appenzeller et al., demonstrated the sub-thermal switching of dual gated carbon nanotube FET by tunneling, the potential use of TFET for beyond CMOS began being extensively explored. Si TFET was the first choice for research due to its compatibility with the current fabrication process and the established high-quality interface to high-k gate oxides. But the large and indirect bandgap of Si reduced the tunneling efficiency resulting in insufficient performance. Strained Si and SiGe have been explored to achieve narrow bandgap and direct tunneling [53].

Figure 2.1: The processing steps involved in the fabrication of TFETs.

Knoch et al., provided the first insights into improving the performance by using a type-II near-broken band lineup. III-V semiconductors with a wealth of high carrier mobility materials allowing band gap engineering was found to be an appealing candidate for TFETs. Initial implementations of III-V TFETs were on III-V substrates since the large lattice mismatch to Si substrate would lead to high defect density. Seabaugh et al., studied planar InAs/AlGaSb, InAs/InP and InAs/GaSb airbridge TFETs with gate both in-line and normal to the tunneling direction. Contact and access resistances were seen to limit the performance and was circumvented using forming gas anneal (FGA) and SiNx passivation [54]. Datta et al., explored InGaAs TFET as homojunctions, highly doped pocket at the junction and InGaAs/GaAsSb heterojunction and found that tuning the Sb:As ratio of the source helps vary the band offset and hence the tunnel barrier width. Pulsed I-V measurements that mitigate the effects of interface traps on the transistor characteristics and the first report of RF characterization of TFET was demonstrated [55].

Zhao et al., improved the dry etching process for a top-down fabricated NW and demonstrated the first fully vertical III-V TFET with S=79~mV/dec. Improving the spacer technology helped reduce the S further down to 53 mV/dec. Alian et al., reported InGaAs/GaAsSb vertical NW TFET with S=

47 mV/dec and  $I_{ON} = 0.7 \mu\text{A/}\mu\text{m}$ . Development of EOT scaling process and analysis of defects helped in the realization of the steep switching devices.

Moselund et al., were among the first few to integrate III-V TFETs on Si substrate by utilizing template-assisted selective area growth of NW. InAs/Si p-TFET achieving S = 70 mV/dec and  $I_{ON}$  = 4  $\mu$ A/ $\mu$ m at  $V_{DS}$  = -0.5 V had been presented [56].

Heterojunction engineering to achieve balanced on- and off-state performance led to previous works of TFET with S = 48 mV/dec and  $I_{ON}$  = 10  $\mu A/\mu m$  for  $I_{OFF}$  = 1 nA/mm at  $V_{DS}$  = 0.3 V. For a TFET to be competitive with MOSFET, the  $I_{60}$  and  $I_{ON}$  must ideally be 1-10  $\mu A/\mu m$  and 10-100  $\mu A/\mu m$  while meeting the  $I_{OFF}$  requirements for the specific applications. For circuit design, the nuance is set on improving sub-threshold current levels. To compete with MOSFETs at low power applications, the  $I_{60}$  should be greater than 1mA/mm at  $V_{GS}$  of 100 mV.

#### 2.3 IMPROVING THE CURRENT LEVELS

Heterostructure TFETs are sensitive to epitaxy as BTBT is spatially confined within a very short distance across the tunnel junction. Thus, a slight modification at the heterojunction can substantially change the performance. In this section, we look into two aspects; the position of source dopant and the source dopant concentration, and understand their effects on TFET current levels. As described in Chapter 1, I<sub>60</sub> and SS would be the key parameters to benchmark the device performance.

#### 2.3.1 HETEROSTRUCTURE ENGINEERING

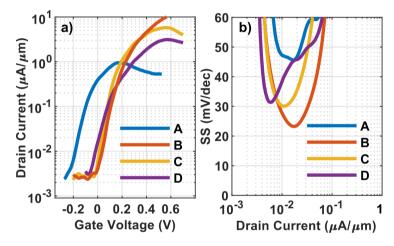

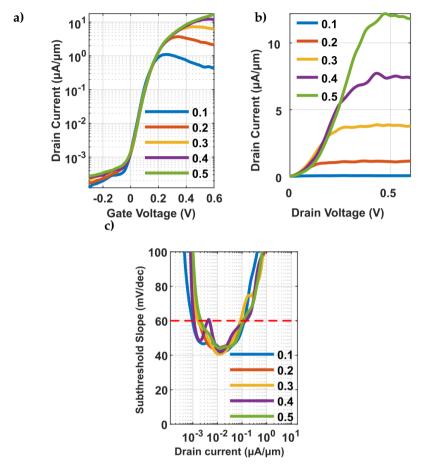

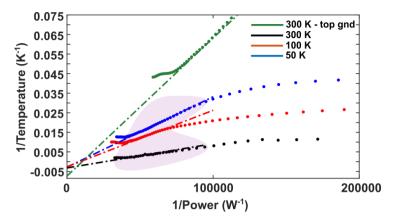

Band alignment at the tunnel junction can be varied by changing the composition of the source segment [57,58]. In paper II, one such variation analysis is performed. A systematic evaluation of delaying the introduction of Ga (TMGa) and Zn dopant (DEZn) into the source segment is performed to study the inflence in SS and  $I_{60}$ . Four different sample, A-D was evaluated in the series, based on the introduction time variation (Table 2.1). Fig. 2.2 shows the transfer characteristics and subthreshold swing (SS) of representative devices for samples A-D at  $V_{DS}$  of 500 mV. The compositional variation due to delay in DEZn introduction shifts the valence and conduction band to lower energies, leading to a decrease the effective tunnel barrier. This changes the heterojunction from staggered to near broken, thereby improving current levels. Delaying TMGa seems to have no effect on device properties.

The main optimization in growth which led to improvement in device parameters was to delay the introduction Zn dopant into the source segment.

**Table 2.1:** Sample list used to evaluate the nanowire source growth. TMSb is introduced first, followed by TMGa and DeZn; delayed by the time(s) mentioned in the table.

| Sample | TnSb | TMGa delay (s) | DeZn delay (s) |

|--------|------|----------------|----------------|

| A      | 0    | 5              | 5              |

| В      | 0    | 8              | 8              |

| С      | 0    | 10             | 8              |

| D      | 0    | 5              | 0              |

**Figure 2.2:** (a) Measured transfer characteristics of representative devices from A-D for  $V_{DS}$  of 0.3 V and (b) respective subthreshold swing vs drain current. The lowest slope is 26 mV/dec for sample B.

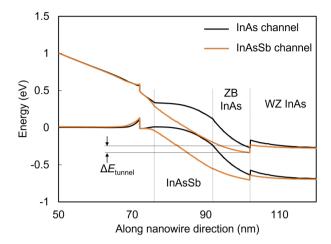

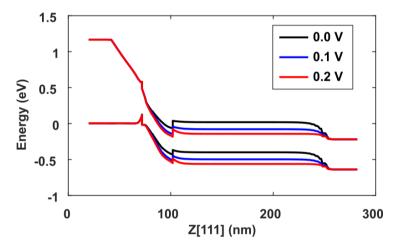

It results in a longer unintentionally doped InAsSb segment which has a narrower bandgap than InAs. Due to the doping delay, the majority of the tunneling occurs at the p-(In)GaAsSb/nid-InAsSb interface, leading to a larger energy window for tunneling compared to that of InAs channel according to the band diagram in Fig. 2.3. Combined with that the carrier effective mass in InAsSb is smaller than that in InAs, the tunneling current thereby would increase, resulting in a higher  $I_{ON}$ .

#### 2.3.2 DOPANT LEVELS

Even though the TFETs device parameters were improved by optimization of dopant positioning in the source, the goal of  $I_{60} > 1 \mu A/\mu m$  was not achieved.

**Figure 2.3:** Band diagram simulation of heterojunction TFETs with InAsSb channel compared to InAs channel.  $\Delta E_{tunnel}$  indicates a larger energy window for tunneling in the case of InAsSb channel.

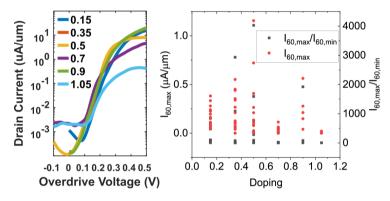

One way to improve the performance further is by optimization of dopant levels in the source [59–62]. A careful study in variation of doping level was conducted in paper I and II. High levels of doping will lead to introduction of states in the bandgap which increases subthreshold swing. These states affect the valence band-edge of the source and reduce the filtering efficiency of carriers in the Fermi-tail. Furthermore, high doping can lead to degeneracy, which diminishes filtering of charge carriers at the junction. Additionally, these bandgap states can cause more leakage paths that degrade the off-state when the channel has very few charges. On the other hand, too low source doping can result in source depletion, which affects the on-performance of the devices by increasing tunneling length and barrier height. Furthermore, a low source doping level will increase resistive loss and lower the current. Thereby, a detailed analysis of TFET device parameters is conducted by varying the source doping levels.

Among the devices, sample B and C exhibit the highest on-current, as discussed above. Device C exhibits a negative threshold voltage while device B, exhibits a positive threshold voltage. To minimise the static power dissipation, an enhancement mode device is preferred. Thereby, to optimize the device performance further by optimizing the source doping level, sample B was chosen as the best candidate. Choosing sample B as baseline, Zn dopant level concentration was varied from  $0.5 \times 10^{19}$  cm<sup>-3</sup> to  $3 \times 10^{19}$  cm<sup>-3</sup> with steps of  $0.5 \times 10^{19}$  cm<sup>-3</sup>, producing six samples E to J.

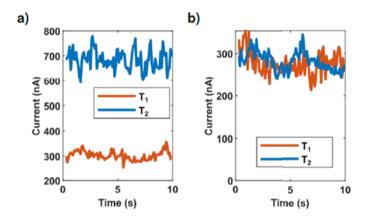

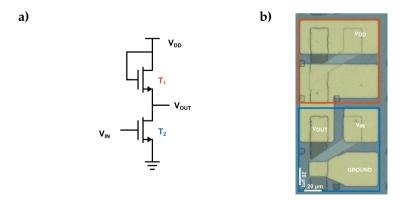

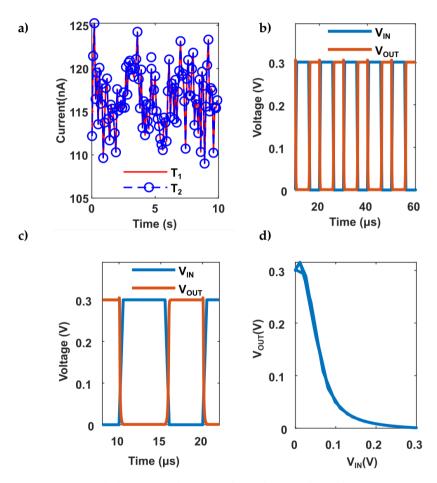

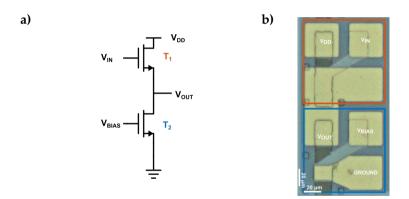

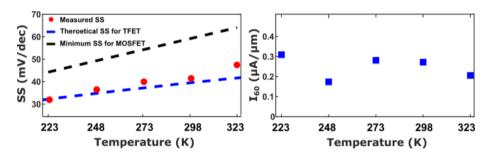

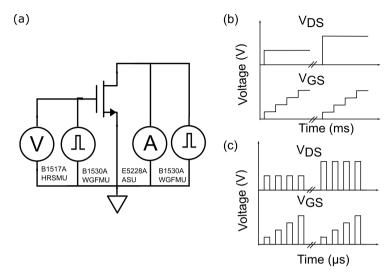

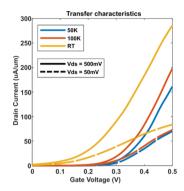

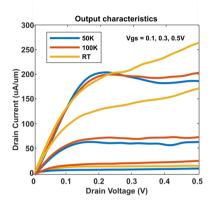

Fig. 2.5 (a) shows the transfer characteristics and  $I_{60}$  statistics of TFETs for samples E-J at  $V_{DS}$  of 500 mV. Lower doping causes source depletion and increases the barrier height and tunnelling distance. This leads to lower current. High doping gives rise to source degeneracy and softens the TFET turn on characteristics.