# LUND UNIVERSITY

### Baseband Processing for 5G and Beyond: Algorithms, VLSI Architectures, and Codesign

Mahdavi, Mojtaba

2021

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

Mahdavi, M. (2021). Baseband Processing for 5G and Beyond: Algorithms, VLSI Architectures, and Co-design. [Doctoral Thesis (compilation), Department of Electrical and Information Technology]. Dpt. of Electrical and Information Technology, Lund University, Sweden.

Total number of authors: 1

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

### Baseband Processing for 5G and Beyond: Algorithms, VLSI Architectures, and Co-design

Mojtaba Mahdavi

LUND UNIVERSITY

Doctoral Thesis Electrical Engineering Lund, March 2021 Mojtaba Mahdavi Department of Electrical and Information Technology Lund University P.O. Box 118 SE-221 00 LUND SWEDEN

Series of licentiate and doctoral theses ISSN 1654-790X; No. 140 ISBN 978-91-7895-960-0 (print) ISBN 978-91-7895-959-4 (pdf)

© Mojtaba Mahdavi, 2021 Produced using IAT<sub>E</sub>X Documentation System. Printed in Sweden by *Tryckeriet i E-huset*, Lund University, Lund. March 2021

No part of this thesis may be reproduced or transmitted in any form or by any means, electronically or mechanical, including photocopy, recording, or any information storage and retrieval system, without written permission from the author.

### Abstract

In recent years the number of connected devices and the demand for high data-rates have been significantly increased. This enormous growth is more pronounced by the introduction of the Internet of things (IoT) in which several devices are interconnected to exchange data for various applications like smart homes and smart cities. Moreover, new applications such as eHealth, autonomous vehicles, and connected ambulances set new demands on the reliability, latency, and data-rate of wireless communication systems, pushing forward technology developments. Massive multiple-input multiple-output (MIMO) is a technology, which is employed in the 5G standard, offering the benefits to fulfill these requirements. In massive MIMO systems, base station (BS) is equipped with a very large number of antennas, serving several users equipments (UEs) simultaneously in the same time and frequency resource. The high spatial multiplexing in massive MIMO systems, improves the data rate, energy and spectral efficiencies as well as the link reliability of wireless communication systems. The link reliability can be further improved by employing channel coding technique. Spatially coupled serially concatenated codes (SC-SCCs) are promising channel coding schemes, which can meet the high-reliability demands of wireless communication systems beyond 5G (B5G). Given the close-to-capacity error correction performance and the potential to implement a high-throughput decoder, this class of code can be a good candidate for wireless systems B5G.

In order to achieve the above-mentioned advantages, sophisticated algorithms are required, which impose challenges on the baseband signal processing. In case of massive MIMO systems, the processing is much more computationally intensive and the size of required memory to store channel data is increased significantly compared to conventional MIMO systems, which are due to the large size of the channel state information (CSI) matrix. In addition to the high computational complexity, meeting latency requirements is also crucial. Similarly, the decoding-performance gain of SC-SCCs also do come at the expense of increased implementation complexity. Moreover, selecting the proper choice of design parameters, decoding algorithm, and architecture will be challenging, since spatial coupling provides new degrees of freedom in code design, and therefore the design space becomes huge. The focus of this thesis is to perform co-optimization in different design levels to address the aforementioned challenges/requirements. To this end, we employ system-level characteristics to develop efficient algorithms and architectures for the following functional blocks of digital baseband processing.

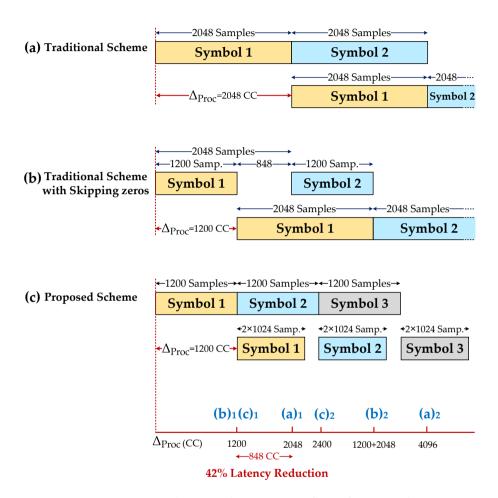

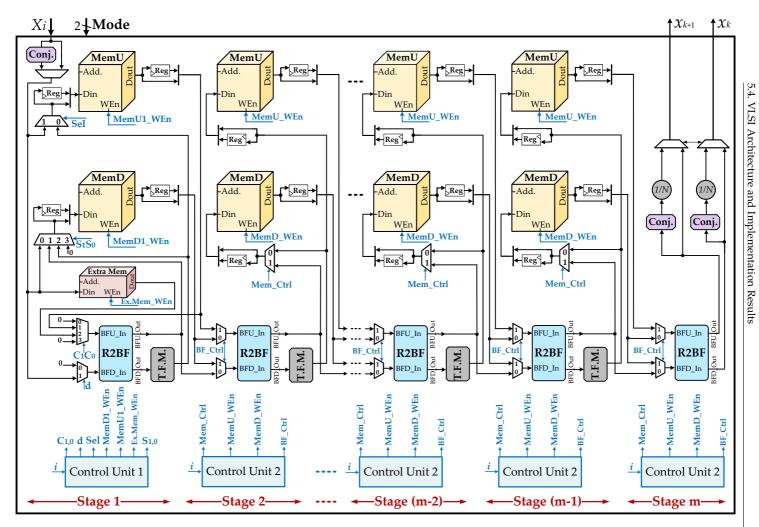

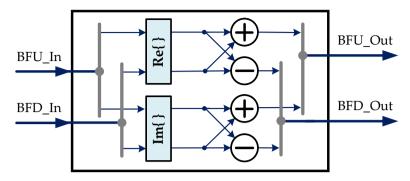

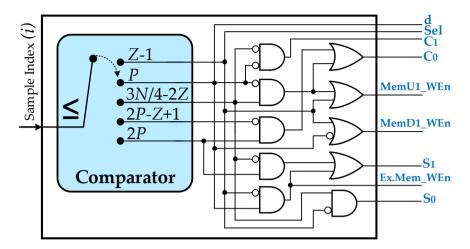

First, we present a fast Fourier transform (FFT), an inverse FFT (IFFT), and corresponding reordering scheme, which can significantly reduce the latency of orthogonal frequency-division multiplexing (OFDM) demodulation and modulation as well as the size of reordering memory. The corresponding VLSI architectures along with the application specific integrated circuit (ASIC) implementation results in a 28 nm CMOS technology are introduced. In case of a 2048-point FFT/IFFT, the proposed design leads to 42% reduction in the latency and size of reordering memory.

Second, we propose a low-complexity massive MIMO detection scheme. The key idea is to exploit channel sparsity to reduce the size of CSI matrix and eventually perform linear detection followed by a non-linear post-processing in angular domain using the compressed CSI matrix. The VLSI architecture for a massive MIMO with 128 BS antennas and 16 UEs along with the synthesis results in a 28 nm technology are presented. As a result, the proposed scheme reduces the complexity and required memory by 35%–73% compared to traditional detectors while it has better detection performance.

Finally, we perform a comprehensive design space exploration for the SC-SCCs to investigate the effect of different design parameters on decoding performance, latency, complexity, and hardware cost. Then, we develop different decoding algorithms for the SC-SCCs and discuss the associated decoding performance and complexity. Also, several high-level VLSI architectures along with the corresponding synthesis results in a 12 nm process are presented, and various design tradeoffs are provided for these decoding schemes.

To my wife, Marzieh

## Contents

| Ał  | ostra | ct                                          | iii  |

|-----|-------|---------------------------------------------|------|

| Pr  | eface | 2                                           | xi   |

| Ac  | knov  | wledgments                                  | xv   |

| Ac  | rony  | yms y                                       | cvii |

| M   | athe  | matical Notations                           | xxi  |

| Lis | st of | Figures x                                   | xiii |

| Lis | st of | Tables xx                                   | vii  |

| 1   | Intr  | oduction                                    | 1    |

|     | 1.1   | Scope of the Thesis                         | 2    |

|     | 1.2   | Thesis Outline and Contributions            | 3    |

| 2   | Dig   | ital Baseband Processing                    | 9    |

|     | 2.1   | Wireless Communication Systems              | 11   |

|     | 2.2   | OFDM-Based Multi-User Massive MIMO Systems  | 19   |

|     | 2.3   | Baseband Processing in Massive MIMO Systems | 20   |

| 3   | Sys   | tem, Algorithm, and VLSI Co-Design          | 25   |

|     | 3.1   | Performance Metrics and Design Parameters   | 25   |

|     | 3.2   | Cross-Level Optimization                    | 28   |

| I  | FF   | T/IFFT Processor for Massive MIMO Systems                   | 29  |

|----|------|-------------------------------------------------------------|-----|

| 4  | FFT  | /IFFT in Massive MIMO System                                | 33  |

|    | 4.1  | Fast Fourier Transform                                      | 33  |

|    | 4.2  | Latency Analysis                                            | 36  |

| 5  | Low  | -Latency FFT/IFFT                                           | 41  |

|    | 5.1  | Exploring OFDM Guard Bands                                  | 41  |

|    | 5.2  | Low-Latency IFFT Scheme                                     | 46  |

|    | 5.3  | Latency Comparison                                          | 50  |

|    | 5.4  | VLSI Architecture and Implementation Results                | 52  |

| 6  | Reo  | rdering Scheme                                              | 63  |

|    | 6.1  | Reordering Mechanism                                        | 64  |

|    | 6.2  | VLSI Architecture and Implementation Results                | 68  |

| II | Ма   | ssive MIMO Detection                                        | 73  |

| 7  | Upl  | ink Processing in Massive MIMO                              | 79  |

|    | 7.1  | Uplink System Model                                         | 79  |

|    | 7.2  | Antenna-Domain Detection                                    | 80  |

|    | 7.3  | Massive MIMO Channel                                        | 81  |

| 8  | Ang  | ular-Domain Massive MIMO Detection                          | 85  |

|    | 8.1  | Domain Transformation and Compression                       | 87  |

|    | 8.2  | Angular-Domain Linear Detection                             | 88  |

|    | 8.3  | Angular-Domain Non-Linear Detection                         | 89  |

| 9  | Des  | ign Evaluation and Tradeoffs                                | 95  |

|    | 9.1  | Performance Evaluation                                      | 95  |

|    | 9.2  | Analysis of Complexity and Memory Requirement               | 103 |

|    | 9.3  | Design Tradeoffs                                            | 106 |

| 10 |      | dware Realization of Angular- Domain Massive MIMO<br>ection | 111 |

|    | 10.1 | VLSI Architecture                                           | 111 |

|    | 10.2 | Implementation Results                                      | 120 |

| III Spatially Coupled Serially Concatenated Codes          | 125 |

|------------------------------------------------------------|-----|

| 11 Turbo-like Codes                                        | 129 |

| 11.1 Serially Concatenated Code (SCC)                      | 131 |

| 11.2 Spatially Coupled Serially Concatenated Code (SC-SCC) | 134 |

| 11.3 Design Space Exploration                              | 136 |

| 12 Decoding Algorithms                                     | 139 |

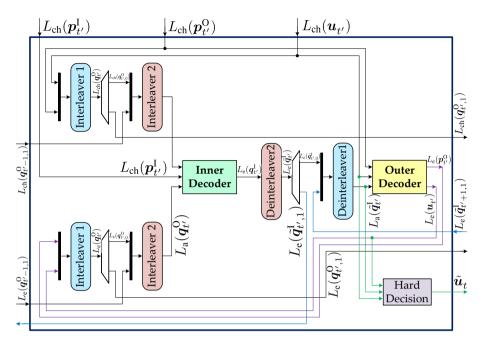

| 12.1 SCC Decoder                                           | 139 |

| 12.2 Block-Wise SC-SCC Decoder                             | 141 |

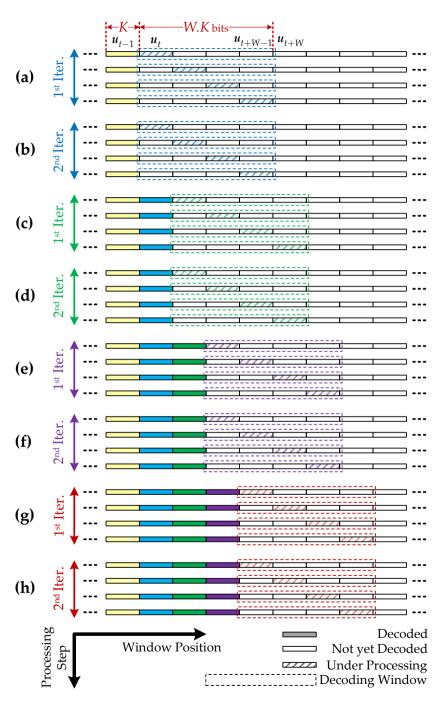

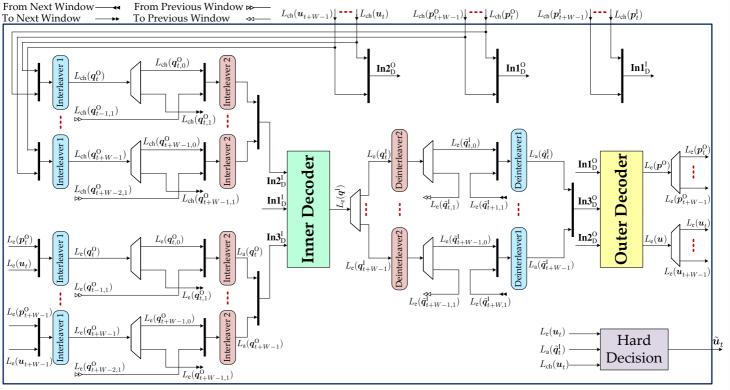

| 12.3 Window-Wise SC-SCC Decoder                            | 146 |

| 13 Performance and Complexity Evaluation                   | 151 |

| 13.1 Computational Complexity Analysis                     | 151 |

| 13.2 Performance Evaluation                                | 156 |

| 14 Decoder Architectures and Implementation Results        | 169 |

| 14.1 VLSI Architectures for Inner and Outer Decoders       | 169 |

| 14.2 Decoder Architectures                                 | 174 |

| 14.3 Results and Discussion                                | 180 |

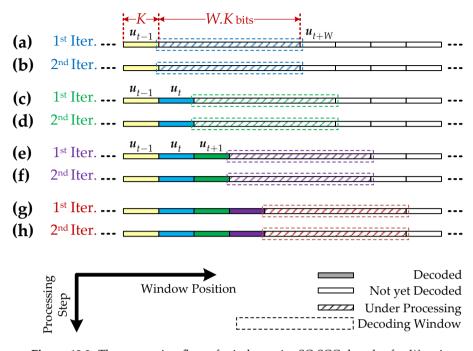

| 15 Fully Pipelined Decoding of SC-SCCs                     | 189 |

| 15.1 Fully Pipelined Iteration Unrolled Architecture       | 190 |

| 15.2 Jumping Window Decoding (JWD)                         | 194 |

| 15.3 Results and Discussion                                | 196 |

| Future Works                                               | 203 |

| Appendix A Popular Science Summary                         |     |

| Bibliography                                               | 209 |

### Preface

This thesis summarizes my academic work carried out during five years in the Digital ASIC group, at the department of Electrical and Information Technology (EIT), Lund University, Sweden. The main contributions are derived from the following articles:

1. Mojtaba Mahdavi, Stefan Weithoffer, Matthias Herrmann, Liang Liu, Ove Edfors, Norbert Wehn, and Michael Lentmaier, "Spatially Coupled Serially Concatenated Codes: Performance Evaluation and VLSI Design Tradeoffs, "submitted to *IEEE Transactions on Circuits and Systems I* (*TCAS-I*): Regular Papers, August 2021.

**Contribution:** The research work has been performed by the first author under the guidance of the remaining authors. The first author has presented two decoding algorithms along with the corresponding VLSI architectures for the spatially coupled serially concatenated codes (SC-SCCs). Also, the author has discussed different tradeoffs between silicon area, throughput, and latency of these schemes.

Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "Angular-Domain Massive MIMO Detection: Algorithm, Implementation, and Design Tradeoffs," in *IEEE Transactions on Circuits and Systems I (TCAS-I): Regular Papers*, vol. 67, no. 6, pp. 1948-1961, January 2020, doi: 10.1109/TCSI.2020.2968408.

**Contribution:** The first author has performed this research work under the guidance of the other authors. The first author has proposed an angular-domain massive MIMO detection scheme, which performs uplink detection using compressed channel matrix. The analysis of computational complexity and required memory, performance evaluation, and design tradeoffs have been discussed in detail. 3. Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "A Low Latency FFT/IFFT Architecture for Massive MIMO Systems Utilizing OFDM Guard Bands," in *IEEE Transactions on Circuits and Systems I (TCAS-I): Regular Papers*, vol. 66, no. 7, pp. 2763-2774, February 2019, doi: 10.1109/TCSI.2019.2896042.

**Contribution:** This research work has been performed by the first author under the guidance of the remaining authors. The first author has developed a hardware architecture, which utilizes the OFDM guard bands to reduce the latency of FFT/IFFT in the OFDM-based systems including massive MIMO systems.

4. **Mojtaba Mahdavi**, Liang Liu, Ove Edfors, Michael Lentmaier, Norbert Wehn, and Stefan Weithoffer, "Towards Fully Pipelined Decoding of Spatially Coupled Serially Concatenated Codes," in 2021 IEEE International Symposium on Topics in Coding (ISTC), Montreal, Canada, August 2021, pp. 1-5.

**Contribution:** The first author has developed a decoding scheme, which enables pipelined implementation of SC-SCCs decoder. Also, the author has evaluated the decoding performance of this scheme in several latency scenarios with different design parameters.

Mojtaba Mahdavi, Muhammad Umar Farooq, Liang Liu, Ove Edfors, Viktor Öwall, and Michael Lentmaier, "The Effect of Coupling Memory and Block Length on Spatially Coupled Serially Concatenated Codes," in *IEEE 93rd Vehicular Technology Conference (VTC)*, Helsinki, Finland, December 2020, pp. 1-7, doi: 10.1109/VTC2021-Spring51267.2021.9448689.

**Contribution:** This research work has been performed by the first author under the guidance of the remaining authors. The first author has performed an extensive performance evaluation to investigate the effect of different design parameters in a wide range on the decoding performance of several SC-SCC scenarios.

Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "A VLSI Implementation of Angular-Domain Massive MIMO Detection," in 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, May 2019, pp. 1-5, doi: 10.1109/ISCAS.2019.8702720.

**Contribution:** The first author has designed and implemented, under guidance of the other authors, an angular-domain linear detection

scheme for massive MIMO systems. In this work a massive MIMO system with 128 antennas at the base station, which communicates with 16 user equipments is considered.

Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "A Low Complexity Massive MIMO Detection Scheme Using Angular-Domain Processing," in 2018 IEEE Global Conference on Signal and Information Processing (GlobalSIP), Anaheim, CA, USA, November 2018, pp. 181-185, doi: 10.1109/GlobalSIP.2018.8646483.

**Contribution:** The first author under the guidance of the remaining authors has investigated the massive MIMO channel properties and developed a compression algorithm to reduce the size of channel matrix. As a result, computational complexity and required memory are reduced significantly compared to the traditional antenna-domain massive MIMO detectors.

Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "A Low Latency and Area Efficient FFT Processor for Massive MIMO Systems," in 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, May 2017, pp.1-4, doi:10.1109/ISCAS.2017.8050692.

**Contribution:** The first author has designed a hardware architecture to realize a low-latency FFT/IFFT, which can be used in the OFDM-based massive MIMO systems.

Furthermore, I have contributed in the following publications, which are not included in this thesis:

- 9. **Mojtaba Mahdavi**, Ove Edfors, Viktor Öwall, and Liang Liu, "Angular-Domain Massive MIMO Detection: Algorithm, Implementation, and Design Tradeoffs," in 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, South Korea, May 2021.

- 10. **Mojtaba Mahdavi**, Ove Edfors, Viktor Öwall, and Liang Liu, "Low-Complexity Massive MIMO Detection Scheme," in 2019 *ELLIIT Workshop*, Karlskrona, Sweden, October 2019.

- 11. **Mojtaba Mahdavi** and Mahdi Shabany, "A 13 Gbps, 0.13 μm CMOS, Multiplication-Free MIMO Detector", in *Springer Journal of Signal Pro*-

*cessing Systems*, vol. 88, no. 3, pp. 273-285, June 2016, doi:10.1007/s11265-016-1145-2.

- Mahdi Shabany, Roya Doostnejad, Mojtaba Mahdavi, and Glenn Gulak, "A 38 pJ/b Optimal Soft-MIMO Detector", in *IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II)*, vol. 64, no. 9, pp. 1062-1066, September 2017, doi:10.1109/TCSII.2016.2641964.

- Mahdi Shabany, Dimpesh Patel, Mario Milicevic, Mojtaba Mahdavi, and Glenn Gulak, "A 70 pJ/b Configurable 64-QAM Soft MIMO Detector", in *Integration, the VLSI Journal*, vol. 63, pp. 74-86, September 2018, doi:10.1016/j.vlsi.2018.05.008.

### Acknowledgments

The five-year PhD journey has been a joyful experience and full of adventures. I believe this would not have been possible without the support, guidance, and friendship of many people.

I would like to express my sincere gratitude to my supervisors, Associate Prof. Liang Liu, Prof. Viktor Öwall, and Prof. Ove Edfors. My heartfelt gratitude to Associate Professor Liang Liu, for his limitless support, encouragement, patience in listening to my complaints, and always being around for discussions. I will never forget your great help and thank you for guiding me throughout this journey. I am certainly indebted to Prof. Viktor Öwall, for his kind support, trusting me to be his PhD student, and giving me the chance to pursue this journey. I am also grateful to Prof. Ove Edfors, for always providing constructive feedback and his massive help in the field of wireless communication, even with a very busy schedule. I would like to thank Associate Prof. Michael Lentmaier, for his support, fruitful collaboration, and helpful meetings during the last two years of my PhD studies. Thanks to all of you for your support and what we accomplished together.

My gratitude also goes to the head of department, administrative, and technical staff at EIT department, Prof. Daniel Sjöberg, Associate Prof. Stefan Höst, Pia Bruhn, Anne Andersson, Elisabeth Nordström, Elisabeth Ohlsson, Linda Bienen, Erik Göthe, Josef Wajnblom, Bertil Lindvall, Stefan Molund, and Erik Jonsson, who made my life as a PhD student smooth.

I would like to thank all my past and present colleagues at EIT department. I would also like to extend my gratitude to my friends and their families in Sweden, who have created pleasant weekends for me and my family. Special thanks to Farrokh Ghani Zadegan and Babak Mohammadi for their help since the beginning of this journey. I would like to express my appreciation to my friends in Iran and my supervisors in Sharif University of Technology. I am so grateful to Prof. Norbert Wehn for his great support and hosting me at the Division of Microelectronic Systems Design in Technical University of Kaiserslautern in Germany. I want to acknowledge the discussions we had with other colleagues and also the help with administrative matters given by Martina Jahn. I would also thank Associate prof. Stefan Weithoffer at electronics department, IMT Atlantique in France, for his supportive and detailed discussions. During this research visit, I gained valuable experience, met wonderful people there, and had exciting stay in Kaiserslautern.

I would like to heartily thank my wonderful parents and siblings for their unconditional love, sacrifices, and support throughout my life. I would not be here without your love and tireless support. Although I have unfortunately been physically far away from you, you always have a place in my heart.

I would also like to express my excitement to my cute daughter, Zahra, who was born at the early stage of my PhD studies. Zahra, you are the reason why I feel great about the future.

Last but not least, my deepest gratitude to my wife for her endless love, patience, and selflessness so that I could pursue my PhD studies. Words cannot express how grateful I am to Marzieh, my better half, who has made our life full of happiness since eleven years ago. Marzieh, I love you more than I can ever express.

In memory of my mother-in-law, who passed away in the last year of this journey.

Mojtaba Mahdavi

Lund, March 2021

## Acronyms

| 1G<br>3G<br>3GPP<br>4G<br>5G | 1st Generation<br>3th Generation<br>3rd Generation Partnership Project<br>4th Generation<br>5th Generation |

|------------------------------|------------------------------------------------------------------------------------------------------------|

| ACQ                          | Acquisition                                                                                                |

| ACSU                         | Add-Compare-Select Unit                                                                                    |

| APP                          | A Posteriori Probability                                                                                   |

| ASIC                         | Application Specific Integrated Circuit                                                                    |

| AWGN                         | Additive White Gaussian Noise                                                                              |

|                              |                                                                                                            |

| BCJR                         | Bahl-Cocke-Jelinek-Raviv                                                                                   |

| BER                          | Bit Error Rate                                                                                             |

| BF                           | Butterfly                                                                                                  |

| BMU                          | Branch Metric Unit                                                                                         |

| BP                           | Belief Propagation                                                                                         |

| BPSK                         | Binary Phase Shift Keying                                                                                  |

| BS                           | Base Station                                                                                               |

| СС                           | Clock Cycle                                                                                                |

| CD                           | Cholesky Decomposition                                                                                     |

| CMOS                         | Complementary Metal Oxide Semiconductor                                                                    |

| СР                           | Cyclic Prefix                                                                                              |

| CSD                          | Canonical Signed Digit                                                                                     |

| CSEE                         | Column-SE Enumeration                                                                                      |

| CSI                          | Channel State Information                                                                                  |

| DFT        | Discrete Fourier Transform              |

|------------|-----------------------------------------|

| DIF        | Decimation In Frequency                 |

| DIT        | Decimation In Time                      |

| ED         | Euclidean distance                      |

| eMBB       | Enhanced Mobile Broadband               |

| FDD        | Frequency Division Duplex               |

| FDM        | Frequency Division Multiplexing         |

| FEC        | Forward Error Correction                |

| FFT        | Fast Fourier Transform                  |

| FIFO       | First-In First-Out                      |

| FPGA       | Field Programmable Gate Array           |

| FPMAP      | Fully Parallel MAP                      |

| HDL        | Hardware Description Language           |

| ICI        | Inter-Carrier Interference              |

| IFFT       | Inverse Fast Fourier Transform          |

| i.i.d.     | Independent and Identically Distributed |

| IoT        | Internet of Things                      |

| ISI        | Inter-Symbol Interference               |

| IUI        | Inter-User Interference                 |

| JWD        | Jumping Window Decoding                 |

| LDPC       | Low-Density Parity-Check                |

| LLR        | Log-Likelihood Ratio                    |

| LNA        | Low Noise Amplifier                     |

| Local-SOVA | Local Soft-Output Viterbi Algorithm     |

| LOS        | Line-of-Sight                           |

| LTE        | Long Term Evolution                     |

| LTE-A      | LTE Advanced                            |

| LuMaMi     | Lund University Massive MIMO            |

| LUT        | Look-Up Table                           |

| MAP        | Maximum a Posteriori                    |

| MDC        | Multipath Delay Commutator              |

| MDF        | Multipath Delay Feedback                |

| MF         | Matched Filtering                       |

| MIMO       | Multiple-Input Multiple-Output          |

| ML<br>MMSE<br>mMTC<br>MPC<br>MPD<br>MU<br>MU-MaMi | Maximum Likelihood<br>Minimum Mean Square Error<br>Massive Machine Type Communications<br>Multi-Path Components<br>Message Passing Detector<br>Multi User<br>Multi-User Massive MIMO     |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAE                                               | Normalized Area Efficiency                                                                                                                                                               |

| NEE                                               | Normalized Energy Efficiency                                                                                                                                                             |

| NL                                                | Non Linear                                                                                                                                                                               |

| NLOS                                              | Non-Line-of-Sight                                                                                                                                                                        |

| NMT                                               | Nordic Mobile Telephone                                                                                                                                                                  |

| OFDM                                              | Orthogonal Frequency Division Multiplexing                                                                                                                                               |

| PAP                                               | Per Antenna Processing                                                                                                                                                                   |

| PCC                                               | Parallel Concatenated Code                                                                                                                                                               |

| PE                                                | Processing Element                                                                                                                                                                       |

| PMAP                                              | Parallel MAP                                                                                                                                                                             |

| PP                                                | Post Processing                                                                                                                                                                          |

| PSP                                               | Per Subcarrier Processing                                                                                                                                                                |

| PUP                                               | Per User Processing                                                                                                                                                                      |

| QAM<br>QPSK<br>QRD                                | Quadrature Amplitude Modulation<br>Quadrature Phase Shift Keying<br>QR Decomposition                                                                                                     |

| R2BF                                              | Radix-2 Butterfly                                                                                                                                                                        |

| RAM                                               | Random Access Memory                                                                                                                                                                     |

| RF                                                | Radio Frequency                                                                                                                                                                          |

| RSC                                               | Recursive Systematic Convolutional                                                                                                                                                       |

| RSEE                                              | Row-SE Enumeration                                                                                                                                                                       |

| RX                                                | Receiver                                                                                                                                                                                 |

| SC<br>SCC<br>SC-SCC<br>SD<br>SDF<br>SE<br>SFG     | Spatial Coupling<br>Serially Concatenated Code<br>Spatially Coupled Serially Concatenated Codes<br>Sphere Decoding<br>Single-path Delay Feedback<br>Schnorr Euchner<br>Signal Flow Graph |

| SISO  | Soft-Input Soft-Output                        |

|-------|-----------------------------------------------|

| SMAP  | Serial MAP                                    |

| SNR   | Signal-to-Noise Ratio                         |

| SOU   | Soft-Output Unit                              |

| SP    | Single Port                                   |

| SQNR  | Signal-to-Quantization-Noise Ratio            |

| SW    | Sliding Window                                |

| TC    | Turbo Code                                    |

| TDD   | Time Division Duplex                          |

| TFM   | Twiddle Factor Multiplier                     |

| TX    | Transmitter                                   |

| UE    | User Equipment                                |

| UC    | Uncoupled                                     |

| ULA   | Uniform Linear Array                          |

| URC   | Ultra Reliable Communication                  |

| URLLC | Ultra-Reliable and Low-Latency Communications |

| UXMAP | Unrolled XMAP                                 |

| VLSI  | Very Large Scale Integration                  |

| ХМАР  | Piplelined XMAP                               |

| ZF    | Zero Forcing                                  |

# **Mathematical Notations**

| С                                                                     | Complex field                                                        |

|-----------------------------------------------------------------------|----------------------------------------------------------------------|

| $\operatorname{Re}\{\cdot\}$                                          | Real part of complex numbers                                         |

| $\text{Im}\{\cdot\}$                                                  | Imaginary part of complex numbers                                    |

| $ \cdot $                                                             | Absolute value                                                       |

| $\ \cdot\ _2$                                                         | $\ell_2$ -norm                                                       |

| $(\cdot)^*$                                                           | Complex conjugate                                                    |

| $(\cdot)^T$                                                           | Matrix/vector transpose                                              |

| $(\cdot)^H$                                                           | Matrix/vector conjugate-transpose                                    |

| $(\cdot)^{-1}$                                                        | Matrix inverse                                                       |

| $(\cdot)^{\dagger}$                                                   | Matrix pseudo-inverse                                                |

| $(\cdot)_{i,j}$                                                       | (i, j) <sup>th</sup> element of a matrix                             |

| $\widehat{(\cdot)}$                                                   | Angular-domain representation of a matrix/vector                     |

| $(\cdot)'$                                                            | Compressed matrix/vector                                             |

| $\boldsymbol{A} = \begin{bmatrix} \boldsymbol{a}_{m,k} \end{bmatrix}$ | Matrix with element $a_{m,k}$ in the $(m, k)$ <sup>th</sup> position |

| $a = [a_m]$                                                           | Vector with element $a_m$ in the $m$ <sup>th</sup> position          |

| a(i:j)        | <i>i</i> -th to <i>j</i> -th element of vector <b>a</b> |

|---------------|---------------------------------------------------------|

| $dim\{.\}$    | Matrix dimension                                        |

| Tr(.)         | Trace of a square matrix                                |

| $\propto$     | Proportional                                            |

| $\infty$      | Infinity                                                |

| $\approx$     | Approximately                                           |

| $\mathcal{O}$ | Order of computational complexity                       |

|               |                                                         |

# List of Figures

| 2.1 | The estimated world average monthly traffic per subscription  |    |

|-----|---------------------------------------------------------------|----|

|     | for different applications.                                   | 9  |

| 2.2 | Various applications in 5G with different requirements        | 10 |

| 2.3 | Number of mobile subscriptions and data traffic in different  |    |

|     | technologies.                                                 | 11 |

| 2.4 | A simplified block diagram of wireless communication systems. | 12 |

| 2.5 | Multi-path wireless propagation channel                       | 13 |

| 2.6 | MIMO wireless system.                                         | 15 |

| 2.7 | A multi-user massive MIMO system in uplink and downlink.      | 17 |

| 2.8 | A simplified block diagram of baseband processing in OFDM-    |    |

|     | based massive MIMO systems                                    | 20 |

| 3.1 | Design parameters and performance metrics in different ab-    |    |

|     | straction levels for the considered designs in this thesis    | 27 |

| 4.1 | Example design of a radix-2 single-input pipelined FFT/IFFT   |    |

|     | architecture                                                  | 38 |

| 4.2 | The memory content of example design in Figure 4.1 for two    |    |

|     | successive OFDM symbols                                       | 39 |

| 5.1 | OFDM symbol structure with length of $N = 2048$ samples       | 42 |

| 5.2 | The OFDM symbol of length $N = 16. \dots \dots \dots \dots$   | 44 |

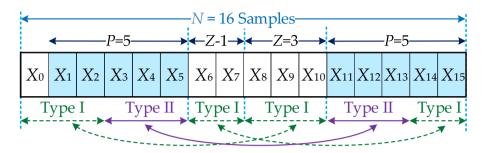

| 5.3          | The content of memories in the example design after skipping     |     |

|--------------|------------------------------------------------------------------|-----|

|              | the zero samples.                                                | 45  |

| 5.4          | Memory content of the example design for two OFDM symbols        |     |

|              | by considering gap between successive symbols                    | 46  |

| 5.5          | Memory content of a 16-point IFFT based on the proposed          |     |

|              | scheduling scheme and memory structure                           | 47  |

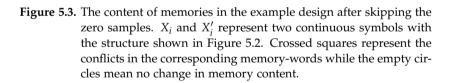

| 5.6          | Conditions for memories and butterfly in Stage 1                 | 48  |

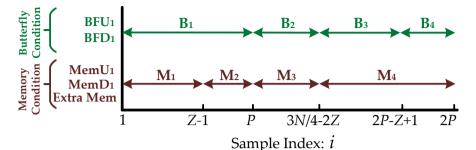

| 5.7          | Conditions for memories and butterflies in Stage <i>m</i>        | 49  |

| 5.8          | Comparison between the processing flow of single-input pipelined | l   |

|              | IFFT in three scenarios.                                         | 51  |

| 5.9          | Proposed VLSI architecture for an <i>N</i> -point FFT/IFFT       | 53  |

| 5.10         | The Radix-2 Butterfly unit (R2BF)                                | 54  |

| 5.11         | Control circuit for the memories and butterfly of Stage 1        | 55  |

| 5.12         | Control circuit for the memories and butterflies of Stage 2 to   |     |

|              | the last stage of FFT/IFFT architecture                          | 56  |

| 5.13         | The architecture of Reconfigurable General Multiplier            | 57  |

| 5.14         | The proposed circuit for Constant Multiplier.                    | 57  |

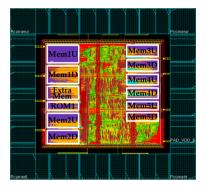

| 5.15         | The layout of the proposed pipelined FFT/IFFT processor          | 59  |

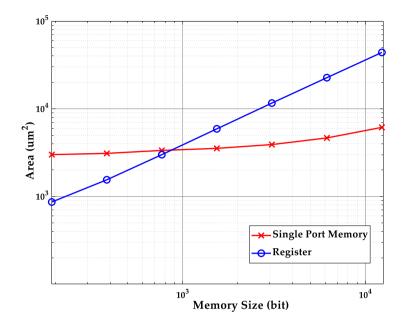

| 5.16         | Design area of different memory realizations in 28 nm technology | 61  |

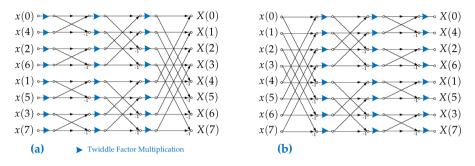

| 6.1          | The SFG of a radix-2 FFT in DIF and DIT.                         | 64  |

| 6.2          | Proof of generality of presented reordering scheme.              | 66  |

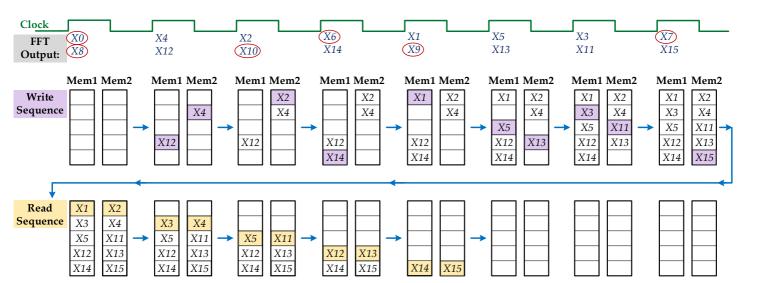

| 6.3          | Step by step operation of developed reordering mechanism.        | 67  |

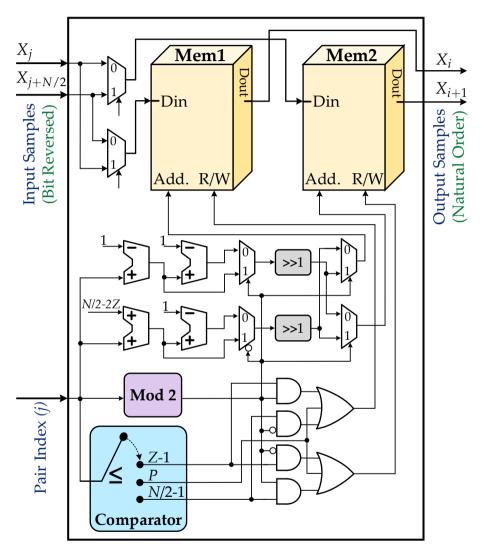

| 6.4          | VLSI architecture of the reordering mechanism.                   | 69  |

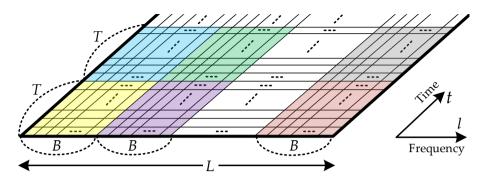

| 7.1          | Time-frequency blocks in massive MIMO systems.                   | 80  |

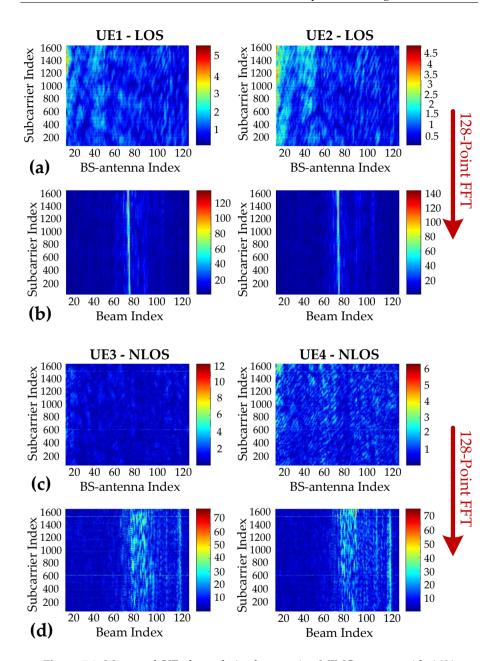

| 7.2          | Measured UE channels in the massive MIMO system                  | 82  |

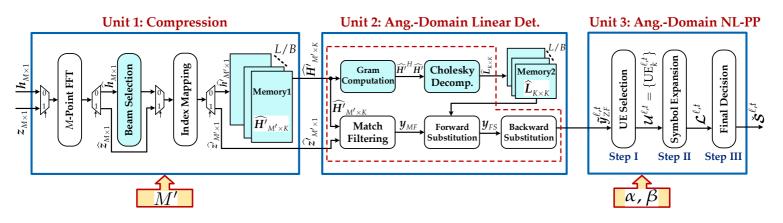

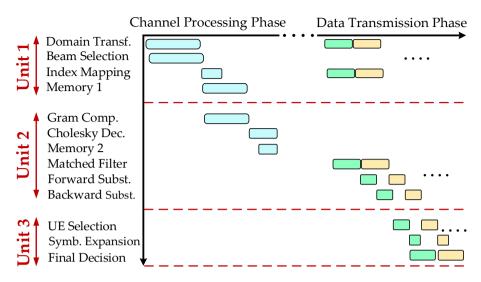

| 8.1          | Processing chain of proposed angular-domain massive MIMO         |     |

|              | detection scheme.                                                | 86  |

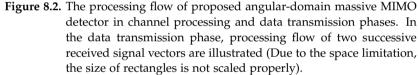

| 8.2          | Processing flow of the angular-domain massive MIMO detector.     | 87  |

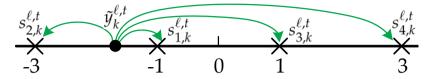

| 8.3          | SE enumeration technique in the real-domain constellation        | 91  |

| 8.4          | Symbol expansion scheme for the ZF output of <i>k</i> -th UE     | 92  |

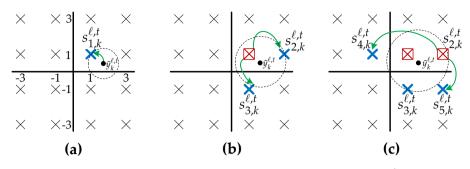

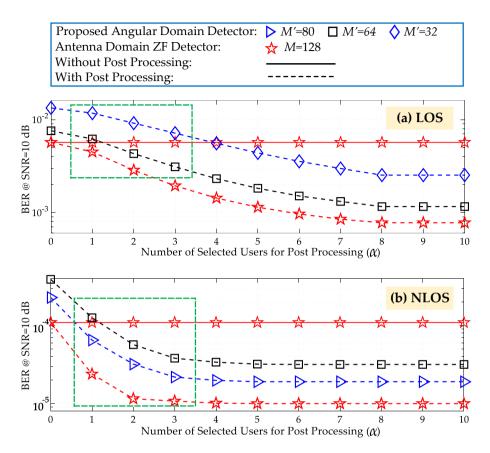

| 9.1          | BER Performance of the proposed angular-domain detector          |     |

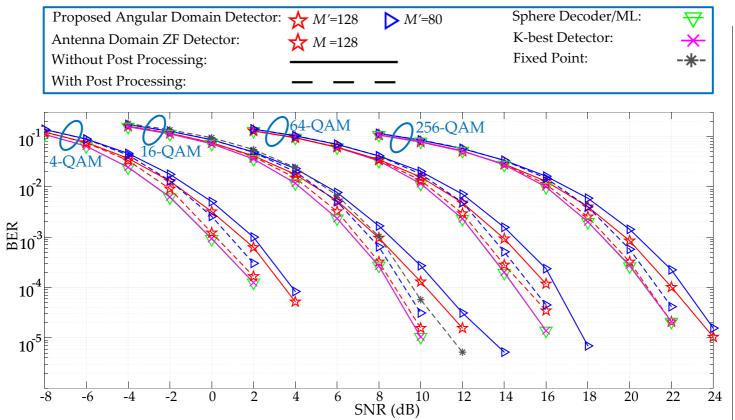

|              | and antenna-domain ZF in LOS and NLOS scenarios                  | 97  |

| 9.2          | Distribution of strong UEs in the angular domain for LOS and     |     |

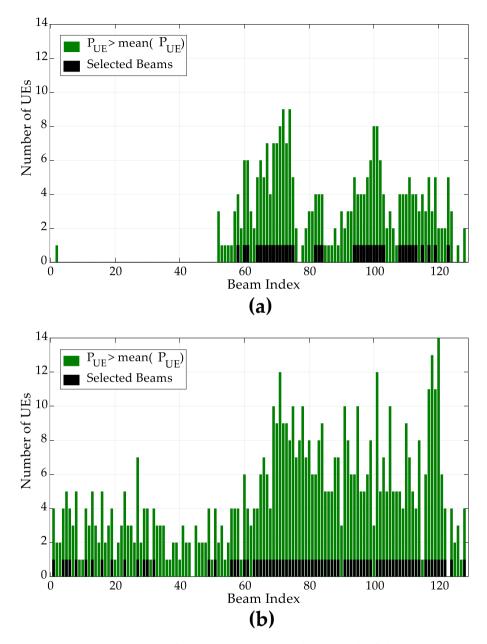

|              | NLOS scenarios.                                                  | 98  |

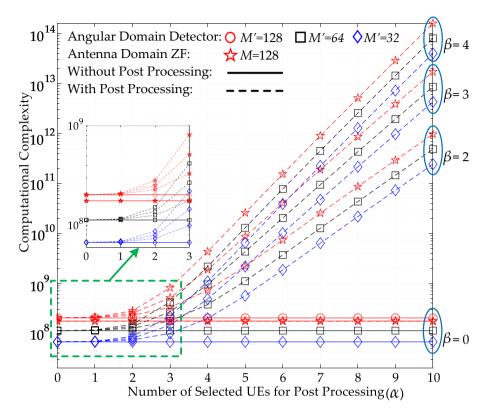

| 9.3          |                                                                  | 101 |

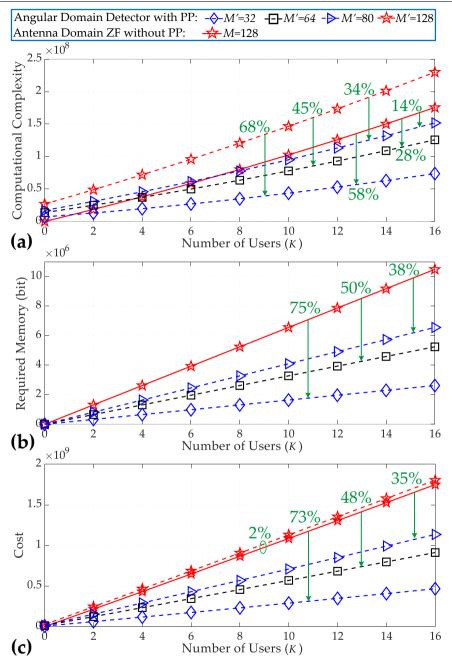

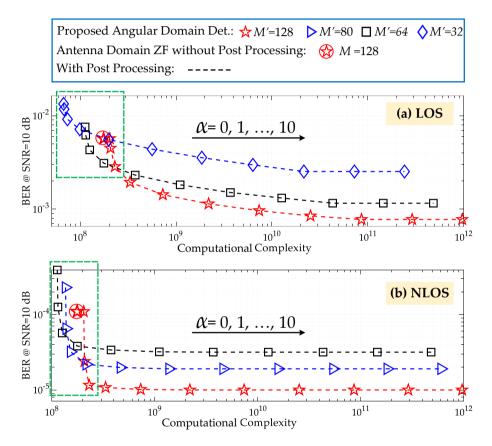

| 9.4          | Design comparison in terms of computational complexity, size     |     |

| <i>,</i> ,,, |                                                                  | 104 |

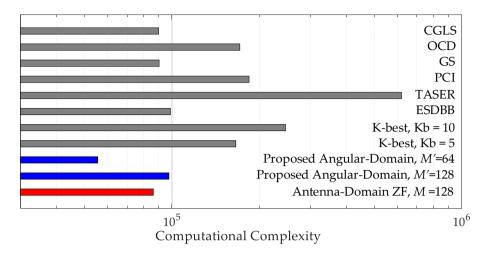

| 9.5          | Comparison between the computational complexity of differ-       |     |

|              |                                                                  | 106 |

| 9.6          | Total computational complexity of antenna-domain detection       |     |

|              |                                                                  | 107 |

|              | LL                                                               |     |

| 9.7   | Performance evaluation for different number of selected UEs     |     |

|-------|-----------------------------------------------------------------|-----|

|       | in the post processing                                          | 108 |

| 9.8   | Performance versus complexity of antenna-domain detection       |     |

|       | and proposed angular-domain scheme in LOS and NLOS              | 110 |

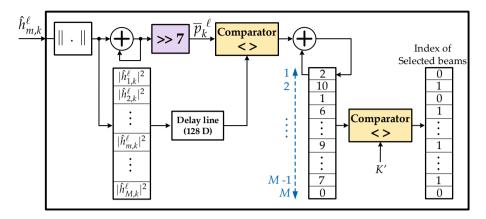

| 10.1  | The structure of Beam Selection and Index Mapping blocks.       | 112 |

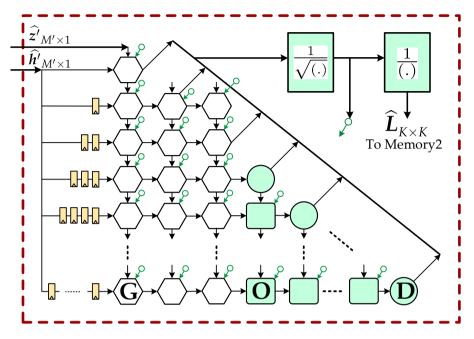

| 10.2  | Proposed systolic array architecture for the Angular-Domain     |     |

|       | Linear-Detection Unit.                                          | 113 |

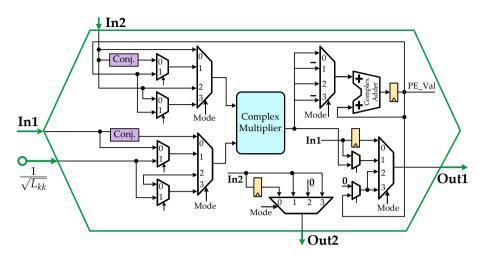

| 10.3  | The VLSI architecture for General PE                            | 114 |

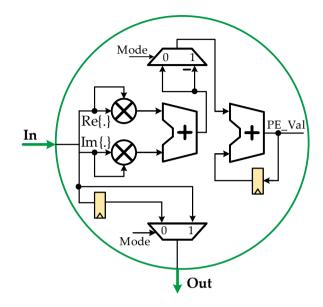

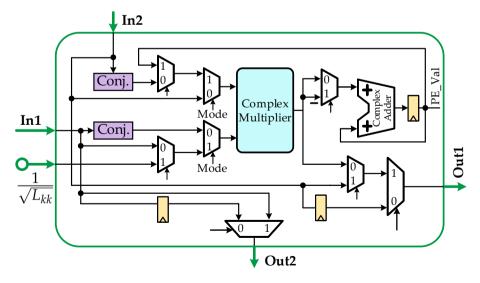

| 10.4  | Developed circuits for the Diagonal PE                          | 115 |

| 10.5  | The detailed architecture for Off-Diagonal PE                   | 115 |

| 10.6  | Different operational modes of the proposed systolic array      | 116 |

| 10.7  | VLSI Architecture for the Angular-Domain Non-Linear Post-       |     |

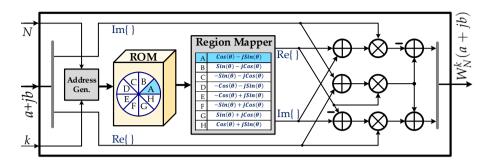

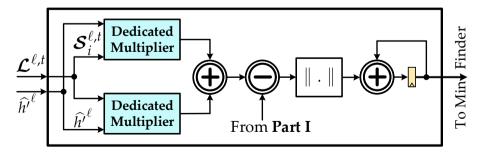

|       | Processing Unit                                                 | 117 |

| 10.8  | The detailed architecture of Mapper and Limiter blocks          | 117 |

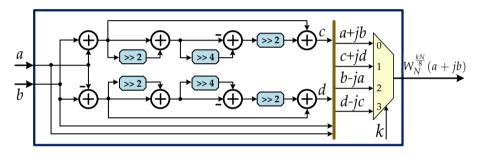

| 10.9  | VLSI Architecture for the Dedicated Multiplier and Constant     |     |

|       | Multiplier                                                      | 119 |

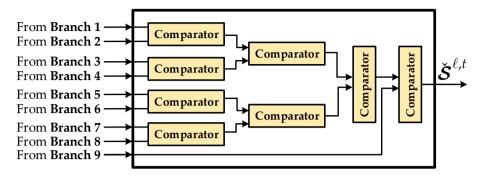

| 10.10 | The architecture of Branch module                               | 119 |

| 10.11 | The structure of Min Finder block.                              | 120 |

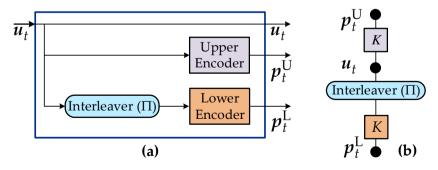

| 11.1  | Block diagram and compact graph representation of PCC           | 129 |

| 11.2  | Block diagram and compact graph representation of SCC           | 130 |

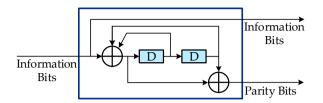

| 11.3  | The structure of RSC encoder.                                   | 131 |

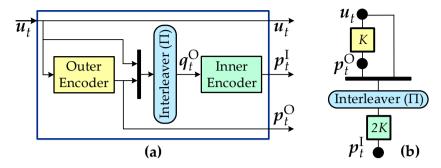

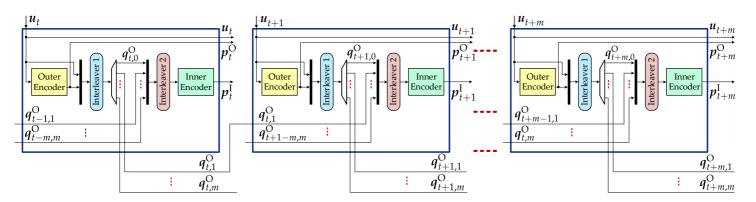

| 11.4  | Structure of SC-SCC encoder with coupling memory <i>m</i>       | 133 |

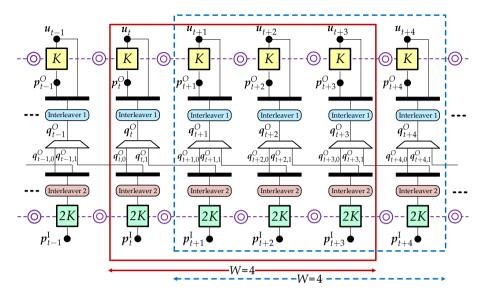

| 11.5  | Compact graph representation of an infinite chain of SC-SCC.    | 135 |

| 12.1  | The processing flow of SCC decoder.                             | 141 |

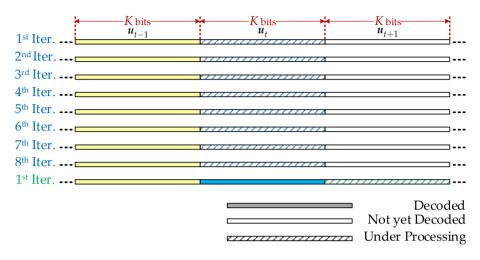

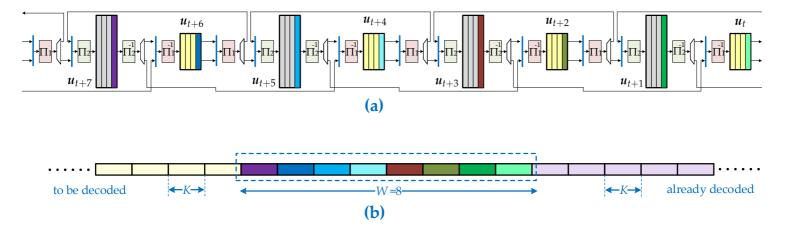

| 12.2  | The processing flow of block-wise SC-SCC decoder                | 144 |

| 12.3  | The processing flow of window-wise SC-SCC decoder               | 148 |

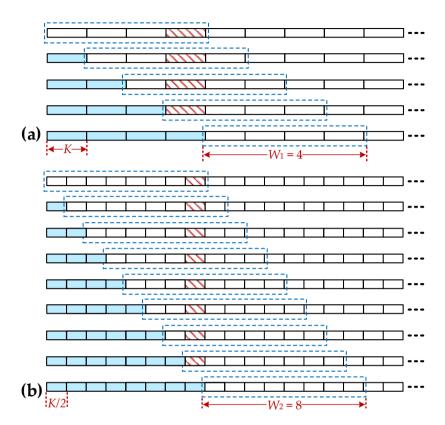

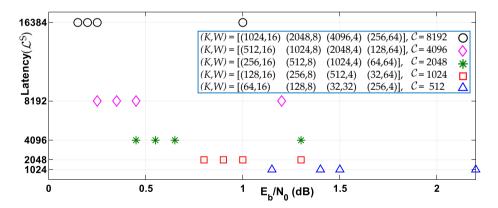

| 13.1  | Window decoding approach for two fixed-latency scenarios        | 155 |

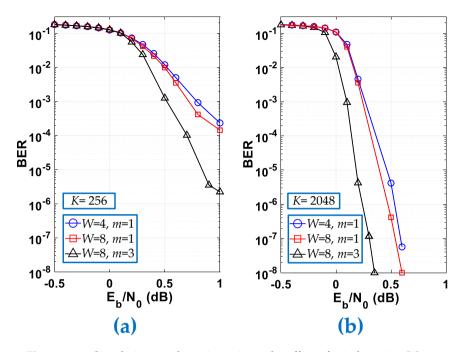

| 13.2  | The effect of coupling memory on the decoding performance.      | 158 |

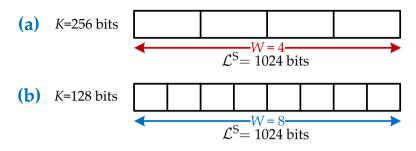

| 13.3  | Two SC-SCC scenarios with the same latency.                     | 159 |

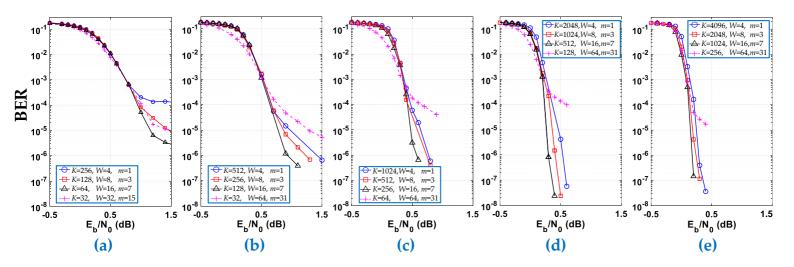

| 13.4  | BER performance of the SC-SCC scenarios in Table 13.2           | 161 |

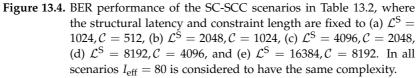

| 13.5  | BER Performance comparison between the proposed SC-SCC          |     |

|       | and uncoupled SCC                                               | 162 |

| 13.6  | The effect of window size on the decoding performance           | 164 |

| 13.7  | The latency-performance tradeoff for the SC-SCC scenarios in    |     |

|       | Table 13.2.                                                     | 164 |

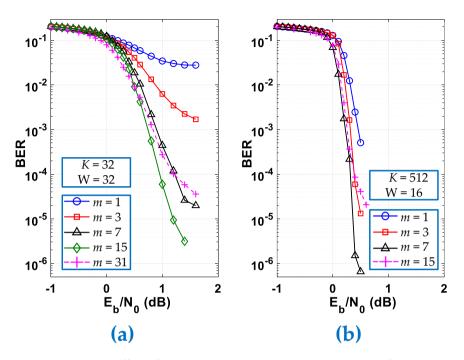

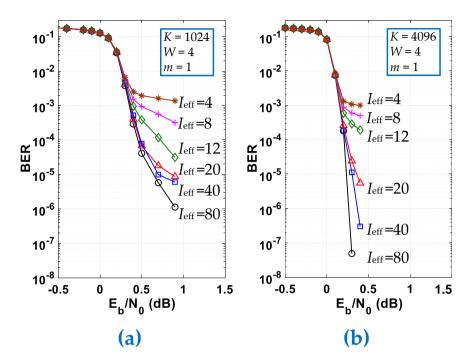

| 13.8  | The effect of number of iterations on the decoding performance. | 165 |

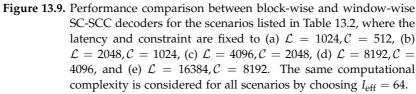

| 13.9  | Performance comparison between block-wise and window-wise       |     |

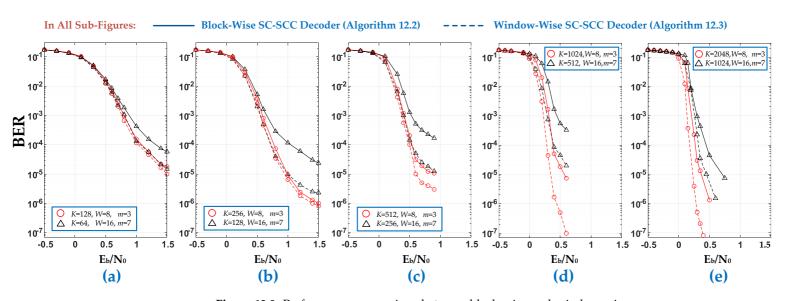

|       | SC-SCC decoders.                                                | 167 |

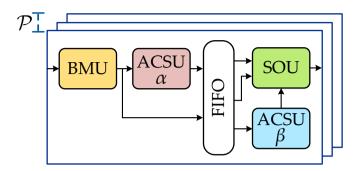

| 14.1  | PMAP decoder architecture schematic                             | 171 |

| 14.2  | XMAP decoder architecture schematic                             | 172 |

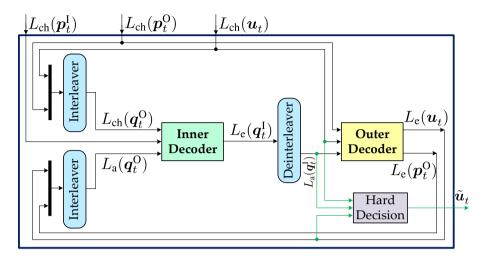

| 14.3  | The VLSI architecture of SCC decoder.                           | 174 |

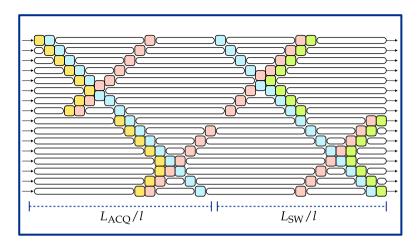

| 14.4  | The VLSI architecture for the block-wise SC-SCC decoder         | 175 |

| 14.5 | The VLSI architecture for the window-wise SC-SCC decoder          | 177 |

|------|-------------------------------------------------------------------|-----|

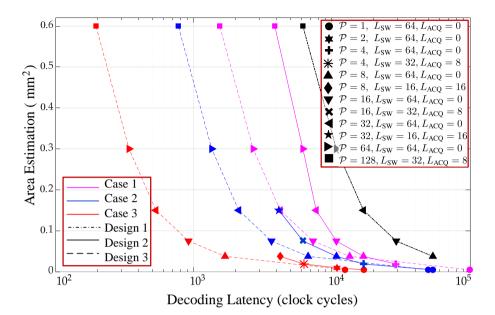

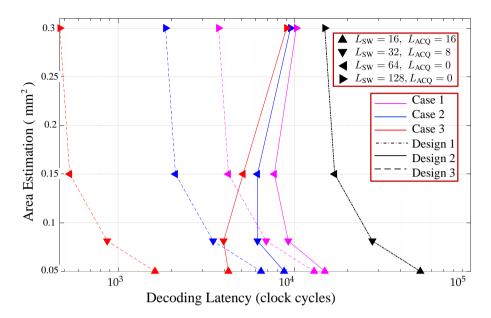

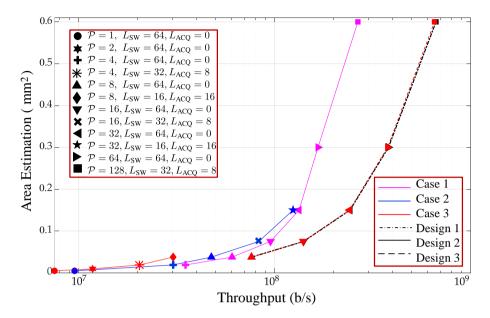

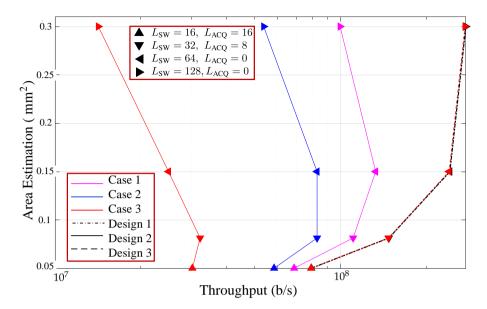

| 14.6 | Area and decoding latency estimates for the decoders with a       |     |

|      | SMAP/PMAP component decoder architecture                          | 183 |

| 14.7 | Area and decoding latency estimates for the decoders with an      |     |

|      | XMAP component decoder architecture                               | 184 |

| 14.8 | Area and throughput estimates for the decoders with a PMAP        |     |

|      | component decoder architecture                                    | 185 |

| 14.9 | Area and throughput estimates for the decoders with an XMAP       |     |

|      | component decoder architecture                                    | 186 |

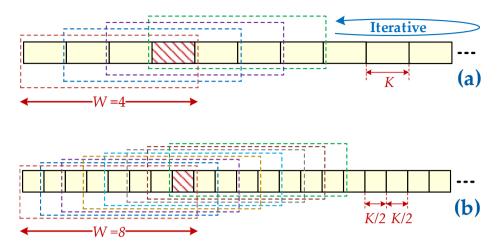

| 15.1 | High-level architecture of a decoder pipeline for fully pipelined |     |

|      | decoding of SC-SCCs.                                              | 192 |

| 15.2 | Window decoding (WD) scheme for two SC-SCC scenarios with         |     |

|      | a fixed structural latency and different block lengths            | 193 |

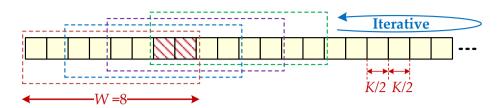

|      | Proposed jumping window decoding (JWD) for the SC-SCC             | 195 |

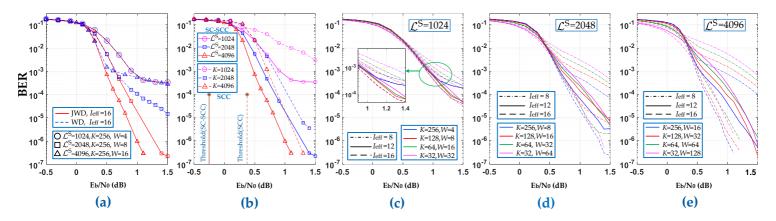

| 15.4 | BER Performance comparison between the proposed JWD and           |     |

|      | WD schemes.                                                       | 198 |

## List of Tables

| 5.1  | System parameters in the massive MIMO framework                   | 42  |

|------|-------------------------------------------------------------------|-----|

| 5.2  | Control scheme of memories in Stage 1                             | 48  |

| 5.3  | Control scheme of butterfly in Stage 1                            | 48  |

| 5.4  | Control scheme of memories in Stage $m, m = 2,, \log_2 N$         | 49  |

| 5.5  | Control scheme of butterfly in Stage $m, m = 2,, \log_2 N \dots$  | 49  |

| 5.6  | Comparison between <i>N</i> -point IFFT schemes with single-input |     |

|      | pipelined architectures                                           | 52  |

| 5.7  | Four operation modes of the presented design                      | 58  |

| 5.8  | Tradeoff between latency and area for 2048-point FFT/IFFT         | 59  |

| 5.9  | Implementation results of the FFT/IFFT                            | 60  |

| 5.10 | Design comparison between FFT/IFFT architectures                  | 62  |

| 6.1  | Implementation results of the reordering circuit                  | 68  |

| 9.1  | Complexity and memory requirement of antenna-domain de-           |     |

|      | tectors and proposed angular-domain scheme                        | 102 |

| 10.1 | Design comparison between MU-MaMi detectors                       | 122 |

| 13.1 | Computational complexity per decoded bit in Log-MAP BCJR.         | 154 |

| 13.2 | Different SC-SCC scenarios with the same latency, constraint      |     |

|      | length, and complexity.                                           | 157 |

| 14.1 | Design comparison between VLSI architectures of uncoupled         |     |

|      | and coupled SCC decoders                                          | 179 |

| 14.2 | Place and route results for the computational units            | 180 |

|------|----------------------------------------------------------------|-----|

| 14.3 | Component decoder parameters for the silicon area and la-      |     |

|      | tency estimations.                                             | 182 |

| 15.1 | SC-SCC scenarios with fixed structural latency and complexity. | 196 |

| 15.2 | Place and route results of the MAP computational kernels       | 199 |

| 15.3 | Area and throughput estimates of pipelines for different block |     |

|      | lengths and $I_{\text{eff}}$                                   | 199 |

# 1

### Introduction

This thesis presents an interdisciplinary study of wireless communication and digital hardware design. More specifically, the study is on co-optimization of algorithms and hardware implementations of the key components in the digital baseband processing in wireless communication systems. It is envisioned that by the end of 2026 the number of mobile subscriptions will be around 8.8 billion and total mobile data traffic is estimated to reach 226 EB per month [1]. To satisfy such demands, the 5th generation (5G) standard was designed to boost the overall network capacity while ensuring low-latency and highly-reliable links [2]. To keep up with the rapid growth in wireless data traffic and number of subscriptions, and to support emerging applications, the future networks should deliver higher data rates, lower latency, and higher link-reliability [3]. Since the available frequency spectrum is limited, the transmission resources must be utilized as efficiently as possible.

In order to improve spectral efficiency and link reliability, advanced communication schemes are needed for wireless data transmission. Massive multiple-input multiple-output (MIMO) is such a scheme, which can offer very high spectral and energy efficiency [4] and it is considered as a key technology in 5G [5]. In massive MIMO systems, the base station (BS) is equipped with a large number of antennas, serving several user equipments (UEs) simultaneously using the same time and frequency resources. The benefits of massive MIMO entail a significant increase in signal processing complexity at the BS, where sophisticated signal processing techniques are required. Due to the large number of BS antennas, most of the computations are performed using large matrices and vectors, which results in challenges to meet the requirements on latency, data rate, and hardware cost. In order to further enhance the link reliability and communication performance, channel coding schemes can be used. Spatially coupled codes are a powerful class of codes, which can provide a close-to-capacity decoding performance [6]. This type of channel coding scheme can be used in the upcoming use-cases in wireless systems beyond 5G (B5G), where a very good error correction performance is required. However, designing high-performance and hardware-friendly decoding algorithms for this type of code is a very challenging task.

Eventually, these complex algorithms have to be realized using very large scale integration (VLSI) architectures and implemented in hardware. Therefore, hardware-efficient realization of massive MIMO baseband processor has become a critical challenge, being at the forefront of research for several years.

The main focus of this thesis is to explore the efficient VLSI realization of baseband processing of massive MIMO systems. The target subject faces several challenges in practical implementations, such as requirements of low latency, high communication performance, and low hardware cost. This thesis addresses these challenges by investigating system-level features and performing co-optimization at the algorithm and architecture level. Also, several design tradeoffs are discussed and presented for key functional blocks of massive MIMO baseband processing.

#### 1.1. SCOPE OF THE THESIS

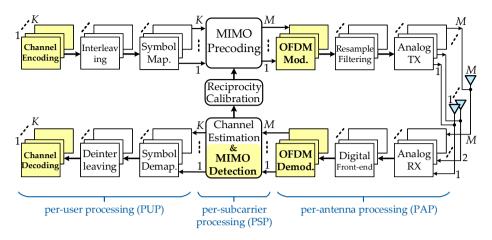

Digital baseband processing in wireless communication systems includes several components such as digital front end, orthogonal frequency-division multiplexing (OFDM) modulation/demodulation, channel estimation, MIMO processing, interleaving/deinterleaving, error correction scheme, etc. Among them, this thesis mainly focuses on some of the crucial blocks in a typical baseband processing chain, i.e., OFDM modulation, OFDM demodulation, MIMO processing, channel encoding, and channel decoding.

The central part of this thesis mainly addresses the following questions:

- Can co-optimization techniques be leveraged in different design stages to trade between complexity, latency, hardware cost, and communication performance in massive MIMO baseband?

- Are there special system-level characteristics, which can be exploited to reduce the processing latency of OFDM (de)modulation?

- Is it possible to exploit characteristics of massive MIMO propagation channel to reduce the complexity and lower the hardware cost of massive MIMO baseband processing, e.g., reducing the size of required memory?

- How to improve the reliability in communication links between the BS and UEs by exploiting the spatial coupling? How to efficiently implement the decoder of such channel coding schemes?

#### **1.2. THESIS OUTLINE AND CONTRIBUTIONS**

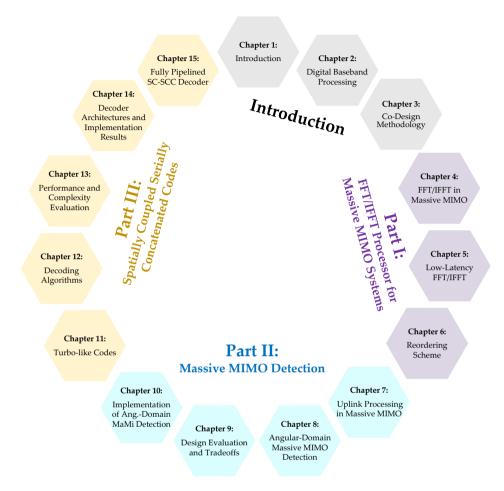

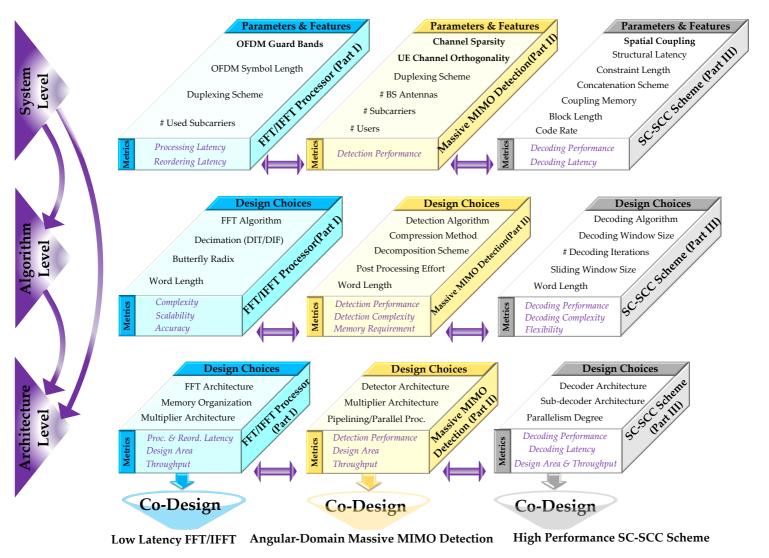

This thesis is divided into fifteen chapters as shown in Figure 1.1. The first three chapters of the thesis give an overview of the research field and present a general reference information on terms and concepts, which will be used later in this thesis. Chapter 2 provides an introduction to the field of wireless communication systems including propagation channel, different wireless transmission technologies, and massive MIMO baseband processing, with the focus on functional blocks, which are targeted in this thesis. Chapter 3 presents the design methodology and tradeoffs to achieve hardware-efficient massive MIMO baseband processor. The remaining chapters of this thesis are organized into three parts, i.e., Part I–III, as follows.

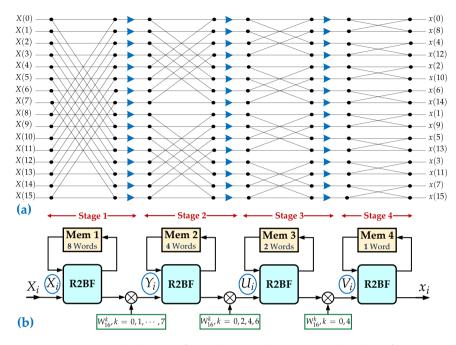

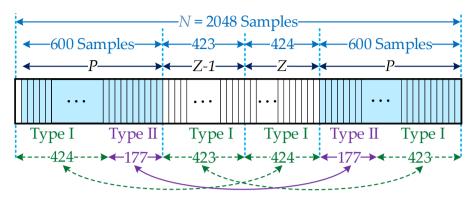

Part I includes three chapters. The latency requirements of OFDM modulation and demodulation in the context of massive MIMO systems are discussed in Chapter 4. Then, Chapter 5 presents a low-latency fast Fourier transform (FFT) and inverse FFT (IFFT) along with the VLSI architecture and application specific integrated circuit (ASIC) implementation results. This is followed by an efficient reordering scheme for uplink demodulation in OFDM-based systems in Chapter 6.

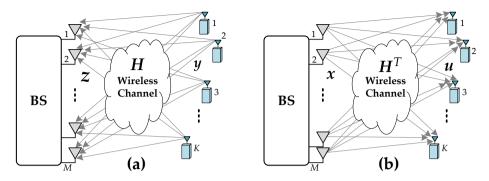

Part II starts by introducing the concept of massive MIMO detection and propagation channel in Chapter 7. Then, the proposed angular-domain massive MIMO detection algorithm is described in Chapter 8. The complexity and detection performance of angular-domain massive MIMO detection are analyzed in Chapter 9, and different design tradeoffs are discussed. Chapter 10 presents the VLSI architecture, which realizes the angular-domain massive MIMO detection along with corresponding synthesis results.

Part III consists of five chapters. In Chapter 11, turbo-like codes and the concept of spatial coupling are introduced. The decoding algorithms for uncoupled and spatially coupled serially concatenated codes (SC-SCCs) are presented in Chapter 12. Then, in Chapter 13 the decoding performance and complexity of these schemes are evaluated and several design tradeoffs are discussed. The VLSI architectures to realize these decoding algorithms are presented in Chapter 14 and the corresponding latency, throughput, and silicon area are analyzed. Moreover, a fully-pipelined decoding scheme for SC-SCCs along with the estimation of throughput and hardware cost are introduced in Chapter 15.

Finally, the thesis is concluded by a chapter with outlook for future work. Figure 1.1 shows a general view of the thesis content.

Figure 1.1. The outline of this thesis.

#### PART I: FFT/IFFT PROCESSOR FOR MASSIVE MIMO SYSTEMS

New services and applications require low-latency communication links and aim for data delivery within a specified delay. In this regard, one area of design focus for 5G standard is to support time-critical (low-latency) communications, where the end to end latency is as low as 1 ms [7]. Self-driving cars, cloud gaming, and factory robots are examples of such applications that require a low latency [8].

On the other hand, in time division duplexing (TDD) mode, which is considered as the operation mode of massive MIMO system in this work, the latency requirement becomes far more challenging. This is due to the sharing of available time budget between uplink and downlink processing as well as the link-direction switching time. This time budget depends on how fast the channel is changed due to the changes in the propagation environment and users positions.

Latency analysis in [9] shows that a considerable part of latency in the baseband of OFDM-based massive MIMO systems is introduced by OFDM modulation and demodulation. This includes the time needed to perform FFT/IFFT and to reorder the generated output samples. To address the low-latency demand of massive MIMO systems, an FFT/IFFT processor and corresponding reordering scheme are proposed in this part of the thesis, which reduce the latency of OFDM-based systems considerably. The main idea is to utilize the OFDM guard bands to reduce the number of required computations, and therefore the processing time. To realize this idea, a modified pipelined architecture with a reorganized memory structure and an efficient data scheduling mechanism are developed.

The content of Part I is based on following publications:

- Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "A Low Latency FFT/IFFT Architecture for Massive MIMO Systems Utilizing OFDM Guard Bands," in *IEEE Transactions on Circuits and Systems I* (*TCAS-I*): Regular Papers, vol. 66, no. 7, pp. 2763-2774, February 2019, doi: 10.1109/TCSI.2019.2896042.

- Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "A Low Latency and Area Efficient FFT Processor for Massive MIMO Systems," in 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, May 2017, pp. 1-4, doi: 10.1109/ISCAS.2017.8050692.

#### PART II: MASSIVE MIMO DETECTION

Due to the large number of BS antennas in massive MIMO systems, the computational complexity of uplink detection is increased significantly compared to the conventional MIMO systems. Moreover, the amount of memory which is needed to store the channel state information (CSI) becomes orders of magnitude larger than the one in traditional small-scale MIMO systems.

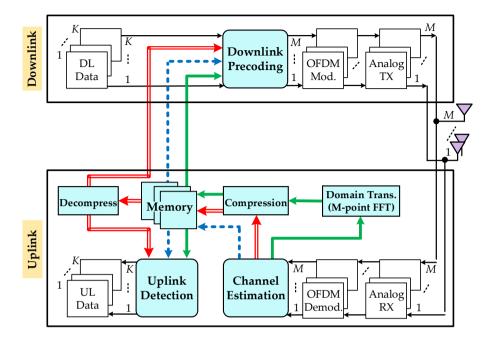

To address these challenges, a new approach to detection in massive MIMO systems is presented in this part of the thesis. To this end, we have investigated the sparsity of massive MIMO channels using real-measured channel data. The underlying idea in our scheme is to exploit the sparsity of the massive MIMO channel in the angular domain to reduce the size of the CSI matrix by selecting dominant angles of the wireless signal. Then, the detection is performed in the angular domain using the reduced-size CSI. As a result, the angular-domain massive MIMO detector outperforms the antenna-domain schemes in terms of computational complexity and required memory.

In the proposed scheme, the angular-domain linear detector is followed by a non-linear post-processing scheme, which is designed to improve the overall detection performance of massive MIMO detection. The angular-domain massive MIMO detector is realized using an efficient VLSI architecture, in which the processing is mainly performed by a reconfigurable systolic array.

The content of Part II is based on the following publications:

- Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "Angular-Domain Massive MIMO Detection: Algorithm, Implementation, and Design Tradeoffs," in *IEEE Transactions on Circuits and Systems I (TCAS-I): Regular Papers*, vol. 67, no. 6, pp. 1948-1961, January 2020, doi: 10.1109/TCSI.2020.2968408.

- Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "A VLSI Implementation of Angular-Domain Massive MIMO Detection," in 2019 *IEEE International Symposium on Circuits and Systems (ISCAS)*, Sapporo, Japan, May 2019, pp. 1-5, doi: 10.1109/ISCAS.2019.8702720.

- Mojtaba Mahdavi, Ove Edfors, Viktor Öwall, and Liang Liu, "A Low Complexity Massive MIMO Detection Scheme Using Angular-Domain Processing," in 2018 IEEE Global Conference on Signal and Information Processing (GlobalSIP), Anaheim, CA, USA, November 2018, pp. 181-185, doi: 10.1109/GlobalSIP.2018.8646483.

#### PART III: SPATIALLY COUPLED SERIALLY CONCATENATED CODES

Mission-critical applications are an important group of applications in many recent wireless networks, which have stringent performance and reliability requirements [10, 11]. Remote surgery, railway/aircraft control systems, and vehicle to vehicle communication are just a few examples of such applications [12, 13]. In such cases wireless communications must meet high reliability requirements since any noticeable error can lead to catastrophic outcomes. Sometimes the demand on high reliability comes together with low latency requirements. Several channel coding techniques, such as turbo codes and low parity check codes (LDPC), have been proposed to improve the reliability of wireless communication systems [14].

Spatially coupled serially concatenated codes (SC-SCCs) are a class of spatially coupled turbo-like codes, which have a close-to-capacity performance and low error floor [6]. In this part of the thesis, a comprehensive design space exploration is performed to reveal different aspects of SC-SCCs. Also, it is demonstrated how this class of codes can be realized in hardware, which has not previously been investigated in the literature. To this end, different SC-SCC decoding schemes along with the VLSI architectures are presented. Various design tradeoffs between decoding performance, complexity, latency, throughput, and hardware cost are discussed.

The content of Part III is based on the following publications:

- Mojtaba Mahdavi, Stefan Weithoffer, Matthias Herrmann, Liang Liu, Ove Edfors, Norbert Wehn, and Michael Lentmaier, "Spatially Coupled Serially Concatenated Codes: Performance Evaluation and VLSI Design Tradeoffs, "submitted to *IEEE Transactions on Circuits and Systems I* (*TCAS-I*): Regular Papers, August 2021.

- Mojtaba Mahdavi, Liang Liu, Ove Edfors, Michael Lentmaier, Norbert Wehn, and Stefan Weithoffer, "Towards Fully Pipelined Decoding of Spatially Coupled Serially Concatenated Codes," in 2021 IEEE International Symposium on Topics in Coding (ISTC), Montreal, Canada, August 2021, pp. 1-5.

- Mojtaba Mahdavi, Muhammad Umar Farooq, Liang Liu, Ove Edfors, Viktor Öwall, and Michael Lentmaier, "The Effect of Coupling Memory and Block Length on Spatially Coupled Serially Concatenated Codes," in *IEEE 93rd Vehicular Technology Conference (VTC)*, Helsinki, Finland, December 2020, pp. 1-7, doi: 10.1109/VTC2021-Spring51267.2021.9448689.

Finally, this thesis concludes with a chapter on outlook and future works.

## 2

### **Digital Baseband Processing**

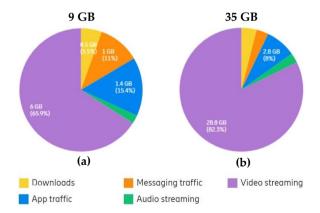

Wireless communication has been experiencing significant growth since its invention, which dramatically has improved the quality of life around the world and the way that people communicate. In 1981, the first generation (1G) of cellular phone systems, e.g., Nordic mobile telephone (NMT), provided a data rate of 1.2 kbps [15]. However, the demand for higher data rate has been increased remarkably over the past decades, especially since multimedia streaming became a normal use case for mobile phones. Figure 2.1 represents the average monthly mobile data traffic per subscription, which is envisioned to increase 4-fold between 2020 and 2026 [1]. It is shown that in 2020, the

**Figure 2.1.** The estimated world average monthly traffic per subscription for different types of applications in (a) 2020, (b) 2026. Source of data/figures: Ericsson Mobility Report [1].

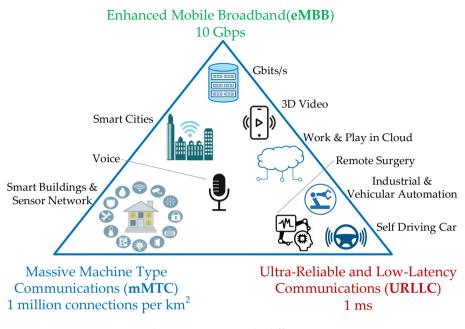

Figure 2.2. Various applications in 5G with different requirements: extreme data rates and large data volumes in eMBB; low energy consumption, extreme coverage, and low-cost devices in mMTC; high availability in URLLC.

video traffic accounts for 66% of all mobile data traffic, while this share is forecast to increase to 82% in 2026.

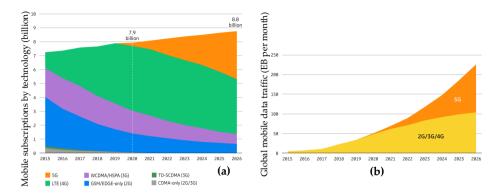

Moreover, new applications set new demands on data-rate, reliability, and latency of the wireless services, pushing forward technology developments [3, 16]. Figure 2.2 illustrates the promised applications in 5G, which are categorized into three groups, enhanced mobile broadband (eMBB) applications [3], massive machine type communications (mMTC) [17], and ultra-reliable and low-latency communications (URLLC) [18]. Examples of such applications are eHealth, autonomous vehicles, connected ambulances, smart cities, smart homes, the Internet of things (IoT), and emergencies [8, 12, 13]. The later one directly affects mobile traffic; in the first 6 months of the COVID-19 pandemic, the mobile traffic grew by 20 percent [1]. As illustrated in Figure 2.3, the total mobile data traffic reached around 51 EB per month at the end of 2020 and it is projected to reach 226 EB per month in 2026 [1].

In order to support these applications and requirements, the 5G standard employs massive MIMO as a key technology, which upgrades the previous wireless standards [2, 5]. It enhances the bounds of access, reliability, per-

Figure 2.3. (a) Number of mobile subscriptions in different technologies, (b) Global mobile data traffic (EB per month). In 2026, 5G will account for an estimated 54% of total mobile data. Source of data/figures: Ericsson Mobility Report [1].

formance, data-rate, and latency limitations. More specifically, a peak data rate of 10 Gb/s and a latency of 1 ms are promised in 5G standard [3]. As shown in Figure 2.3(a), the number of 5G subscriptions is 220 million at the end of 2020, while it is projected to have 3.5 billion 5G subscriptions globally by the end of 2026. It is expected that 54% of world's mobile data traffic will be carried by 5G networks, as depicted in Figure 2.3(b).

This chapter aims to introduce basic concepts and terminologies of wireless communication systems, which are used in the rest of this thesis. First, a general description of wireless communication systems, wireless channel, and transmission technologies is given. Then, massive MIMO systems and corresponding propagation channels are discussed. Lastly, an overview of the massive MIMO baseband processing is presented where the targeted blocks of this thesis are emphasized.

#### 2.1. WIRELESS COMMUNICATION SYSTEMS

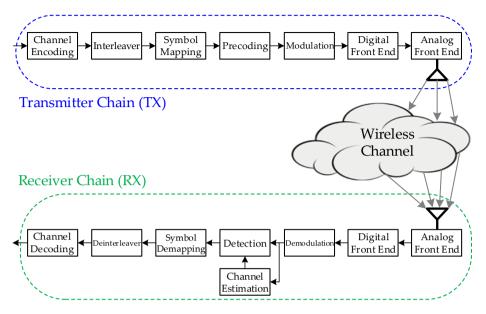

Figure 2.4 illustrates a simplified model of wireless communication systems. At the transmitter (TX) side, the information bits are encoded and mapped to the constellation symbols. These symbols are modulated and then converted to the analog signals to be transmitted over the wireless channel using the antenna. The analog signals are propagated through the atmosphere in the form of electromagnetic waves, and they are received by the antenna at the receiver (RX) side.

The receiver chain performs the inverse transformations on the received

Figure 2.4. A simplified block diagram of wireless communication systems.

data and corrects the errors introduced by the propagation channel and TX/RX chains to extract the transmitted information. To this end, the received signal goes through the analog front-end and is eventually demodulated. Then, the received symbols are detected, demapped, and decoded to obtain an estimate of the transmitted bits. In the detection process, the receiver needs to know the channel state. This can be done by, for example, sending known pilots used to estimate the effects of the propagation channel on the transmitted signal [19, 20].

#### 2.1.1. WIRELESS CHANNEL

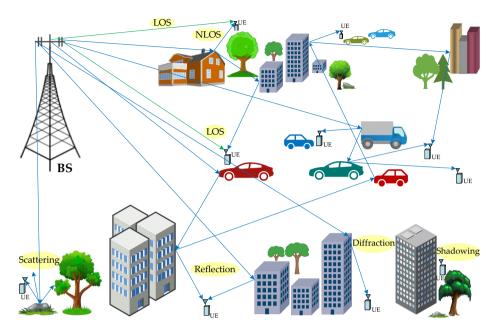

A communication channel is a medium in which the information transmission between the transmitter and receiver occurs. The electromagnetic wave leaves the transmitter antenna, propagates through the channel, and it is picked up by the receiver antenna. On the way from transmitter to receiver, the electromagnetic signal experiences several different effects. First, the signal power is reduced due to path loss in free space propagation. Second, the signal can be reflected, diffracted, and scattered by objects such as buildings, mountains, trees, cars, and rough surfaces, in the environment. This results in multi-path components (MPC) of the transmitted signal, which arrive at the receiver through multiple paths, each with a different delay, phase, and attenuation [21]. This effect is referred to as multi-path propagation, which leads

**Figure 2.5.** Multi-path wireless propagation channel between the base station (BS) and several UEs. Different propagation mechanisms and channel effects are marked.

to the channel being frequency selective [22]. Figure 2.5 shows an example of multi-path wireless propagation channel, which shows different channel effects and propagation mechanisms. Typically, MPCs can be classified into two groups: if there is a direct connection between transmitter and receiver, the path is called as line-of-sight (LOS) otherwise it is a non-line-of-sight (NLOS) path, as shown in Figure 2.5.

The third effect is about the changes in the propagation environment due to the movement of receiver, transmitter, and/or scatterers, which would change the travel time of the signal and, consequently, the perceived frequency of the transmitted signal. This effect is known as the Doppler frequency shift and depends on the relative movement between the transmitter and receiver as well as movements in the environment itself [22]. Another effect that can occur in the channel is shadowing of one or more MPCs of the signal due to obstruction between the transmitter and receiver, caused by the changes in the propagation environment (see Figure 2.5). All the mentioned propagation effects vary over time, resulting in a time-varying frequency-selective channel. The mitigation of such effects at the receiver makes the baseband processing of wireless communication systems a very challenging task. Based upon the received distorted and noisy signals, the receiver estimates transmitted data with as few errors as possible. However, errors can occur if the distortion and noise become too strong, which affects the performance and link reliability. This is usually quantified using the bit error rate (BER), defined as the number of error bits divided by the total number of transmitted bits. Theoretically, the Shannon-Hartley theorem [22] states that an arbitrarily low error rate communication, using an average received signal power of *S* through a communication channel subject to additive white Gaussian noise (AWGN) of power N, can be achieved if the data rate is less than

$$C = B \log_2\left(1 + \frac{S}{N}\right). \tag{2.1}$$

In this equation, *C* is the channel capacity measured in bit per second (bps), *B* is the bandwidth measured in Hz, and S/N is the received signal-to-noise power ratio (SNR).

It can be seen in (2.1) that capacity, and therefore data-rate of a wireless system can be increased by either using more bandwidth or increasing the signal power. Due to the logarithmic dependency, the later option provides only a limited gain. In addition, the transmitted power is faced by practical limitations and also it has to satisfy the regulatory constraints defined in the standards. For these reasons, increasing the bandwidth has been the preferred choice to increase capacity in the cellular standardization process; the bandwidth was increased from 200kHz in the 2G standard to 100 MHz in the 4G standard.

#### 2.1.2. WIRELESS TRANSMISSION TECHNOLOGIES

As shown in (2.1), a straightforward way of increasing the data rate and capacity is to increase the communication bandwidth; a wide frequency band allows more data to be transmitted at any time. However, a larger bandwidth increases the implementation complexity of the system, since the channel becomes increasingly frequency selective, and thus affects signals at different frequency bands differently. Moreover, the spectrum is a regulated and very expensive resource, meaning that simply scaling the bandwidth is not an economic solution. Therefore, finding methods to increase the data rate in a limited spectrum, i.e., improving the spectral efficiency, becomes critical. This section describes the key technologies, which are used in the wireless communication systems to mitigate the mentioned issues.

#### **ORTHOGONAL FREQUENCY DIVISION MULTIPLEXING (OFDM)**

In order to reduce the frequency selectivity, the frequency division multiplexing (FDM) method can be used [22]. The key idea is to divide the bandwidth into several non-overlapping sub-bands (i.e., subcarriers), which carry

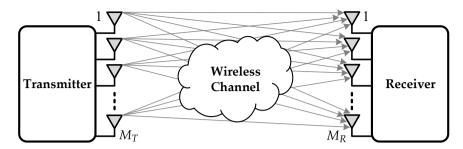

**Figure 2.6.** A MIMO wireless system with  $M_{\rm T}$  transmit antennas and  $M_{\rm R}$  receive antennas.

different signals, corresponding to different parts of the data. In this way, the frequency response of each sub-band is flattened, thus reducing the complexity of channel equalization. Orthogonal frequency-division multiplexing (OFDM) is one of the FDM techniques, in which the subcarriers are chosen to be orthogonal to each other [22]. The orthogonality leads to no interference among subcarriers under ideal conditions and, consequently it does not require inter subcarrier guard bands. Therefore, OFDM can improve the spectral efficiency of the communication systems by parallel transmission using frequency-overlapping subcarriers. Another advantage of OFDM is that, OFDM demodulation and modulation can be efficiently implemented using fast Fourier transform (FFT) and inverse FFT (IFFT) at the receiver and transmitter, respectively [23].

The signals in OFDM systems may experience inter-carrier interference (ICI), since the orthogonality of the subcarriers may be destroyed by multipath propagation and hardware imperfections such as carrier-oscillator mismatch. The effect of ICI and inter-symbol interference (ISI) can be reduced a by extending each OFDM symbol with a cyclic prefix (CP) with a length greater than the channel delay spread [24].

#### MULTIPLE-INPUT MULTIPLE-OUTPUT (MIMO)

The spatial domain provides the possibility to increase the data rate and link reliability. Multiple-input multiple-output (MIMO) is a technology which exploits the spatial domain by employing multiple antennas at the transmitter and receiver [25]. MIMO has been incorporated in many wireless communication standards such as IEEE 802.11ac, LTE, and LTE Advanced (LTE-A) [26]. In these standards, LTE-A supports the highest number of antennas at the transmitter and receiver, i.e., up to  $8 \times 8$ . In modern wireless standards such as 4G and 5G, the MIMO and OFDM technologies are jointly deployed, which is termed as a MIMO-OFDM system.

In general, there are three MIMO transmission techniques and each can offer a specific property [26]. The first one is spatial multiplexing, which splits and performs transmission of a signal over several antennas to increase the communication link capacity and the overall data-rate without requiring additional bandwidth. Second, MIMO can be used for spatial diversity to transmit the same signal over several beams increasing resilience to fading and other propagation effects, e.g., when the UE experiences low SNR due to deep fading. Third, MIMO can offer beam steering and electronically guide the signal directivity by controlling the propagating phase over multiple antennas. This enables communication with several UEs within the same time and frequency resources (multi-user MIMO).

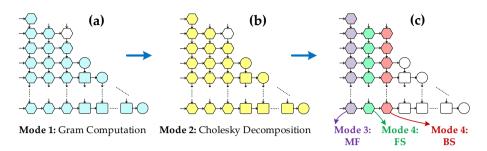

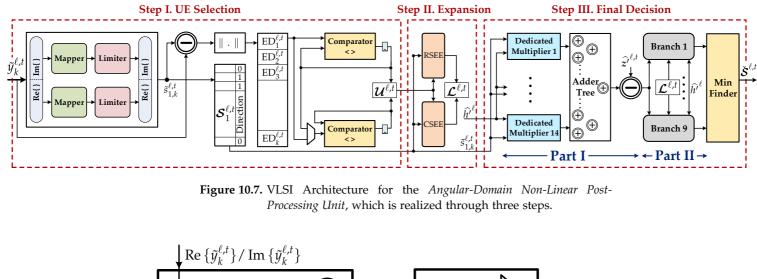

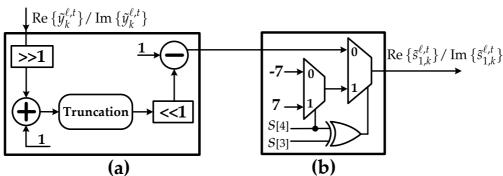

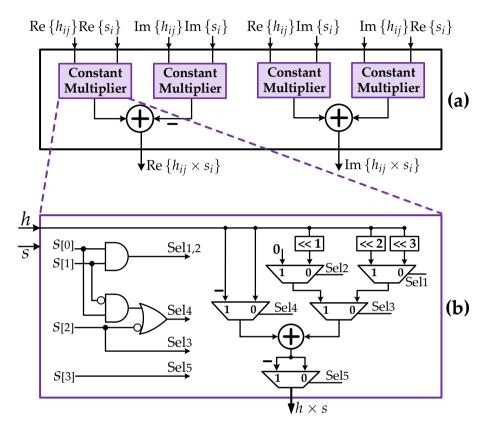

Transmission of multiple streams simultaneously through the wireless channel would result in mixing of the signals at the receiver side. Therefore, additional and complicated signal processing is required to separate the data streams, which is generally called MIMO processing.