#### Development of new characterization techniques for III-V nanowire devices

Persson, Olof

2017

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

Persson, O. (2017). *Development of new characterization techniques for III-V nanowire devices*. [Doctoral Thesis (compilation), Department of Physics]. Lund University, Faculty of Science, Department of Physics, Division of Synchrotron Radiation Research.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Development of New Characterization Techniques for III-V Nanowire Devices

Olof Persson Doctoral Thesis 2017

Division of Synchrotron Radiation Research

Department of Physics

Lund University

Front cover: Artistic interpretation of the normalized differential conductance along a contacted GaSb-InAs nanowire.

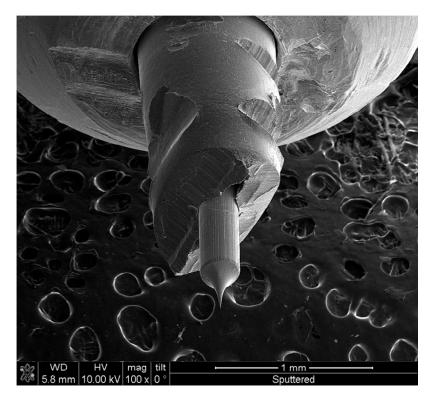

Back cover: Slightly bent W-tip.

#### © Olof Persson

Division of Synchrotron Radiation Research Department of Physics Lund University

ISBN: 978-91-7753-128-9 (print) ISBN: 978-91-7753-129-6 (pdf)

Printed in Sweden at E-huset, Lund University Lund 2017

"I'd like to congratulate myself, and thank myself,

and give myself a big pat on the back"

– Dee Dee Ramone

### **Abstract**

This dissertation presents the new methods and techniques developed to investigate the properties of nanowires (NWs) and NW devices and the results obtained using these methods. The growth and characterization of NWs have become a large research field because NWs have been shown to improve the properties of many semiconductor applications such as transistors, solar cells, and light emitting diodes. The structural composition, optical properties, and electric characteristics of NWs and NW devices are affected by effects at the atomic level. The surface of NWs plays a crucial role when it comes to these characteristics because of the large surface to volume ration of the NW structures. This makes the characterization of these structures, at the atomic level, a key factor, for understanding the underlying mechanisms, and for the development of even more suitable structures. Here, the composition of III-V semiconductor materials and the electronic properties of III-V semiconductor NWs are investigated using scanning tunneling microscopy (STM) and X-ray photoelectron spectroscopy (XPS).

A new method for studying contacted NWs on insulating substrates with STM is described, and the results from investigations of InAs-GaSb Esaki diode NWs are presented. The ability to study the NW side facets with STM while at the same time being able to apply a potential along the NW makes it possible to connect the device performance with the NW characteristics found with the STM.

The conductivity of up-standing, as-grown NWs is also measured with an STM using the novel technique called top contact mode. The method is used to evaluate, the Schottky barrier height of the Au-GaAs interface in GaAs NWs, and the conductivity of InP and InAs NWs. This method makes it possible to measure the electric conductivity of the NWs without any additional device fabrication, making it more reliable due to the good ohmic electrical contacts established to the NW. It also, in contrast to conventional methods, enables well-controlled surface treatment of the NW side facets which is used to show how surface oxides influence NW conductance.

XPS and the more penetrating hard X-ray photoelectron spectroscopy (HAXPES) are used to evaluate the homogeneity and the growth of HfO<sub>2</sub> films on InAs as well as the mechanism behind the self-cleaning effect of the InAs native oxide.

This information is especially important for the continued work on semiconductor transistors where the  $HfO_2$  is one of the best candidates to be used as the gate oxide and where the interface between the oxide and semiconductor is crucial for device performance.

## Populärvetenskaplig sammanfattning

Nanoteknik är i grunden förmågan att kunna påverka material ner på dess mest grundläggande nivå, d.v.s. atomär nivå. Ett sådant vitt begrepp gör att väldigt mycket kan beskrivas som nanoteknik vilket i sin tur kan medföra en del förvirring kring vad nanoteknik egentligen är. Ett sätt att se på det är helt enkelt att nanoteknik är en del av den naturliga utvecklingen av naturvetenskapen där ökad förståelse leder till mer precisa verktyg som i sin tur leder till ökad förståelse och så vidare. Själva ordet nano syftar till nanometer vilket i sin tur betyder miljarddels meter. Som jämförelse har en vanlig hudcell en diameter på ungefär 30000 nanometer. På en nanometer får c:a tre atomer i rad plats.

Halvledare är material som leder ström, fast dåligt. Deras ledningsförmåga kan dock påverkas permanent genom s.k. dopning där orenheter tillförs materialet, eller tillfälligt genom att utsätta halvledarna för elektriska fält. Dessa egenskaper visade sig vara perfekta för utvecklingen av elektriska komponenter och halvledarmaterialen är grunden till bl.a. lysdioder (populärt kallat LED-lampor) och många sorters solceller. Halvledarmaterialens egenskaper är också en av de grundläggande orsakerna till att datorutvecklingen tog sådan fart som den gjorde. Genom att byta ut de klumpiga radiorören som användes i dåtidens datorer mot transistorer gjorda av halvledarmaterial kunde flera fördelar uppnås. Datorerna blev driftsäkrare, de blev mindre, drog mindre ström och framförallt kunde de utföra beräkningar snabbare. Antalet transitorer i en dator är direkt kopplat till hur snabb den är. Genom att göra transistorerna mindre och mindre (så att antalet i en dator ökar) så kan allt snabbare datorer tillverkas. Det är denna förminskning som har drivit datorutvecklingen i mer än ett halvt århundrade men nu är transistorerna så små att de inte kan bli mycket mindre. Problemet är att när vi kommer ner på nanonivån så börjar material uppföra sig annorlunda än vad vi är vana vid, de får andra egenskaper. Elektroner börjar tunnla, vilket innebär att strömmar kan uppstå där de klassiskt sett inte skulle kunna finnas. För att beskriva vad som händer kan man inte längre förlita sig till den klassiska fysiken utan istället måste kvantfysikens lagar tas i beaktning. För att föra utvecklingen framåt kan vi då istället vända på problemen som uppstår på nanoskalan och använda de nya förutsättningarna till vår fördel. För att kunna göra det krävs en ökad förståelse och det är där som vår forskning kommer in i bilden.

I den här avhandlingen beskrivs den forskning vi har bedrivit för att öka förståelsen kring vad som händer med halvledarkomponenter när de krymps ner till nanoskalan. Mycket fokus har lagts på att utveckla verktyg och metoder med vilkas hjälp experiment kan utföras. De två huvudsakliga verktygen har varit svepspetsmikroskopi och fotoelektronspektroskopi med vilka speciella strukturer kallade nanotrådar i huvudsak har undersökts. Nanotrådarna vi har undersökt är små pinnar gjorda av halvledarmaterial som är runt 1  $\mu$ m långa (dvs i storleksordningen som en bakterie, och mycket mindre än en mänsklig cell). Med rätt förhållanden kan man få nanotrådar att växa på halvledarplattor bara man tillför rätt gaser vid rätt temperatur och tryck. Genom noggranna beräkningar och experiment kan man styra hur nanotrådarna växer. Det går att skapa alla möjliga strukturer, med atomär precision, t ex solceller, lysdioder eller transistorer.

Vi har utvecklat en ny metod att använda svepspetsmikroskopi för att undersöka ytan hos nanotrådar medan de har varit utsatta för olika elektriska spänningar. Vi har även utvecklat en annan metod för att kontaktera nanotrådar och mäta hur strömmen varierar genom dessa beroende på vilken elektrisk spännig de utsätt för. Båda metoderna har utvecklats för att det behövs mer kunskap om hur, och framför allt varför, nanotrådar beter sig som de gör.

Fotoelektronspektroskopi har framför allt använts för att belysa frågor kring hur tunna oxidlager kan skapas och hur deras sammansättning ser ut. Dessa oxidlager spelar en framträdande roll i utvecklingen av morgondagens transistorer.

## Preface & List of papers

This doctoral thesis presents my contribution to our work on developing new and utilizing existing techniques to evaluate nanowires and nanowire devices over the last five years. Here, the techniques and methods developed during this time span are explained. The underlying theory is presented as well as the results which have been published in scientific journals. Parts of this work have previously been presented in my licentiate thesis "Surface studies of III—V nano devices". This doctoral thesis is based on the following papers, which will be referred to in the text by their Roman numerals.

#### Paper I

## Scanning Tunneling Spectroscopy on InAs-GaSb Esaki Diode Nanowire Devices during Operation

O. Persson, J.L. Webb, K. A. Dick, C. Thelander, A. Mikkelsen, and R. Timm *Nano Letters*, **15**, 3684 (2015)

I was involved in the planning of the experiment and responsible for the development of the techniques used as well as the measurements. I analyzed the data and wrote the manuscript.

#### Paper II

### High Resolution Scanning Gate Microscopy Measurements on InAs/GaSb Nanowire Esaki Diode Devices

J. L. Webb, <u>O. Persson</u>, K. A. Dick, C. Thelander, R. Timm, and A. Mikkelsen *Nano Research*, **7**, 877 (2014)

I was involved in the planning of the experiment as well as the measurements and I took part in the discussions about the manuscript.

#### Paper III

# Current-Voltage Characterization of Individual As-Grown Nanowires using a Scanning Tunneling Microscope

R. Timm, <u>O. Persson</u>, D. L. J. Engberg, A. Fian, J. L. Webb, J. Wallentin, A. Jönsson, M. T. Borgström, L. Samuelson, and A. Mikkelsen

Nano Letters, 13, 5182 (2013)

I was involved in the planning of the experiment, measuring the data, and development of the technique. I analyzed parts of the data and contributed to writing the manuscript.

#### Paper IV

# The Effect of Surface Oxide and Wurtzite/Zinc blende Interfaces on the Conductivity of InAs Nanowires

O. Persson, L. Kral, S. Lehmann, C. Thelander, A. Mikkelsen, and R. Timm

In manuscript

I was involved in the planning of the experiment and responsible for the measurements. I analyzed the data and wrote the manuscript.

#### Paper V

## Strong Schottky Barrier Reduction at Au-Catalyst/GaAs-Nanowire Interfaces by Electric Dipole Formation and Fermi-level Unpinning

D. B. Suyatin, V. Jain, V. A. Nebol'sin, J. Trägårdh, M. E. Messing, J. B. Wagner, <u>O. Persson</u>, R. Timm, A. Mikkelsen, I. Maximov, L. Samuelson, and H. Pettersson

*Nature Communications*, **5**, 3221 (2014)

For the nanowires described as series B, I was involved in the planning of the experiment, measuring the data, and development of the technique. I analyzed the data for series B and took part in discussions about the manuscript.

#### Paper VI

# Interface Characterization of Metal-HfO<sub>2</sub>-InAs Gate Stacks using Hard X-ray Photoemission Spectroscopy

O. Persson, E. Lind, E. Lundgren, J. Rubio-Zuazo, G. R. Castro, L.-E. Wernersson, A. Mikkelsen, and R. Timm

*AIP Advances* **3**, 072131 (2013)

I was involved in the planning of the experiment as well as the measurements. I analyzed the data and wrote the manuscript.

#### Paper VII

## Self-cleaning and Surface Chemical Reactions during HfO<sub>2</sub> Atomic Layer Deposition on InAs

R. Timm, A. Head, S. Yngman, J. V. Knutsson, M. Hjort, S. McKibbin, A. Troian, <u>O. Persson</u>, S. Urpelainen, J. Knudsen, J. Schnadt, and A. Mikkelsen

In manuscript

I took part in the measurements and discussions about the manuscript.

## Abbreviations and Symbols

III-V material comprised of one group III-element and one group

V-element in the periodic table

A\* Richardson constant

AHC atomic hydrogen cleaning ALD atomic layer deposition APT atom probe tomography

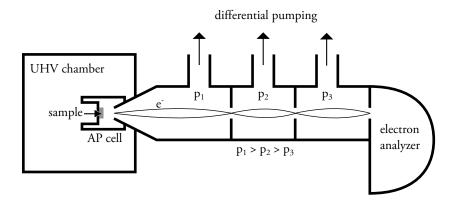

APXPS ambient pressure X-ray photoelectron spectroscopy

Å angstom

CB conduction band CBE conduction band edge

CMOS complementary metal oxid semiconductor

$\begin{array}{lll} CU & controler \, unit \\ E_i & energy, \, initial \, state \\ E_F & Fermi \, energy \\ E_f & energy, \, final \, state \\ E_G & band \, gap \, energy \\ E_K & kinetic \, energy \end{array}$

EDX energy dispersive X-ray spectroscopy

ESRF European synchrotron radiation facility

FET field effect transistor

H\* atomic hydrogen radical

HAXPES hard X-ray photoelectron spectroscopy

$\begin{array}{ll} I_S & \text{saturation current} \\ IMFP & \text{inelastic mean free path} \\ I_T & \text{tunneling current} \\ K & \text{decay length} \end{array}$

LDOS local density of states

LED light emitting diod

M<sub>i,f</sub> tunneling matrix element

MBE molecular beam epitaxy

MOSFET metal oxide semiconductor field effect transistor

MOVPE metal organic vapor phase epitaxy

NW nanowire

SEM scanning electron microscope SGM scanning gate microscopy SPM scanning probe microscopy

STM scanning tunneling microscope/microscopy

T tunnel probability

$T_{\rm C}$  congruent evaporation temperature TEM transmission electron microscope

UHV ultra high vacuum VB valence band

VPE vapor phase epitaxy

VT tip bias

XPS X-ray photoelectron spectroscopy

$\epsilon_0$  vacuum permittivity

κ relative dielectric constantλ inelastic mean free path

$\begin{array}{ll} \varphi & \text{work function} \\ \varphi_{bi} & \text{built in potential} \\ \varphi_{Bn} & \text{barrier height} \\ \chi & \text{electron affinity} \end{array}$

### Acknowledgements

There are of course many people who have helped and guided me in my work during the timespan of this thesis, and I hope that I remember to acknowledge you all.

First of all, I would like to thank my supervisor, Anders, for all your support and positive attitude to my various ideas, and also of course for everything you have taught me. I can not stress enough how glad I am that I have had such a positive and encouraging supervisor. Also, your ability to make sense of even the most convoluted and confusing manuscripts I've written so that other people also can understand them is much appreciated.

My co-supervisor Rainer with whom I even shared an office when I started at the division. You have such an approachable and kind personality. You are most probably the person who has taught me most about all the various experimental techniques and the theory behind them. We have also been on many beam-times together, and I must thank you for all of your candy that I have eaten. You have also been a tremendous help when it comes to my writing and presenting material at various conferences.

Martin and Johan, you have taught me everything I know about practical STM work (except for everything Anders and Rainer taught me), thank you. You, together with Erik M., are for sure the silliest physicists I know, keep it up.

There have been students helping me these past five years. Jalil, Jovana, and Lena, you all kept on working even though it did not always go according to plans.

Thank you Estephania. If something is broken, one can always count on your help.

Everyone else who has been in the STM labs working with me, thank you.

All my former office mates, Erik M., Elin, Natalia, Olesia, Erik M., Sophie, Chu chu, and Andrea. We have shared many laughs, disappointments, and stories.

Thank you, Sara. I think discussing things, not necessarily strictly connected to surface science all the time, is a good way of not losing track of what is important here in life.

Patrik, thank you for all the support related to me getting money from the university. You have helped a lot. And also, thank you for your stories and gossip.

It has been great fun and very educational working together with you, Elisabeth. I think we have shared many eureka moments, teaching these last five years.

The I311 people and especially Karina. I do not want to recall all the phone calls I have made in the middle of the night to you guys. Thank you for being so understanding and helpful.

Electrical measurements, device fabrication, and general STM/AFM stuff, thank you, Jim, I've learned a lot.

None of my work would have been possible without samples to investigate. Thank you, Claes, especially for your very interesting Esaki diodes that really helped us when starting with the STM on device-measurements. Thank you, Kristian and Sebastian, as well for the various samples that we have destroyed. The collaboration with Lars-Erik and Erik and the rest of your group with all the NW-wrap gate related samples.

All the people at solid state physics and especially the clean room staff for all the equipment training.

I also have to thank the rest of my co-workers at the department of synchrotron radiation research. I strongly feel that there are a community and warmth at the division which may not be that common in the research world. Keep it up.

Writing this thesis would not have been possible if it was not for my parents and my in-laws and all the help with taking care of Stina afternoons and evenings. Thank you.

And finally Rebecca for your support!

### Contents

| 1 | Intr | oduction                                     | 1  |

|---|------|----------------------------------------------|----|

|   | 1.1  | III-V semiconductors                         | 3  |

|   | 1.2  | Semiconductor doping                         | 4  |

|   | 1.3  | Surfaces                                     | 6  |

|   | 1.4  | Basic devices                                | 7  |

|   | 1.5  | Aim and outline of this thesis               | 10 |

| 2 | Nar  | 13                                           |    |

|   | 2.1  | Nanowire growth                              | 14 |

|   | 2.2  | Nanowire doping                              | 16 |

|   | 2.3  | Metal-semiconductor electrical contacts      | 17 |

|   | 2.4  | Devices                                      | 20 |

|   | 2.5  | Atomic layer deposition & high-k dielectrics | 21 |

|   | 2.6  | Nanowire cleaning                            | 23 |

| 3 | Ехр  | 25                                           |    |

|   | 3.1  | Scanning tunneling microscopy                | 25 |

|   |      | 3.1.1 Electron tunneling                     | 27 |

|   |      | 3.1.2 Tunneling current                      | 28 |

|   |      | 3.1.3 Operation                              | 29 |

|   |      | 3.1.4 qPlus mode                             | 31 |

|   | 3.2  | Scanning tunneling spectroscopy              | 35 |

|   |      | 3.2.1 Variable z-mode and broadened $dI/dV$  | 36 |

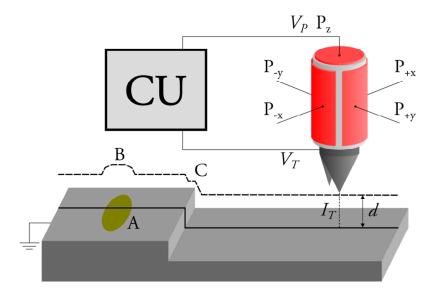

|   | 3.3  | Scanning probe microscopy on NW devices      | 39 |

|   | 3.4  | STM top contact mode                         | 43 |

|   | 3.5  | X-ray photoelectron spectroscopy             | 47 |

|   |      | 3.5.1 Theory                                 | 48 |

|   |      | 3.5.2 Inelastic mean free path               | 50 |

|   |      | 3.5.3 Analyzing HAXPES spectra               | 51 |

|   | 3.5.4 Ambient–pressure XPS     | 53 |

|---|--------------------------------|----|

| 4 | Concluding remarks and outlook | 55 |

| 5 | Bibliography                   | 57 |

| 6 | Summary of papers              | 63 |

### 1 Introduction

It is hard to imagine how our modern world would look without the use of semiconductor materials. The fact that a modern computer now fits in your hand (smartphone) is all thanks to semiconductors. A computer consists, at its core, of billions of small semiconductor devices called transistors. Semiconductors are also the key material in solar cells, light-emitting diodes (LEDs) and many other applications today.

During the timespan of this thesis I have, together with my colleagues and collaborators, studied the properties of semiconductor devices at the nanoscale. Nanoscience is the description and understanding of the novel properties that different material systems exhibit when they are shrunk into the nanometer (nm) scale. These new properties give rise to semiconductor devices with completely new scopes. Due to the small dimensions of these structures, classical physics are not enough to describe their electronic properties. The laws of quantum mechanics have to be taken into account to be able to explain and understand how and why they work. The laws of quantum mechanics state that all matter can mathematically be described, not only as particles but also as waves, and that classical physics is in fact merely a statistical result of quantum mechanics, at larger scales.

There are however many challenges associated with the making of nanoscale semiconductor devices. For example, at the atomic level, it is almost inevitable not to get imperfections at the interface between different materials which will deteriorate the performance of many devices. A very promising semiconductor material shape called the semiconductor nanowire (NW) has been shown to circumvent many of these challenges, and it has also been shown to improve upon the performance (switching speeds of transistors, efficiency of solar cells and LEDs) of many semiconductor devices when integrated as an active part.

In this thesis, I have focused on revealing and understanding the properties of semiconductor NW structures and some of their applications, solar cells, LEDs, and transistors. To do this new methods and techniques had to be developed to enable us to couple the atomic structure of NWs with their electronic behavior. Much focus has been put into investigation of individual NWs and the development of techniques to enable us to couple the individual NW surface

structure with the NW electrical characteristics. The mere fact that NWs are so small in size makes this challenging.

The two main techniques used to conduct the research presented in this thesis are scanning tunneling microscopy (STM) and X-ray photoelectron spectroscopy (XPS). Both are so-called surface sensitive techniques highlighting the fact that they only analyze the outmost atomic layers of the sample studied. Using various methods and tricks, we utilize these surface sensitive techniques to also, in various ways, probe deeper into our samples to reveal further information.

In this introduction chapter, an overview of the semiconductor world will be given with a focus on the areas which are most important for my research.

#### 1.1 III–V semiconductors

All the results presented in this thesis are from research and experiments on III–V semiconductor material. Semiconductor materials have higher electrical conductivity than insulators but lower than metals. This property in itself did not make semiconductor materials especially interesting from an electronic device maker's point of view, but it was the ability to change the conductivity in a controlled manner of these materials by introducing minute amounts of other materials, so-called dopants, that did [1].

The predominantly used material in the semiconductor industry was, in the beginning, Ge which later got replaced by Si [2]. One of the major reasons for the replacement is because Si naturally forms a thin layer of insulating SiO<sub>2</sub> which is stable and can have very few interface defects which are highly useful in the industry. The increasing demand for faster electronics and more efficient LEDs and solar cells has led to a demand for materials with more suitable properties. New semiconductor materials are needed with different band gap size, charge carrier mobility, carrier generation and recombination, and direct or indirect band gap. Both Ge and Si are from the fourth group of the periodic table. By combining materials from the third and fifth group in the periodic table new semiconductor materials become available, hence the name III–V semiconductors. These materials can then be designed so that they satisfy many of the desired properties.

The use of III–V semiconductors has two main reasons. In the case of transistors, it is the high charge carrier mobility which makes them ideal for high switching speeds [3]. For LEDs, it is the direct band gap of many III–V semiconductors [4] which allows for fast electron-hole recombination and thereby good electricity-to-light efficiency, and vice versa for solar cells. By using more than one element from group three and group five and controlling the ratio between the same (e.g.  $Ga_xIn_{1-x}As_yP_{1-y}$ ), tailoring of the band gap and lattice constant of the resulting material is possible.

The use of III–V semiconductors in the industry is limited, especially in the complementary metal oxide semiconductor (CMOS) industry where Si still is the predominant material [5]. The technology needed to use III–V semiconductor materials is less explored and thereby more expensive than the standard Si technology. The materials themselves are more expensive, and the integration with the Si technology is challenging due to the distinct differences in the industrial processing of Si and III–V semiconductors [6]. When combining Si and III–V semiconductors, anti-phase domains can arise which leads to the formation of defective material. The different domains are created when III–V semiconductor

material growth is initiated on two different Si atomic planes with only one atom in height difference [7]. Where the domains meet defects arise.

The difference in lattice constant (physical dimensions of the smallest unit cell of a crystalline material) between most III–V semiconductors and Si also creates integration problems. A difference in lattice constant between two materials will lead to strain in the interface between the same, which in turn leads to dislocations which will deteriorate the performance of most devices made this way. The lattice constant of the semiconductor at the interface to the Si can, in some cases, be tailored to match the lattice constant of Si. There is, however, an additional problem with integration between Si and III-V semiconductors, and that is the difference in the coefficient of thermal expansion. Two materials with different coefficients will expand or contract to different degrees when exposed to temperature variation which will also lead to dislocations at the interface between the two materials.

By growing semiconductor nanowires (NWs) – self-assembling, rod-shaped structures – many of these limitations can be overcome, and the realization of more complex III–V semiconductor-Si devices can be realized [8, 9]. Typical NWs have a width of 10 to 100 nm and a length of 1 to 10 µm. NWs can accommodate the strain caused by growing materials with different lattice constants due to the small cross-section area and by effect large surface to volume ratio. The surface of the NW accommodates the strain caused by the lattice mismatch at the NW–substrate interface, allowing an elastic deformation to take place with no dislocations forming at the interface. This enables NWs to handle much more strain than an ordinary bulk structure of the same materials could. Since NWs grow separately from each other, there will never be any domains with different phases. Thus, they are ideal for implementing III–V materials with Si technology [7, 10].

### 1.2 Semiconductor doping

Doping plays a crucial role when it comes to semiconductor device production and operation. Doping is the process of introducing impurities into a semiconductor material resulting in either an excess of electrons or holes. Epitaxially grown semiconductor materials without any *added* impurities are said to be nominally undoped (or intrinsically doped), because a small amount of dopants will always be present. Introduced dopant atoms exchange position with an atom in the semiconductor lattice. The dopant either has less (acceptor) or more (donor) valence electrons compared to the substituted atom. Donors create an excess of electrons in the semiconductor (*n*-doping), fig 1.1(a), and acceptors

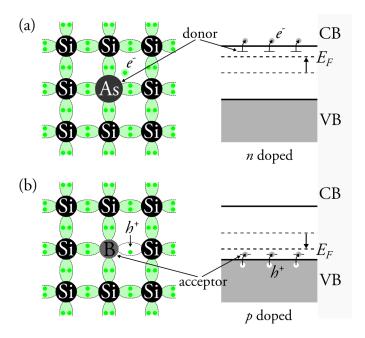

**Figure 1.1:** Schematic representation of doping of semiconductors. (a) *n* doping of Si with As. The As atom has five valence electrons, one too much to fit in the Si lattice. The extra electron is "donated" to the Si conduction band, raising the Fermi level. (b) *p* doping of Si with B. The B atom, on the other hand, has only three valence electrons, one too little to fit in the Si lattice. The B "accepts" an electron from the Si, creating a mobile hole in the Si valence band, lowering the Fermi level.

create an excess of free electron holes (*p*-doping), fig 1.1(b). Dopants have an energy level which either lies just beneath the conduction band (donor) or above the valence band (acceptor). The energy difference between the dopant level and the band edge is typically so small that, at room temperature, the dopants are ionized.

The crucial role of doping in device making is that it shifts the Fermi level (the hypothetical energy level that has a 50% chance of being occupied by an electron, at thermal equilibrium) of the semiconductor. By introducing electron states close to the conduction band, the Fermi level is raised in that material and vice versa, fig 1.1. In thermodynamic equilibrium, the Fermi level of a system has to be constant which means that the valence- and conduction band of differently doped semiconductors have to bend if brought into contact with each other. This is utilized in almost all semiconductor devices, fig 1.2.

#### 1.3 Surfaces

The properties of the surface of a material are in some cases more important and interesting than the properties of the bulk of the material. Heterogeneous catalysis is a classic example. It is a process where a chemical reaction is facilitated between reactants in one phase by a catalyst in another. Typically the reactants are in gas or liquid phase, and the catalyst is in solid phase. For a solid catalyst, it is only the outermost atoms of the whole catalyst material that are interesting. It is only these atoms and their properties that govern the mechanisms involved in the catalytic reaction.

In electronics devices based on crystalline materials, the surfaces are seen as irregularities. In the ideal case of an infinite, periodic crystal, the electrons have well defined allowed energy bands. A surface of a material breaks this periodicity in one dimension giving rise to new energy states which are allowed in that dimension. The notion of an infinite crystal is, of course, absurd in real life, but the approximation holds for most crystals since the number of bulk atoms in relation to surface atoms is so large. The bulk states outnumber the surface states to such a degree that the surface states effects are negligible. At the nanoscale, though, this approximation breaks down as the ratio between bulk and surface atoms gets smaller and smaller when shrinking the size of the devices. This is one of the major challenges when trying to understand and design nanoscale devices since the smaller you make your device, the more your material properties will be determined by surface effects and differ from the properties of the same material in bulk form. At the surface of crystalline materials, the atoms can change their arrangement compared to the bulk to lower their potential energy. This is called reconstruction. The unit cell of a stable surface reconstruction of Si(111), imaged with an STM in 1983 by G. Binnig et al. [11], is, for example, seven times longer and much more complex than the unit cell of the bulk structure.

Since the surface plays such a large part when it comes to determining the properties of material at the nanoscale, it is of utmost importance to be able to investigate and characterize surfaces and their properties. Once understood, the effects of the surface properties can not only be minimized but potentially utilized to give rise to new material properties which are then also structure based.

#### 1.4 Basic devices

The applications in which III–V semiconductor materials are utilized to improve the performance are growing every year. Our research is focused on increasing the understanding of how and why these new applications work. There are three general types of semiconductor devices which demonstrate the basics for these applications. The devices are: 1) the light emitting diode (LED), 2) the photovoltaic cell, commonly named solar cell, and 3) the transistor. The basic working principles for these devices will be described in this section.

The building block of all these devices is the p-n junction which consists of two differently doped parts where one (n) has an excess of free electrons, and the other part (p) has a deficit. At the junction between these parts, the electrons will diffuse from the n-part with an excess of electrons into the p-part, creating a so-called depletion region. This will create a local electric field (the built-in potential) over the depletion region which in turn will facilitate any flow of electrons through the p-n junction in the p-to-n direction.

In fig 1.2 the band diagram of the central area of an LED, a solar cell, and a metal oxide semiconductor field effect transistor (MOSFET) are depicted. A band diagram is a simplification in two dimensions showing the allowed energies for the electrons in the specific system. An ideal semiconductor (at 0 K) has two bands which are important for its electronic behavior, the valence- and conduction band, with energy states electrons can occupy. Between these two bands, there is the band gap without any allowed energy states. The energy states in the valence (lower) band are all filled, and all the states in the conduction (top) band are empty. Since all the states are occupied in the valence band, the electrons can not move, and no flow of electrons (electric current) is possible. For an electrical current to be possible, an electron first has to occupy a state in the conduction band. This can be done by absorbing energy, typically from heat (if the temperature is above 0 K), or from incoming light.

The p-n junction is the most important part in both the LED, fig 1.2(a), and the solar cell, fig 1.2(b). In the LED, a potential is applied across the p-n junction, and charge carriers (negative electrons or positive electron holes) flow into the depletion region where a fraction of the electrons and holes recombine, emitting photons. The efficiency of the LED (luminous efficacy: the ratio of luminous flux to power) depend on the amount of charge carriers that recombine and emit a photon, and it can be up to one order of magnitude higher than for standard incandescent light bulbs [12]. The emitted photons from an LED will have the

Figure 1.2: Energy band diagrams of three common (idealized) semiconductor devices. In (a) the LED is shown. By applying a bias  $(V_{on})$ , the built-in potential of the depletion region is counteracted, and the electrons  $e^c$  and holes  $h^+$  can diffuse into the depletion region and recombine emitting photons with energy hv corresponding to the band gap energy  $E_G$ . In (b) a solar cell is shown. Electrons are excited by incoming photons, with energy  $hv > E_G$ , creating electron-hole pairs. The charge carriers are accelerated by the built-in potential, in the depletion region, and reach the contacts on either side. The highest theoretical bias that can be extracted  $(V_{ext})$  from a single p-n junction is equal to the difference between the conduction band edge at the n-contact and the valence band edge at the p-contact. Greater bias can be achieved by connecting several solar cells in series. In (c) a metal oxide semiconductor field effect transistor (MOSFET), in this case with a p-doped channel, is shown. A positive potential at the metal gate  $(V_{on})$  will lead to an inversion layer of electrons in the semiconductor at the interface to the gate oxide. This creates a conducting layer between the n-doped source and drain, turning the transistor "on".

energy, hv, corresponding to the band gap energy,  $E_G$ , of the semiconductor material from which it is made, fig 1.2(a). An LED made of one single semiconductor material will hence emit light with a highly defined wavelength. For lighting applications where white light, with high color rendering index, is required this is far from ideal. LED-lamps bought in stores today solve this problem by using a blue LED in combination with a phosphorous coating, known as YAG, which absorbs some of the blue light and emits yellow through fluorescence [13]. This will produce white light with low color rendering index. With careful engineering using more complex designs than the standard p-n junction and different semiconductor materials, LEDs with higher color rendering index can be achieved [14]. These LEDs are able to emit photons with wavelengths in both the blue, green, and yellow spectra which also give the LEDs a higher luminous efficacy since they do not lose any energy from conversion in the YAG coating.

The photovoltaic cell is in many ways the opposite of the LED. Instead of generating photons via electron–hole recombination, electron–hole pairs are generated via absorption of photons. A photon with energy  $hv > E_G$  can excite an electron from the valence band into the conduction band. These charge carriers, if generated in the depletion region, are then separated by the built-in potential creating a flow of charges, an electric current, fig 1.2(b). Here the different material properties of III–V semiconductors, as well as more elaborate designs, can also be utilized to construct more efficient photovoltaic cells [15, 16]. A solar cell comprised of a single semiconductor material will absorb photons with energies  $hv > E_G$  but all the energy above  $E_G$  will be lost as heat as the electron relaxes down to the conduction band edge. Also, all photons with energies  $hv < E_G$  will not be absorbed. By combining semiconductor materials with different band gaps, this problem can be circumvented to a larger degree, and the wide spectrum of photon energies in the sun light can be harvested more efficiently.

Arguably the most important electronic component today is the transistor. A transistor can be built in many ways, but they are all constructed to amplify an electric signal. By connecting transistors in clever ways, logic gates and in turn whole processors can be constructed. The transistors work because it is so easy to manipulate the amount of charge carriers in doped semiconductors. By applying a small bias to a controlling gate, the conductance of a channel between the source and drain of the transistor can be changed dramatically. This is the amplifying behavior behind most transistors. In a processor, current between a source and a drain is a logic *one*, and no current is a logic *zero*. The basic principle of the metal oxide semiconductor field effect transistor (MOSFET) is shown in fig 1.2(c). The gate (metal) is separated from the p-doped semiconductor channel with an oxide; the *n*-doped source and drain are not shown in fig 1.2(c). In this sketch, they are situated behind and in front of the image. By applying a positive bias to the gate, electrons will accumulate in the conduction band of the semiconductor at the interface to the oxide, forming an inversion layer. The inversion layer has the same type of charge carriers as the source and drain (in this case electrons), allowing for a current to flow between the same. The MOSFET can have either a p-doped channel (nMOS) or an *n*-doped (pMOS). The pMOS works just as an nMOS, but everything is opposite, one applies a negative bias to create an inversion of holes. These two kinds of transistors are then combined forming the complementary metal oxide semiconductor (CMOS) technology which is the backbone of modern integrated circuits design.

#### 1.5 Aim and outline of this thesis

In this doctoral thesis, new methods developed by us for investigations of NWs and NW devices will be presented together with the underlying theories and principles. These methods were developed because there is a need for more information and a better understanding of NWs to enable further development of semiconductor NW devices. The aim is to increase our knowledge and explain, what is happening at the atomic level.

The thesis is based on seven publications which can be divided into two groups with respect to the main technique used. In Papers I–V STM, located in Lund at the division of synchrotron radiation, has been used, often in unconventional ways, to obtain both structural and electronic information from different III–V semiconductor devices. In Paper VI and VII photoelectron spectroscopy techniques, placed at the synchrotrons in Grenoble (ESRF) and Lund (MAX-lab), respectively, have been used to obtain structural and chemical information from different III–V semiconductor devices.

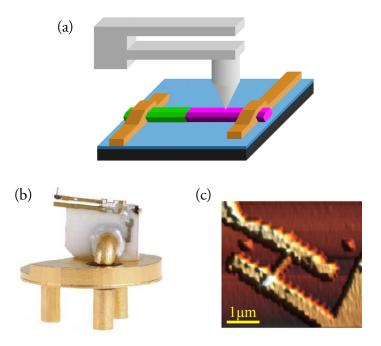

In Paper I a combined atomic force microscope/STM is used to study a contacted III–V semiconductor NW during operation for the first time. In Paper II the same combined microscope used in Paper I is here utilized to perform high resolution scanning gate microscopy on a contacted semiconductor NW. Paper III explains the novel technique of using an STM for contacting up-standing NWs directly. This technique is then utilized in Paper IV to determine the conductivity of InAs NWs with crystal structure interfaces. The influence of the presence of a surface oxide on the NWs is also studied. The same technique is also used in Paper V to determine the Schottky barrier height between InAs NWs and their Au seed particles. In Paper VI hard X-ray photoelectron spectroscopy is used to study a stack with HfO<sub>2</sub> deposited with ALD on InAs with a top layer of metal. The influence of the metal and the composition of the HfO<sub>2</sub> are examined. Paper VII uses the results found in Paper VI, but here time-resolved X-ray photoelectron spectroscopy is used to analyze the growth of the HfO<sub>2</sub> layer in detail.

The thesis consists of two parts where the first covers the theoretical background and gives an introduction to the different experimental techniques used in the articles presented in the second part. The first part is divided into four chapters. In chapter 1an introduction to the research field was given. In chapter 2 NWs and how these can be made into semiconductor devices are explained. Chapter 3 then contains all the experimental technique used and developed for our research. The STM is explained in detail and how it can be utilized to also investigate NW devices and measure the conductance of as-grown NWs. Here X-ray photoelectron

spectroscopy (XPS) is also described, and the advantages of hard X-ray photoelectron spectroscopy (HAXPES) are discussed as well as ambient pressure X-ray photoelectron spectroscopy (APXPS). Finally, chapter 4 summarizes and concludes the thesis and also gives an outlook on the future of our research field.

### 2 Nanowire devices

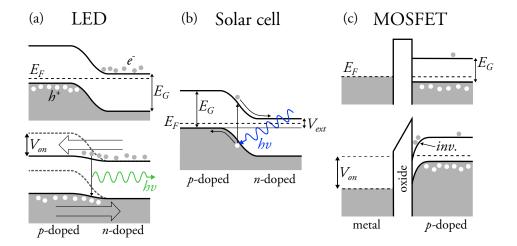

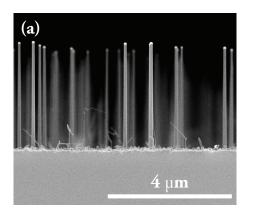

All the NWs studied in this thesis are III-V semiconductor NWs. Despite their name (wires) they are perhaps more correctly described as elongated rods with the typical width of 10 to 100 nm and length of 1 to 10 µm, fig 2.1. The III-V semiconductor NWs are crystalline objects, the atoms in the NWs are arranged in an ordered structure with a repeating pattern. The structure can be described using the atoms that make up the smallest unit in this pattern called the unit cell. The parameters describing the unit cell are referred to as the lattice parameters, and they describe the length of the principal axes of the unit cell and the angles between these. If the width of a NW is small enough the NW can be considered to be a one-dimensional structure where the energy levels of the electrons are quantized in two dimensions. This minimum width for quantization is dependent on many factors such as the NW structure, the NW material, the temperature, and the de Broglie-wavelength of the electrons (0.1 nm in metals but up to 40 nm for semiconductors). The NWs studied during the work presented in this thesis are however large enough not to show this behavior, typically 100 nm in width.

The focus on III–V semiconductor materials in the shape of NWs has been brought on for several reasons. The small width of the NWs allows for strain relaxation in the radial direction which enables change in material composition along the axis between materials of highly different lattice parameters without the formation of stacking faults [17, 18]. The structural and optoelectrical properties of NWs may also be different from the corresponding bulk material [19]. NWs have been shown to improve the performance of electronic devices mentioned in chapter 1 such as LEDs [20-23], photovoltaic cells [24-28], and transistors [29-31]. Also in life science, many applications have been shown [32, 33]. The high surface to volume ratio of NWs is as well advantageous when constructing sensors [34, 35].

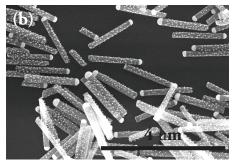

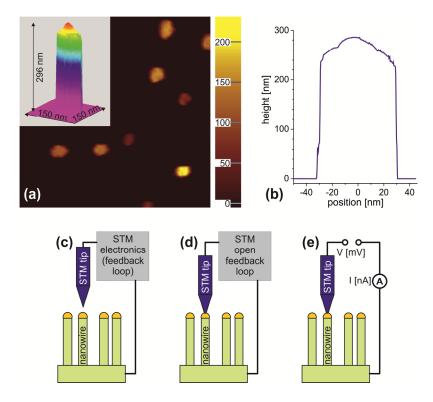

In fig 2.1 two scanning electron micrographs of different InP NWs are shown. Here the typical elongated rod shape is seen as well as the Au seed particle on top of the NWs which is used to catalyze the growth. These NWs, as well as all the NWs investigated throughout this thesis, are made with a bottom-up technique, usually referred to as NW growth.

**Figure 2.1:** Two scanning electron micrographs of two different samples of InP semiconductor NWs grown with Au seed particles. The image in (a) was recorded in cross-section with the NWs standing as-grown on the InP substrates. In (b) a different set of NWs are shown. The NWs have been broken of their growth substrate and put on a new substrate to enable STM investigations of the NW side facets. Here the image was recorded after several heat treatments, and undesired droplet formation (due to excessive heating) is seen on the NW side facets. Images (a) is courtesy of J. Wallentin.

### 2.1 Nanowire growth

Traditionally in the semiconductor industry, devices have been constructed using top-down methods; features down to the nm-scale are etched out, using lithographical processes, of larger blocks in many step processes [36]. There are a great variety of methods used to make NWs, the top-down techniques where you etch away material to form NWs and the two main bottom-up: Solution-phase synthesis and vapor phase epitaxy (VPE). With bottom-up techniques, NWs self-assemble into a wanted structure, given the right circumstances. The process is known as NW growth.

In solution phase synthesis, nanostructures are grown in a high-purity supersaturated melt, and it can be used to grow e.g. Si or Ge homogeneous NWs [37]. It is a more simple method than VPE but it also has the limitations when it comes to material compositions, as well as structural design. For growth of III-V semiconductor NWs, VPE is most commonly used [38] due to the fact that there are more precursors in the vapor phase available, and the control of said precursors can be extremely precise, allowing for atomically sharp interfaces between different materials to be made. The two main techniques for VPE are molecular beam epitaxy (MBE) and metal-organic vapor phase epitaxy (MOVPE).

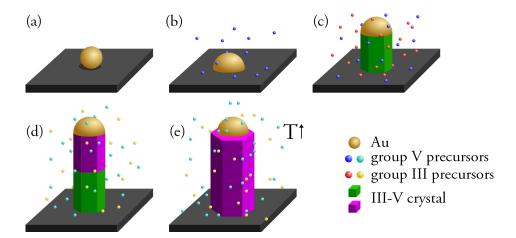

**Figure 2.2:** Au-particle-assisted NW growth in a schematic view. (a) Au particle is deposited on a substrate. (b) Annealing under group V precursor pressure to remove native oxide. (c) Group III precursor is applied, supersaturation of Au particle leads to NW growth. (d) Axial heterostructures can be formed by changing precursors. (e) Introducing radial growth by increasing temperature.

Growth with MBE is done under ultra-high vacuum (UHV) pressures below 10<sup>-9</sup> mbar. The growth constituents are supplied to the growth substrate via elemental beams. Since MBE is performed in UHV the elements travel to the growth substrate without interacting. Once at the substrate, they condense and can interact with each other. MBE can be very precise, and the set-up itself is cheaper than MOVPE. The big drawback for industrial application is the slow growth speed which makes the production cost of mass production of NWs much higher. In the industry, the desired approach would be to produce NWs with MOVPE [38].

All NWs studied in this thesis are grown with MOVPE using Au-particle-assisted growth on crystalline substrates. Epitaxial NW growth is an atomic layer-by-layer growth forming a crystal with the same crystal orientation as the growth substrate. One typically distinguishes between homo- and heteroepitaxy where the former indicates that the NW grown is of the same material as the growth substrate and the latter that it is a different material.

In MOVPE a carrier gas,  $H_2$  or  $N_2$ , is used to transport the growth precursors to the growth substrate. The group III precursors are typically metal-organic compounds such as trimethylgallium ( $Ga(CH_3)$ ) and the group V precursors are hydrides such as arsine ( $AsH_3$ ). The precursors decompose and form crystalline III-V semiconductor material while the organic ligands react with the hydrogen and are desorbed. Au-particle-assisted NW growth starts with the deposition of Au particles on a crystalline growth substrate with a certain crystallographic direction, typically <111>B, fig 2.2(a). The substrate is then annealed in the MOVPE

growth chamber to remove unwanted contaminants and the native oxide of the substrate, fig 2.2(b), under group V precursor overpressure. This also melts the Au particles. The group III precursor is then also applied and alloys with the Au particle. At a certain point, the Au particle becomes supersaturated, and there will be a nucleation of III-V material between the Au particle and the substrate. More precursors are continuously supplied, and the deposition of material continues under the Au-particle, forming a NW, fig 2.2(c). To stop the growth, the supply of group III precursor is simply ended. To create NWs with complex structures one can either change the precursors, changing the material that will grow, fig 2.2(d), or increase the temperature to change the preferred [39] growth direction to introduce layer growth, i.e. growing walls on the NW to get coreshell structures, fig 2.2(e).

### 2.2 Nanowire doping

Over 20 years ago, K. Haraguchi et al. showed that it is possible to grow axial *p-n* junctions in NWs [40]. Since then large advances have been made in the field of NW growth and doping, but there are still many questions left to answer. Doping plays an important role in NW growth. The crystal structure has been shown to change when different dopants are introduced during NW growth [41]. It is also important to note that the carrier concentrations in NWs are not always proportional to doping concentrations. The control of the NW doping is of utmost importance for the operation characteristic of any NW device, and a lot of work has been put into the development of techniques to evaluate it.

Standard methods for doping planar devices are diffusion or ion implantation. To make axial doping profiles in NWs, these standard techniques are not ideal [42] since NWs typically are grown normal to the crystal surface. Instead, in-situ doping is used where the dopants are introduced during growth. As an effect, the doping profiles will be determined in large by the solubility of the dopants in the Au seed particle and their diffusion lengths. This can be used to create sharp doping profiles with interfaces which are only tens of nm wide [3].

The actual evaluation of the doping is also challenging since *standard* Hall measurements can not be used for NWs because of their small size (with specialized device fabrication for Hall measurements of NWs it has been shown that Hall measurements are possible for NWs [43]). Lately, a number of quantitative techniques have been explored by various groups. The most common of these is most probably the NW field-effect transistor (NW-FET) set-up. A NW is placed on an oxidized substrate and contacts are deposited to the ends of the NW. By changing the gate bias to the substrate and measuring the conductance

through the NW the carrier concentration and mobility of the carriers can be determined. This is however done using a series of assumptions [42]. Another major drawback of the NW-FET set-up is the contacting of the NW which is very challenging and requires oxide free NWs as well as high doping concentrations. It should also be noted that the NW-FET only gives information about the carrier concentration and mobility, which, for device optimization, is more important but it does not reveal the actual amount of dopants. Neither does it reveal the local distribution of the dopants over the length of a NW.

To evaluate the dopant concentration secondary-ion mass spectrometry or the more advanced technique, atom probe tomography (APT) can be used [44]. In APT a needle-shaped sample is needed, by pulsing the sample with an electric field and measuring the time-of-flight for the field emitted ions from the sample, a representation of the needle can be obtained with sub nm resolution. This method also has limitations. It is completely destructive since it has to remove an ion from the sample to detect it. The sample shape also puts limitations on what samples and sizes can be studied [45].

Another widely used method which in many respects is the opposite of APT is energy dispersive X-ray spectroscopy (EDX) where the resolution is more limited but the sample size- and structure constrictions are less confining, and it is also faster. EDX is an extension to a scanning- or tunneling electron microscope (SEM or TEM) with an extra detector that detects the photons with characteristic energy emitted from the various atoms in the sample.

### 2.3 Metal-semiconductor electrical contacts

The electrical contact between a semiconductor and a metal plays a crucial role in the performance of any semiconductor device [46]. A good contact is a contact which does not influence the performance of the device and has a small voltage drop over it compared to the rest of the device. These contacts are generally named ohmic contacts. Conversely, contacts which do affect the device performance are named rectifying contacts. In 1938, Schottky explained the rectifying behavior of these

**Figure 2.3:** Energy band diagram of metal-semiconductor contacts and how to determine the Schottky barrier height. (a) The n-doped semiconductor and the metal in thermal nonequilibrium conditions. (b) The metal and semiconductor are now at thermal equilibrium and the barrier height  $\phi_{Bn}$  and the built-in potential  $\phi_{bi}$  are seen. (c) For an ohmic contact to be formed either a low  $\phi_{Bn}$  (thermionic emission, top) and/or a high doping level closest to the metal (tunneling, bottom) is required. (d) Experimental current—voltage data (blue circles) from the Au-semiconductor interface of the NWs in Paper **V**. The red line is the simple linear regression used to determine  $I_S$  used to calculate  $\phi_{Bn}$ .

contacts as a potential barrier arising from the space charges in the semiconductor [47]. This barrier now holds his name and it is known as the Schottky barrier.

To understand the nature of the different metal-semiconductor contacts, one starts with the ideal case of a metal brought into contact with a semiconductor, fig 2.3(a, b) [48]. In fig 2.3(a) the energy band diagrams are shown of a metal and an n-doped semiconductor isolated from each other. The work function of a material is defined as the energy difference between the Fermi level and the vacuum level. Typically the metal work function  $q\phi_m$  and the semiconductor work function  $q\phi_s$  are not the same. In fig 2.3(a) the electron affinity of the semiconductor  $q\chi$  is also shown. It is the energy difference between the vacuum level and the conduction band of the semiconductor. With the two materials in contact, thermal equilibrium is established, and the Fermi levels of the two materials have to align. The vacuum level also has to be continuous which results

in the band-bending situation shown in fig 2.3(b). The potential barrier height the electrons in the metal have to overcome to enter the semiconductor is denoted  $q\phi_{Bn}$  and it is the difference between  $q\phi_m$  and  $q\chi$ :

$$q\phi_{Bn} = q\phi_m - q\chi. \quad (2.1)$$

Conversely, the barrier height the electrons in the semiconductor see is called the built-in potential  $q\phi_{bi}$  and it is the difference between  $q\phi_m$  and  $q\phi_s$ :

$$q\phi_{bi} = q\phi_m - q\phi_s. \quad (2.2)$$

The barrier height between a metal and a *p*-doped semiconductor is denoted  $q\phi_{Bp}$  and it is given by

$$q\phi_{Bp}=E_q-(q\phi_m-q\chi), \quad (2.3)$$

where  $E_g$  is the band gap of the semiconductor.

The following text will be referring to n-doped semiconductors, but it is also valid for p-doped. To obtain an ohmic contact between a metal and a semiconductor a low barrier height  $(q\phi_{Bn/p} \sim kT)$  and/or high doping is demanded. With a low barrier height, there is no hindrance for thermionic emission of electrons between the semiconductor and the metal, fig 2.3(c) top. If  $q\phi_{Bn/p} \gg kT$  a high doping concentration closest to the metal is required to shorten the depletion layer width sufficiently enough to allow for tunneling through the barrier, fig 2.3(c) bottom. If the barrier is too high and the doping is not high enough the contact will be rectifying, and the barrier will be referred to as a Schottky barrier.

At room temperature, the dominating transport mechanism over the Schottky barrier is thermionic emission of majority carriers from the semiconductor to the metal [48]. The current-voltage (*I-V*) behavior is

$$I = I_S (e^{\frac{qV}{kT}} - 1),$$

(2.4)

$$I_S = AA^*T^2e^{-\frac{q\phi_{Bn}}{kT}},$$

(2.5)

where  $I_S$  is the saturation current, A the interface area of the contact,  $A^*$  the effective Richardson constant which is dependent on the semiconductor material, and T is the absolute temperature. For  $qV \gg kT$  the I-V behavior, equation 2.4, can be rewritten as

$$\log(I) = V \frac{q}{\eta kT} \log(e) + \log(I_S), \quad (2.6)$$

where the ideality factor  $\eta$  is added to account for different types of currents. An ideality factor of 1 means that the ideal diffusion current completely dominates, whereas an ideality factor of 2 indicates that recombination currents are dominating. By plotting experimental I–V values, fig 2.3(d), and making a simple linear regression for values  $V \gg kT/q$ , the value for  $I_S$  can be determined at V=0 for the simple linear regression, assuming diffusion currents to be dominating. The value for  $I_S$  is then used to determine the Schottky barrier height by writing equation 2.5 as

$$\phi_{Bn} = \frac{kT}{q} \ln \left( \frac{AA^*T^2}{I_S} \right). \quad (2.7)$$

This method was used for determining the Schottky barrier at the Au-semiconductor interface of the NWs in Paper V.

Equation 2.1 is only true for the ideal case, and for real world metal-semiconductor contacts more factors contribute to an eventual Schottky barrier height. The termination of the semiconductor crystal at the metal interface induces surface states which may very well be situated in the band gap and influence the barrier height [49]. The structure and dimensions of the metal-semiconductor contacts can also influence the height [50]. In Paper V we also discuss the formation of a dipole layer between the metal and semiconductor which can reduce the height. The semiconductor, in this case, is GaAs NWs grown in the (111)B plane with the top Au-seed-particle acting as the metal. The interface between the NWs and the Au consists of only As atoms due to the orientation the NW growth. The As atoms in contact with the Au atoms have a lower electronegativity compared to their neighboring Ga atoms resulting in a dipole layer which in turn lowers the Schottky barrier.

### 2.4 Devices

The most basic NW device is simply contacted NWs. LEDs, solar cells, and transistors can all be made by using NWs still standing on their growth substrate, as-grown [51-53]. The growth substrate then acts as one contact to the NWs and another contact is deposited on top of the NW array. For the transistors, a third contact is needed for the gate. This set-up, with the NWs as-grown, is ideal for industry applications because of the relative few process steps needed to create the devices. In Paper I and II, however, another device design is used to study the NWs, namely the before mentioned FET set-up. This design is used purely for research purposes to enable investigation of the NW properties.

Constructing devices out of NWs has been shown to improve device performances compared to bulk devices. This can be measured as better energy conversion efficiency for solar cells or luminous efficacy for LEDs. These properties are straightforward to measure but, they will only tell you whether your device is working well or not, not how, and maybe even more important, why. To investigate how and why various NW devices work as they do, we have set out to develop novel techniques as well as combining existing methods to investigate the properties of NW devices. Our findings are presented in Papers I–VII in the second part of this thesis.

Moore's law states that the number of transistors on integrated circuits will double approximately every two years [54]. However, Moore's law is not a law but rather a prediction and it has been fulfilled (with slight modifications) during the last decades by the downscaling of the planar MOSFET. This is because the semiconductor industry adopted the statement and has used it as the road map for their development. By making the transistors smaller, not only has the performance improved but the level of integration has increased drastically and the power consumption per function implemented has gone down [55]. The downscaling can not continue ad infinitum due to quantum effects and problems with power dissipation (and in turn overheating), so researchers are now developing new ideas and techniques to continue Moore's law. The NW wrap gate MOSFET has a gate that encloses the transistor channel as compared to standard planar MOSFET where the gate sits on top, enabling improved electrostatic control within the channel [56]. This makes further scaling of the gate possible, or one does not have to scale the oxide as much. With sub 5 nm NW diameter the device can work in the quantum capacitance regime with lower power consumption as a result as well [55, 57]. Utilizing other gate oxides with higher relative dielectric constant also help improve the performance of the MOSFET. In Papers VI and VII, the properties of one such oxide, HfO<sub>2</sub>, and the mechanisms behind its growth are investigated.

# 2.5 Atomic layer deposition & high-k dielectrics

In the semiconductor industry, Si has been the material of choice in large part due to its native oxide,  $SiO_2$ , which easily forms. The oxide plays a crucial part in all transistors as it forms the insulating layer between the gate and the channel. The effectiveness of the gate to introduce charge carriers in the channel is directly proportional to the capacitance of the oxide. The drain current is proportional to the number of charge carriers in the channel, and it is one of the key output parameters of the transistor. Downscaling has been the driving force behind the

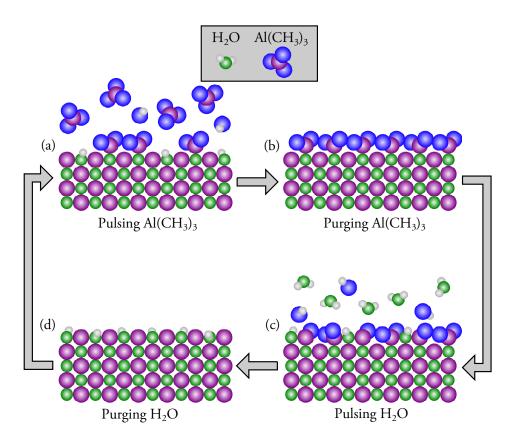

**Figure 2.4:** Schematic presentation of the ALD process, in this case for the forming of  $Al_2O_3$ . In step (a) the precursor  $Al(CH_3)_3$  is dosed over an already formed  $Al_2O_3$  layer (which is terminated with O-H groups) and an atomic layer of  $Al(CH_3)_2$  is formed covering the oxide. During this process, excess  $CH_4$  (gas) is formed. In step (b) the sample is purged, and all that is remaining is the  $Al(CH_3)_2$  layer. In step (c) the sample is dosed with  $H_2O$  and a new  $Al_2O_3$  layer (terminated with O-H groups) is formed. Also in this process excess  $CH_4$  (gas) is formed. In step (d) the sample is once again purged and the cycle can start over.

increase in processor speeds but the limit when the electrons start to tunnel through the gate oxide (approx. 2 nm oxide thickness), creating leakage currents and thereby increased power consumption, has been reached.

The capacitance, C, of the MOSFET oxide can be modeled as a parallel plate capacitor,

$$C = \frac{\kappa \epsilon_0 A}{t}, \quad (2.8)$$

where A is the area of the oxide, t is the thickness,  $\epsilon_0$  is the vacuum permittivity, and  $\kappa$  is the relative dielectric constant. Given a certain dimension of our

transistor, A will be given, and t can not be smaller than 2 nm. That leaves  $\kappa$  as the only parameter left to alter to increase the capacitance. Materials with a high  $\kappa$  are often referred to as "high- $\kappa$ " or simply "high-k" dielectrics. Typical high-k dielectric materials include  $Al_2O_3$  and  $HfO_2$ . In Papers VI and VII, we study the structure of  $HfO_2$  grown with ALD and also the actual ALD growth process of  $HfO_2$ .

When it comes to deposition of these high-k materials, as thin conformal films, on high aspect structures, such as standing NWs, atomic layer deposition (ALD) is considered one of the most promising techniques [58]. ALD was invented by Tuomo Suntola in 1974 but was then called atomic layer epitaxy (ALE). However, most films grown are not epitaxially grown on the underlying substrate and often films grown are amorphous. Hence the more accurate description atomic layer deposition has been adopted. ALD is a sequential, self-limiting surface reaction technique and can be described as consisting of four essential steps [59], fig 2.4(a-d): 1) first precursor exposure, 2) purging of said precursor and byproducts, 3) second precursor exposure, and 4) purging of the second precursor and byproducts. This process is then iterated until the desired number of atomic layers have been grown. The main and distinctive difference between ALD and MOVPE is that ALD is self-limiting; the precursors will not bind to themselves, allowing the ALD film to grow one mono layer per iteration. In MOVPE, due to variations over a sample in precursor flux, adsorption probabilities, and surface diffusion, growth speeds will vary across the sample. This causes nonconformal growth in MOVPE where different precursors are present at the same time. But due to the self-limiting properties due to the sequential dosing of the precursors in ALD, conformal growth can be achieved even on high aspect ratio structures. The selflimiting properties also ensure atomic monolayer precision even when growing nm thick layers.

## 2.6 Nanowire cleaning

All NWs studied during the work for this thesis have been grown by collaborating groups. The transfer of NWs from MOVPE chambers to our various experimental set-ups is done in air under atmospheric pressure. The use of vacuum suite cases where the NWs are kept at low pressures under all times could, in theory, be implemented. At the time of writing this thesis, though, our equipment does not have the specific adaptations to support such an elaborate transfer system. III-V semiconductor materials will oxidize under atmospheric pressures in air, forming a native oxide of 1-2 nm thickness at the surface. This oxide formation is detrimental for device performances, and it is circumvented by encapsulating

processed devices in buffer materials. This procedure will, however, make surface studies of the NWs impossible. Without the encapsulation the oxide will however also greatly reduce the effectiveness of many surface science techniques since the surface of interest will be buried underneath; in XPS the signal from the III-V semiconductor will be greatly reduced and for STM the oxide might even cause the tip to crash.

An oxide removal technique which has been used extensively for metal crystals is Ar-ion sputtering [60]. To ensure high surface crystal quality, the sample has to be annealed afterward to remove trapped Ar atoms and to reduce induced surface roughness. However for III-V semiconductors Ar-ion sputtering induces amorphous layers as well as defects which are hard to anneal away [60]. This is especially true for III-V NWs which in many cases will be destroyed if treated with the temperatures needed to anneal away defects.

Instead, atomic hydrogen cleaning (AHC) has been shown to successfully remove surface contaminants on III-V semiconductor surfaces, especially oxygen and carbon [61]. AHC can be performed inside the preparation chamber of the STM under UHV condition. The sample is annealed (for InAs typically to 650 K) under a flux of atomic hydrogen radicals (H\*) which are formed with a thermal cracker (typically at 2000 K) attached to the preparation chamber. The H\* react with the surface oxides, hydrocarbons, and other surface contaminants and the products are desorbed leaving behind a clean III-V semiconductor surface. The H\* have very low kinetic energies (typically less than 1 eV) limiting their interaction with the III-V semiconductor surface to the top atomic layers. This greatly limits their incorporation in the III-V semiconductor [62]. This method is instrumental for much of the STM work on NWs at our division [63-65], and in Paper I this method is used to enable STM investigations of NW side facets.

Thermal cleaning of III-V semiconductors without H\* is also possible, but it requires higher temperatures which create a problem due to the congruent evaporation temperatures ( $T_C$ ) of III-V semiconductors. At temperatures above  $T_C$ , the rate of evaporation of the group V material will be larger than for the group III leading to a change in the surface chemical composition.

Cleaning NWs is paramount when studying their facets, but it can also be used as a tool to study how surface states on the NW affect the NW devices performance. In Paper III we present supporting information on how the performance of *p-i-n* (*p*-doped, intrinsically doped, *n*-doped) junction InP NWs is greatly improved upon removal of the surface oxides with AHC. In Paper IV we see how the surface states of InAs NWs affect the NW conductance differently depending on the crystal structure of the NWs.

# 3 Experimental techniques

In this chapter, the two main experimental techniques relevant for this work, will be described, as well as the new methods developed for these. The two main techniques are scanning tunneling microscopy (STM) and X-ray photoelectron spectroscopy (XPS). The new methods are scanning probe microscopy (SPM) on NW devices, STM in top contact mode, hard X-ray photoelectron spectroscopy (HAXPES), and ambient pressure XPS. Both main techniques are usually referred to as surface sensitive techniques, but there are many ways to define what surface sensitive means. When using surface science techniques, one has to be aware of the penetration depth of said technique. The technique might show information of the top most layer of atoms or from tens of nm under the surface. STM and XPS are on either side of the surface sensitive-spectrum. STM probes the outermost atomic layer structure and its electronic properties, and XPS give information about the elemental composition of materials from up to 20 nm below the surface. Most surface science techniques require ultra-high vacuum (UHV) conditions, pressure below 10<sup>-9</sup> mbar, to work. There are two main reasons for this. First is the contamination of the sample surface due to impingement of the atoms/molecules in the surrounding atmosphere on the surface, which is directly proportional to the surrounding pressure. At room temperature, and pressures of 10<sup>-6</sup> mbar, a surface with a sticking coefficient of 1 (typical metal) will be covered in a layer of atoms in roughly one second. The second reason for using UHV conditions is the detection of the kinetic energy of electrons used in many techniques. An electron emitted from a solid into a gas will travel a certain distance before inelastically colliding with the atoms/molecules in the gas, losing kinetic energy. This process, known as inelastic scattering, is reversely proportional to the gas pressure. Once an electron has lost kinetic energy, it is no longer interesting to detect and it will only contribute to the background noise.

# 3.1 Scanning tunneling microscopy

The STM is a surface sensitive technique which utilizes the quantum mechanical tunneling of electrons to image surfaces at the atomic level. In 1986, Dr. Gerd

**Figure 3.1:** A low magnification scanning electron micrograph of an STM tip made from an etched W wire. The black background with holes is the carbon tape with which the tip is mounted in the scanning electron microscope. The etched W tip itself is clamped in a steel tube which in turn is mounted in the tip-holder. The indentations on the steel tube are from the pliers used when fixating the tip.

Binnig and Dr. Heinrich Rohrer at the IBM Research Laboratory in Zurich, Switzerland, were awarded the Nobel Prize in physics for their design of the STM which they reported on five years earlier [66]. This revolutionizing tool enables resolution of individual atoms and localized electronic states on the surface of any conducting or semiconducting material. In Papers I-V we utilize this tool to investigate NWs in both conventional and unconventional ways.

The name of the technique arises from the fact that an atomically sharp probe is raster *scanned* over a surface while a *tunneling* current between the probe and the surface is measured. The probe and the surface are never in contact during normal STM investigations. The signal recorded – either the strength of the tunneling current or the height of the tip – is made into an image showing the properties of the studied surface. The probe used is usually an electrochemically etched W wire, fig 3.1, or a cut Pt/Ir wire which forms an atomically sharp tip. The surface is the surface of either a metal or a semiconducting material. The spatial resolution is

around 0.1 nm in plane with the surface studied and 10 pm normal to the surface plane. The image repetition rate is in the order of minutes per image but can, under the right circumstances be as high as 25 images per second [67].

The current measured cannot be explained with classical physics since the work function (the energy needed to bring an electron from the Fermi level into vacuum) for an electron in a solid is typically in the eV range while the thermal energy available at room temperature to overcome this barrier is only 25 meV. Instead, a quantum mechanic approach is needed to explain the flow of electrons between the tip and the sample. In quantum theory, and then also reality, an electron has a certain probability to be anywhere in space at a certain time (granted, the probability will be infinitesimally small everywhere except for within a small volume in space) [68]. This probability cloud can then extend from the outmost point of the tip, through the distance between tip and sample, and into the sample. If there is an electronic state in the sample that the electron can occupy then the electron in the tip has a certain probability to occupy that state. If it does so, it has tunneled from the tip to the sample and thus created a tunneling current.

#### 3.1.1 Electron tunneling

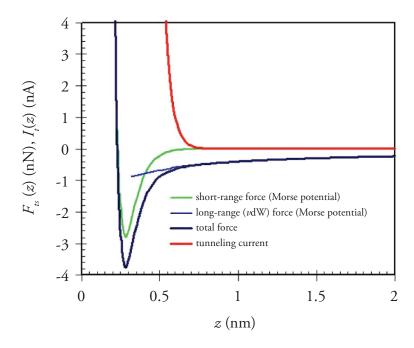

Tunneling between two conducting materials may occur when they are so close together that the electron wave functions at the Fermi level of each material overlap significantly due to leak out from the electrons potential confinement wells. This leak out has a typical inverse decay length, K, which can be described as

$$K = \hbar^{-1} (2m\phi)^{\frac{1}{2}},$$

(3.1)

where m is the electronic mass and  $\phi$  is the effective local work function. This can be rewritten as  $K \approx 0.51 \phi^{1/2}$  where K is measured in Å<sup>-1</sup> (1 Å = 0.1 nm) and  $\phi$  in eV. By bringing the tip and the sample close enough together (< 1 nm) and applying a potential difference between the same, a tunneling current,  $I_T$ , will arise which relates to the tip-sample distance, d, as (fig 3.2(a))

$$I_T \propto e^{-2Kd}.~~(3.2)$$

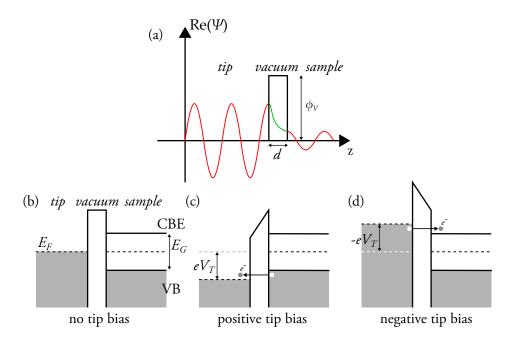

It is important to note that d is actually the distance between the two electronic states which the electron tunnels between. Imaging larger objects (at the nm range) with an STM will reveal the structure morphology but when imaging individual atoms the spatial structure of the electronic states of both the tip and

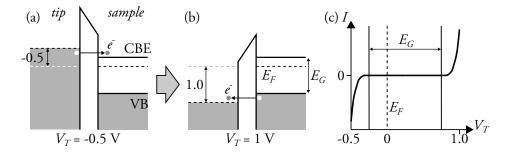

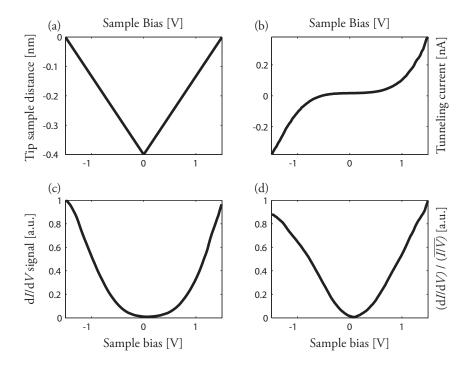

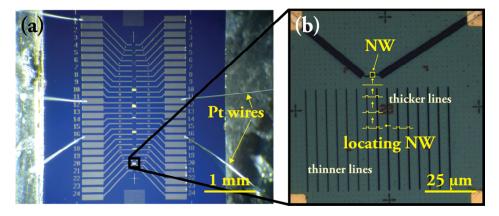

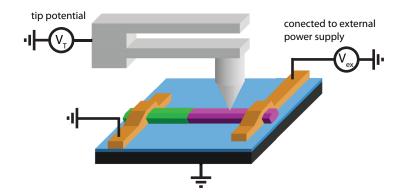

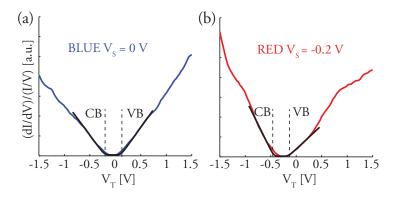

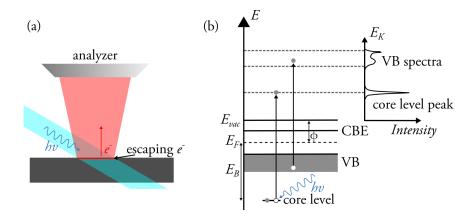

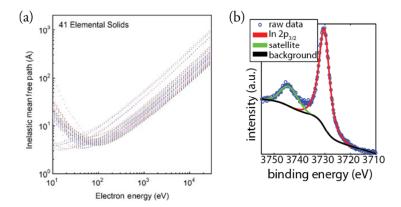

**Figure 3.2:** (a) The wave function of an electron as it tunnels from the tip into the sample (assuming that the tip and sample have the same work function). The potential barrier is the vacuum between the tip and the sample with thickness d and potential height  $\phi_V$ . (b) Band diagram of the tip and sample with no applied bias and hence no tunneling. (c) The band diagram with positive tip bias  $(V_T)$ , showing the electrons tunneling from the valence band (VB) of the semiconductor, through the vacuum to the empty states in the tip. (d) With negative tip bias  $(-V_T)$  the electrons in the tip can tunnel to the empty states in the conduction band instead. Only the conduction band edge (CBE) is shown in (b-d)