# Efficient Processing and Storage for Massive MIMO Digital Baseband

Yangxurui Liu

Doctoral Thesis Electrical Engineering Lund, March 2018

Yangxurui Liu Department of Electrical and Information Technology Electrical Engineering Lund University P.O. Box 118, 221 00 Lund, Sweden

Series of licentiate and doctoral theses ISSN 1654-790X; No. 113 ISBN 978-91-7753-561-4 (print) ISBN 978-91-7753-562-1 (pdf)

© 2018 Yangxurui Liu Typeset in Palatino and Helvetica using  $\LaTeX$ 2 $_{\epsilon}$ . Printed in Sweden by Media-Tryck, Lund University, Lund.

No part of this thesis may be reproduced or transmitted in any form or by any means, electronically or mechanical, including photocopy, recording, or any information storage and retrieval system, without written permission from the author.

## **Abstract**

Driven by the increasing demands on data rate from applications, the wireless communication standard has for decades been evolving approximately at a pace of one generation per ten years. Following this trend, the ambitious plan to replace the current cellular mobile network standard (4G) with the next generation standard (5G) is going through the standardization phase and is getting close to its actual deployment. Promised benefits associated with 5G include higher data rates, lower latency, higher reliability, more connected users, etc. One of the candidate technologies to enable these benefits is based on massive Multiple-Input and Multiple-Output (MIMO).

Massive MIMO systems have base stations equipped with a large number of antennas (hundreds or even more) serving multiple users simultaneously in the same time and frequency resource. It provides higher spectral efficiency and transmitted energy efficiency due to the large spatial multiplexing and antenna array gain. However, massive MIMO requires simultaneous processing of signals for all the antenna chains and real-time computations involving large-size matrices. Compared to today's small-scale MIMO, the corresponding computational complexity can be orders of magnitude higher, which inevitability leads to higher area cost and processing energy consumption. Besides the inherently higher computational complexity, massive MIMO also introduces new design challenges for the data storage system. For example, the number of elements in the Channel State Information (CSI) matrix can increase by hundreds of times. Moreover, to support high-throughput matrix operations, the gap between computational capacity and the memory bandwidth must be bridged. Sophisticated baseband processing algorithms demand complicated data access modes and thus call for smart data storage solutions.

This thesis focuses on two important topics in digital baseband processing: energy-efficient computing and organization of large matrices. Systemalgorithm-circuit co-optimization is explored to meet the real-time computational requirements. In the first topic, the concept of adaptive energyquality scalable circuit is studied to trade between Quality of Service (QoS) and energy consumption. At circuit design level, a multiplier supporting three wordlengths is designed to provide run-time processing precision adjustment. At system and algorithm level, the concept of algorithm switching is investigated. A resource scheduling scheme to switch between accurate and approximative algorithms is developed to exploit the dynamics in the wireless channel. As shown in a case study, 58% energy can be saved by applying this method when implementing on a QR-decomposition processor. In terms of data organization, the concept of parallel memories is applied to provide lowlatency, high-bandwidth, and highly flexible data access for massive MIMO baseband processing. On top of this, on-chip channel data compression methods are proposed, which utilize the inherent sparsity in massive MIMO channel. As a case study, the presented algorithms are capable of saving about 75% of storage requirement for a 128-antenna system with less than 0.8 dB loss in performance. Based on the channel compression concept and various access patterns supplied by parallel memories, a heterogeneous memory system is designed and implemented (layout) using ST 28 nm Fully Depleted Silicon On Insulator (FD-SOI). The area cost is 0.47 mm<sup>2</sup>, which is 58% smaller than a memory system with the same capacity and without compression.

The energy-efficient computing and data organization of large matrices provides a promising methodology for the actual deployment of massive MIMO baseband processor.

# Contents

| A  | bstra | ct                                      | iii  |

|----|-------|-----------------------------------------|------|

| Pı | efac  | e                                       | xi   |

| A  | ckno  | wledgments                              | xiii |

| A  | crony | yms and Mathematical Notations          | xv   |

| 1  | Intı  | roduction                               | 1    |

|    | 1.1   | Scope of the Thesis                     | 2    |

|    | 1.2   | Contribution and Thesis Outline         | 3    |

| 2  | Dig   | gital Baseband Processing               | 5    |

|    | 2.1   | Wireless Channel                        | 6    |

|    | 2.2   | Wireless Transmission Technologies      | 8    |

|    | 2.3   | Overview of Digital Baseband Processing | 14   |

|    | 2.4   | Operation Profiling                     | 16   |

| 3  | Dig   | gital Integrated Circuit                | 19   |

|    | 3.1   | Architecture Level Technologies         | 21   |

|    | 3.2   | Circuit Level Technologies              | 23   |

| I  |                           | ssing                                           | 27  |  |

|----|---------------------------|-------------------------------------------------|-----|--|

| 4  | Sub-word SIMD Multiplier  |                                                 |     |  |

|    | 4.1                       | Prior Work and State-of-art                     | 30  |  |

|    | 4.2                       | Sticky Booth Encoding                           | 31  |  |

|    | 4.3                       | Hardware Implementation                         | 34  |  |

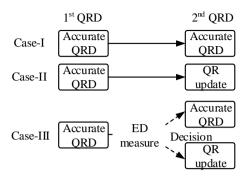

| 5  | Pro                       | cessing Resource Scheduling                     | 37  |  |

|    | 5.1                       | Channel Pre-processing in MIMO                  | 38  |  |

|    | 5.2                       | Scheduling Algorithms                           | 40  |  |

|    | 5.3                       | Performance Evaluation                          | 46  |  |

| II | Me<br>ing                 | emory System for Massive MIMO Baseband Process- | 53  |  |

| 6  | Parallel Memory System    |                                                 |     |  |

|    | 6.1                       | Prior Work and State-of-art                     | 57  |  |

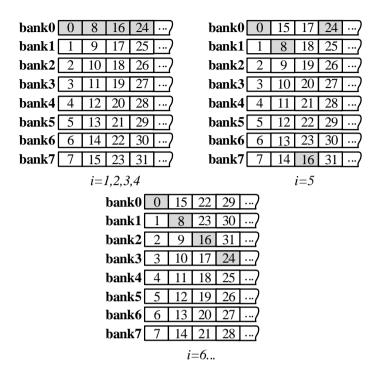

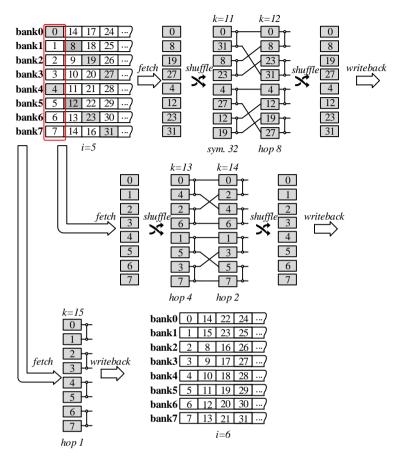

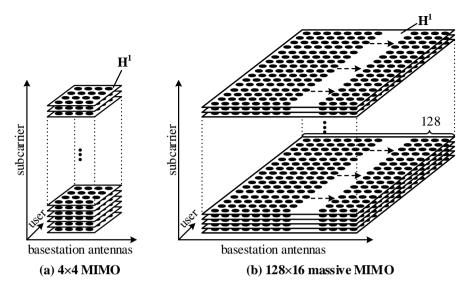

|    | 6.2                       | Data Organization for MIMO Processing           | 59  |  |

|    | 6.3                       | Data Organization for Sorting                   | 72  |  |

| 7  | Cha                       | nnnel Data Compression                          | 85  |  |

|    | 7.1                       | Related Work                                    | 87  |  |

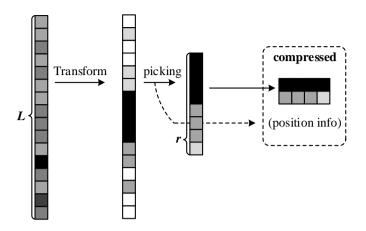

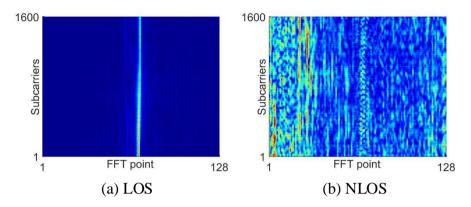

|    | 7.2                       | Domain Transform Compression                    | 89  |  |

|    | 7.3                       | Group-based Compression                         | 93  |  |

|    | 7.4                       | Performance Evaluation                          | 95  |  |

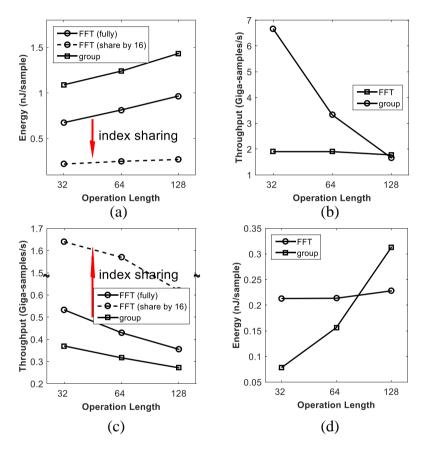

|    | 7.5                       | Operations in Compression Algorithms            | 100 |  |

| 8  | Multi-level Memory System |                                                 |     |  |

|    | 8.1                       | Memory System Design Specifications             | 103 |  |

|    | 8.2                       | VLSI Architecture                               | 104 |  |

|    | 8.3                       | Hardware Implementation                         | 110 |  |

| Co | onclu                     | sion and Outlook                                | 115 |  |

| Aı | ppen                      | dix A Popular Science Summary                   | 119 |  |

Bibliography 121

## **Preface**

This thesis summarizes my academic work carried out from November-2013 to March-2018 in the Digital ASIC group, at the department of Electrical and Information Technology, Lund University, Sweden. The main contributions are derived from the following articles sorted by publication date:

- Y. Liu, O. Edfors, L. Liu, and V. Öwall, "An Area-efficient On-chip Memory System for Massive MIMO using Channel Data Compression," (submitted to IEEE Transactions on Circuits and Systems I: Regular Papers)

- **Contribution** This research work has been performed by first author under the guidance of the remaining authors. The first author has presented the compression algorithm development, hardware implementation, algorithm mapping, and performance evaluation.

- Y. Liu, O. Edfors, L. Liu, and V. Öwall, "Reducing On-chip Memory for Massive MIMO Baseband Processing using Channel Compression," in 2017 IEEE 86th Vehicular Technology Conference: VTC2017-Fall, 2017.

- **Contribution** Based on the concept proposed by the second and fourth author, the first author has presented a channel data compression algorithm and evaluate its effectiveness.

- Y. Liu, L. Liu, and V. Öwall, "Architecture Design of a Memory Subsystem for Massive MIMO Baseband Processing," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 10, pp. 2976-2980, Oct. 2017.

- **Contribution** The first author has presented an on-chip parallel memory subsystem. Design target analysis and hardware development of the subsystem have been performed.

- Y. Liu, H. Prabhu, L. Liu, and V. Öwall, "Adaptive resource scheduling for energy efficient QRD processor with DVFS," in 2015 IEEE Workshop on Signal Processing Systems (SiPS), 2015, no. 2, pp. 1–6.

- **Contribution** The first author has investigated the concept of algorithm switching and resource scheduling scheme. The performance analysis and energy evaluation are formulated by the first author.

- C. Zhang, H. Prabhu, Y. Liu, O. Edfors, L. Liu, and V. Öwall, "Energy Efficient Group-Sort QRD Processor with On-line Update for MIMO Channel Pre-processing," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 5, pp. 1220–1229, 2015.

- **Contribution** The third author has deployed dynamic voltage and frequency scaling (DVFs) technology on a baseband platform proposed by the first author and evaluated the corresponding power reservation.

- M. A. Arslan, K. Kuchcinski, F. Gruian, and Y. Liu, "Programming support for reconfigurable custom vector architectures," in Proceedings of the Sixth International Workshop on Programming Models and Applications for Multicores and Manycores PMAM 15, 2015.

- **Contribution** The fourth author has supplied hardware models for programmability verification.

- Y. Liu, L. Liu, V. Öwall, and S. Chen, "Implementation of a dynamic wordlength SIMD multiplier," 2014 NORCHIP, Tampere, 2014, pp. 1-4.

Contribution The first author developed a concept of "sticky Booth coding" for multiplier and implemented the "proof-of-concept" hardware.

Furthermore, I have contributed in the following documents:

- Y. Liu, L. Liu and V. Öwall, "Implementation of a dynamic wordlength SIMD multiplier," Swedish System-On-Chip Conference.

- Y. Liu, H. Prabhu, L. Liu, and V. Öwall, "Energy Efficient QR Decomposition Processor with Adaptive DVFs Scheduling," Swedish System-On-Chip Conference.

- MAMMOET Technical Report, "D3.3 Hardware aware signal processing for MaMi", https://mammoet-project.eu/.

# Acknowledgments

The four and half years life in Lund University is full of adventures and exciting moments. It is an important experience of my life. I would like to thank many people who have helped and supported me.

First of all, I would like to thank my supervisor Professor Viktor Öwall for the great support and encouragement during my Ph.D. journey. He is always supporting me, standing firmly on my side, and ready to provide all possible help (even after midnight). I would also like to express my deep gratitude to my co-supervisor Associate Professor Liang Liu, for the tons of comments on works and technical writing. I will never forget your great patience on my papers and helps in daily life. Without you, I would never come to this moment.

I am grateful to Professor Ove Edfors for the fascinating idea and suggestions. I would like to thank the senior researchers and administrators at the department of EIT.

I would like to thank all my colleagues in Digital ASIC group for the wonderful experience, helps, and happy moments. I would thank Ping, Chenxin, Hemanth, Isael, Yasser, Reza, Oskar, Xiaodong, Farrokh, Dimitar, Rakesh, Steffen, Ahmed, Mojtaba, Siyu, Xuhong, Breeta, Michal, Meifang, Babak, Minkeun, Sha, Jesús, and others I may have not mentioned for the help and comments on my work.

Thank Professor Shuming Chen, who was my supervisor during my master degree. Thank you for your guidance and the great help during my application of studying abroad. Thank Professor Dake Liu for recommending me to Lund University.

Special thank to one of my best friend Jianbiao Mao. We have known each other since 12 years ago and was roommates during college. He had helped me in dealing with all the document works in China during my Ph.D. journey

and left us forever.

I thank all Chinese friends I met in Lund, including but not limited to Yiheng, Yuan, Qian, Lu Chen, Hong, Huan, Lu Liu, Songran, Mingfa, Chenglong, Jiatang, and Xi.

Last but not least, I would like to thank my parents for the unconditional love and sacrifice for me. Special thank to my wife for all supports in my life. Thank you for bearing my bad temper during the last few months. Of course, tiny little Victor is also on my acknowledgment list. Your smiling little face always encourages me.

Yangxurui Liu Lund, February 2018

# Acronyms and Mathematical Notations

**AGU** Address Generation Unit

**ASIC** Application Specific Integrated Circuit

**AWGN** Additive White Gaussian Noise

**BER** Bit-Error-Rate

**CAS** Compare And Swap

CC Clock Cycle

**CDF** Cumulative Distribution Function

CPF Common Power FormatCPP Core Partial ProductsCSI Channel State Information

**DLP** Data Level Parallelism

**DRAM** Dynamic Random-Access Memory

**DSP** Digital Signal Processor

**DVFS** Dynamic Voltage and Frequency Scaling

ED Euclidean DistanceEQ Energy-QualityEVA Extended Vehicular A

FD-SOI Fully Depleted Silicon On InsulatorFDD Frequency Division DuplexingFDM Frequency-Division Multiplexing

FER Frame Error Rate

FFT Fast Fourier Transform

GPP General Purpose ProcessorGPU Graphics Processing Unit

ICI Inter-Carrier Interference

**IFFT** Inverse FFT

ILP Instruction Level ParallelismISI Inter Symbol Interference

KLT Karhunen-Loeve transform

LOS Line-Of-Sight

LSB Least Significant Bit

LTE-A LTE-Advanced

LuMaMi Lund University Massive MIMO testbed

MAC Multiply-ACcumulateMF Matched-Filtering

MIMO Multiple-Input and Multiple-Output

MMSE Minimum Mean Squared Error

MSB Most Significant Bit

MUX Multiplexer

**NLOS** Non-Line-Of-Sight

**OFDM** Orthogonal Frequency-Division Multiplexing

PE Processing Element

PLL Phase-Locked Loop

**PPGU** Permutation Pattern Generation Unit

PSDR Peak Signal-to-Distortion Ratio PSNR Peak Signal-to-Noise Ratio

QoS Quality of Service QRD QR Decomposition

RF Radio Frequency RGF Register File

**ROM** Read-Only Memory

**SE** Sign Extension Bit

SIMD Single Instruction Multiple Data

SISOSingle Input Single OutputSNRSignal-to-Noise power RatioSRAMStatic Random-Access Memory

TDD Time-Division DuplexTLP Task Level Parallelism

VLIW Very Long Instruction Word VLSI Very-Large-Scale Integration

VM Vector Memory VR Virtual Reality

**XOR** Exclusive-OR

**ZF** Zero-Forcing

- $(\cdot)^*$  Complex conjugate

- $(\cdot)^T$  Vector/matrix transpose

- $(\cdot)^H$  Hermitian transpose

- $(\cdot)^{-1}$  Matrix inverse

- $(\cdot)^{\dagger}$  Matrix pseudo-inverse

- $(\cdot)_2$  Binary form

- $(\cdot)_{ij}$  *ij*-th matrix element

- | · | Euclidean vector length

- $\|\cdot\|_2$   $\ell^2$ -norm

- ∝ Proportional

- ∞ Infinity

- $\approx$  Approximation

- Order of computational complexity

- $x \in \mathbb{S}$  The element x belongs to the set  $\mathbb{S}$

- det(A) Determinant of A

- [·] Ceiling

- | · | Floor

- $\oplus$  XOR

# Introduction

This thesis deals with the subject of wireless communication and digital circuit design. More specifically, this thesis discusses the implementation of digital baseband processing for the massive Multiple-Input and Multiple-Output (MIMO) system, a key component in the 5th generation of wireless communication systems.

Nowadays, most people have witnessed the revolutionary change of wireless communication and are enjoying the convenience brought to the humanity. With the current wireless standard, it is common for an individual to establish an Internet connection and hold a data-intensive application like video chat or online gaming with the help of a single handheld device. Meanwhile, the data-rate demands in the forthcoming applications, such as self-driving cars and mobile Virtual Reality (VR), exceeds the capability of the current standards.

Driven by this ever-increasing data-rate demands from emerging applications, the upcoming 5G is being studied. Since the frequency spectrum has become overcrowded and is highly priced, advanced transmission technologies and algorithms with sophisticated computing demands are being included in the 5G standard in a bid to improve spectrum efficiency.

Eventually, these complex algorithms have to be implemented by hard-ware, and digital baseband processors are one of the essential components for most current wireless transmission. It enables the reliable data exchange between transceivers. The complex algorithms pose a higher requirement on the performance of digital baseband processors. Luckily, the processing performance can be satisfied, to some extent, by the development of chip fabrication technology. Transistors are the building blocks of digital circuits, and its highest density is doubling approximately every two years [1]. The increase in the number of integrated transistors makes it possible to design a

2 Introduction

high-performance baseband processor.

However, hardware designers are encountering a number of challenges when building a baseband processor, such as low energy consumption and efficient data organization. Along with increased functionality, optimizing energy consumption of baseband processors attracts more attention, while primary concerns include battery-life, energy reservation, etc. Another challenge to the high-performance processor is the speed of data access rather than computing itself, which is also known as the long-lasting "Memory Wall" [2] problem.

The main content of this thesis is hardware implementation in the context of massive MIMO baseband processing. Massive MIMO is one of the candidate techniques used to achieve the aggressive 5G roadmap, which promises orders of magnitude improvements in both spectrum and transmitted energy efficiencies by deploying a large number of antennas at the base station side. This inevitable introduces complex matrix-wise operations and poses serious challenges to the mentioned energy consumption and data organization.

#### 1.1. SCOPE OF THE THESIS

The goal of this thesis is to tackle the hardware design challenges in designing the massive MIMO baseband processor. The main methodology is cross system, architecture, and circuits level optimization.

The central part of this thesis mainly addresses the following questions:

- How to lower the energy consumption of baseband processing by exploring features in the wireless channel?

- How to efficiently organize data to support a high degree of parallelism in massive MIMO digital baseband processing?

- How to exploit wireless propagation characteristics in order to lower the hardware requirement, e.g., reduce required memory capacity?

- How to implement an appropriate memory system for massive MIMO baseband processing?

Digital baseband processing includes many components such as digital front end, Orthogonal Frequency-Division Multiplexing (OFDM) modulation/demodulation, channel estimation, MIMO processing, interleaving/de-interleaving, error correction coding and decoding, etc. Among them, this thesis mainly focuses on the MIMO processing, i.e., detection and precoding.

#### 1.2. CONTRIBUTION AND THESIS OUTLINE

This thesis is not limited to performing optimization in several virtually separated levels, e.g., circuit level and algorithm level. Cross-level optimization is carried out to break these boundaries and enables a more optimized design of an overall system. For example, the wireless channel characteristics are generally utilized for designing algorithms, which only indirectly affect the hardware implementation. This thesis directly exploits the wireless channel characteristics to benefit hardware implementation.

This thesis consists of three parts. The first three chapters give an overview of the research field. Chapter 2 briefly introduces the area of wireless communication, including channel properties, wireless transmission technologies, and digital baseband processing algorithms. At the end of Chapter 2, the operations of baseband processing are profiled to make a connection between baseband processing and digital circuits. Chapter 3 is an overview of digital circuits design, explaining several hardware optimization schemes for better performance or energy efficiency.

Part I presents energy-quality scalable circuits and computing for wireless communication, including a flexible multi-mode multiplier and a resource scheduling scheme for the energy-quality trade-off.

Part II presents the design of a memory system for massive MIMO. The three chapters in this part describe techniques to support multi-mode access and memory compression, which are followed by demonstrating an area-efficient high-bandwidth on-chip memory system for massive MIMO.

#### PART I: ENERGY-QUALITY SCALABLE COMPUTING FOR BASEBAND PRO-CESSING

The concept of Energy-Quality (EQ) scalable computing is broad, which can be regarded as a new design dimension for energy reduction [3]. In practical cases, the "quality" of a system refers to the quality of provided service, which usually means the rate of errors or the speed of data transmission in the scope of wireless communication. There exists a potential trade-off between provided quality and energy consumption for a digital baseband processing. This thesis presents two enabling techniques for EQ scalable computing on both circuit and algorithm levels.

In digital signal processing, dynamic wordlength arithmetic units provide an opportunity for exploring the energy reduction with a trade-off between energy consumption and data accuracy. As the dominant arithmetic computing logic in the digital signal processing, a high-performance multi-mode multiplier, which supports three types of wordlengths, is presented.

From an algorithm perspective, switching between complex and simple algorithms provides flexible control of "energy-quality" trade-off. An algorithm

4 Introduction

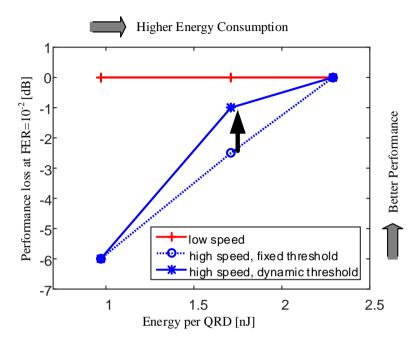

switching strategy is proposed to assign the available computing resource for the LTE-Advanced (LTE-A) downlink channel processing. In order to achieve energy optimization while keeping a stable throughput, this strategy is combined with the use of Dynamic Voltage and Frequency Scaling (DVFS). The proposed solution is evaluated using an in-house reconfigurable baseband processor [4].

The contents of Part I are based on the following publications:

- Y. Liu, L. Liu, V. Öwall, and S. Chen, "Implementation of a dynamic wordlength SIMD multiplier," 2014 NORCHIP, Tampere, 2014, pp. 1-4.

- Y. Liu, H. Prabhu, L. Liu, and V. Öwall, "Adaptive resource scheduling for energy efficient QRD processor with DVFS," in 2015 IEEE Workshop on Signal Processing Systems (SiPS), 2015, no. 2, pp. 1–6.

# PART II: MEMORY SYSTEM FOR MASSIVE MIMO BASEBAND PROCESSING

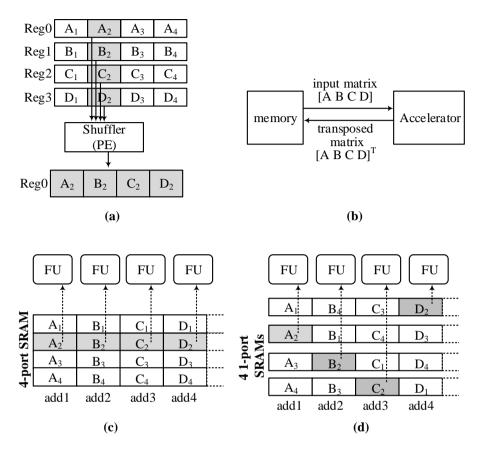

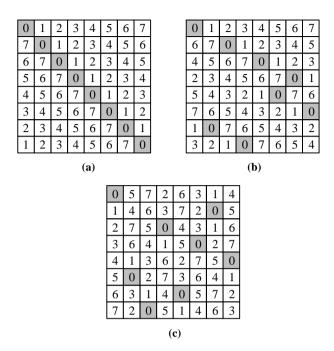

This part presents efficient data organization for massive MIMO baseband processing. Massive MIMO baseband processing algorithms contain matrixwise operations, leading to a variable of memory access modes. Moreover, large-size channel matrices require large memory capacity and high memory bandwidth. The contribution of this work includes a parallel memory system and the corresponding data allocation scheme to handle the large matrices in massive MIMO. Moreover, channel data compression algorithms are studied for saving on-chip memory. As a case study, a heterogeneous memory system enabling both compression and flexible access has been implemented.

The contents of Part II are based on the following publications:

- Y. Liu, O. Edfors, L. Liu, and V. Öwall, "Reducing On-chip Memory for Massive MIMO Baseband Processing using Channel Compression," in 2017 IEEE 86th Vehicular Technology Conference: VTC2017-Fall, 2017.

- Y. Liu, L. Liu, and V. Öwall, "Architecture Design of a Memory Subsystem for Massive MIMO Baseband Processing," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 10, pp. 2976-2980, Oct. 2017.

- Y. Liu, O. Edfors, L. Liu, and V. Öwall, "An Area-efficient On-chip Memory System for Massive MIMO using Channel Data Compression," (submitted to IEEE Transactions on Circuits and Systems I: Regular Papers)

# Digital Baseband Processing

In recent decades, wireless transmission technology has released a booming evolution and is pacing with the "Information Age" which deeply influences human life. Mobile communication standards are updated from generation to generation about every ten years. The first generation cellular phone system (1G), Nordisk MobilTelefoni (NMT), provided a voice-only transmission in 1981 [5]. Launched in 1991, the second generation (2G) replaced the analog modulation with digital communications, leading a transmission speed of 10 kbit/s. The third generation (3G) provides data transmission at rates of 144 kbit/s~ 5 Mbit/s, which is comparable to cable modems [6]. This datarate boosting continues, and the current standard (4G) has reached a peak download speed of 1 Gb/s. The upcoming standard (5G) promises a speed of more than 10 Gb/s and is planned to be commercially deployed at around 2020.

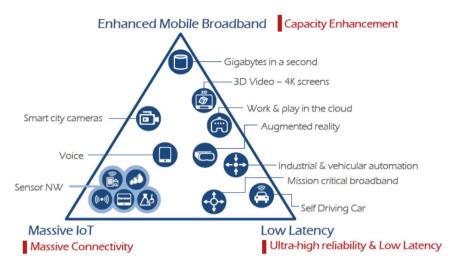

Though 5G is still under standardization process, theoretical analysis and field tests have verified the effectiveness of several key enabling technologies. 5G not only promises increases in data rates but also in coverage, spectral efficiency, number of supported devices, combined with a significant reduction in latency. These promising benefits are enabling many new applications that require intensive data exchange, including self-driving cars, mobile VR, real-time high-definition video, etc., as shown in Figure 2.1. It is hard to imagine how to approach these applications without 5G.

To be able to deploy, wireless technologies have to be mapped to the processors first. Before going into the details of hardware implementation, this chapter briefly introduces concepts in the field of wireless communication, including wireless channels, candidate transmission techniques, and digital baseband processing. In the end, a short operation profile on digital baseband processing is discussed.

**Figure 2.1.** Promised applications of 5G for 2020 and beyond (source: www.itu.int).

#### 2.1. WIRELESS CHANNEL

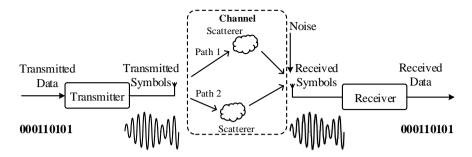

Figure 2.2 illustrates a model of wireless communication systems. To transmit information through the atmosphere, the transmitter converts the digital data into analog waveforms. Those waveforms then propagate in the atmosphere in the form of electromagnetic waves and are received by antennas at the receiver side. On their way from transmitters to receivers, signals are reflected and scattered by objects, such as large buildings and mountains. This results in multiple transmission paths between transmitting and receiving antennas, which is referred as multi-path propagation [7]. Based upon the received distorted and noisy signals, the receiver estimates transmitted data with as few errors as possible. An error occurs when the distortion and noise become so serious that the detection result at the receiver side is different from transmitted data. Bit-Error-Rate (BER) is an important parameter to quantify the transmission quality, which is the number of error bits divided by the number of transmitted bits.

The channel capacity,  $\mathcal{C}_{channel}$ , is an important parameter to describe a transmission system, which represents the highest data-rate at which information can be reliably transmitted. For example, according to the Shannon–Hartley theorem [8], the capacity of an Additive White Gaussian Noise (AWGN) Single Input Single Output (SISO) non-fading channel is

$$C_{\text{channel}} = \mathcal{B}\log_2(1+\gamma) \text{ [bit/s]},$$

(2.1)

2.1. Wireless Channel 7

Figure 2.2. Illustration of a wireless digital communication system model.

where  $\mathcal{B}$  is the physical bandwidth in the frequency domain, and  $\gamma$  is the received Signal-to-Noise power Ratio (SNR). SNR is usually expressed in decibels (dB),

$$\gamma_{\rm dB} = 10\log_{10}\gamma,\tag{2.2}$$

and we use dB to quantify SNR in this thesis.

One important fact which can be observed from (2.1) is that the capacity  $\mathcal{C}_{channel}$  linearly increases with the bandwidth  $\mathcal{B}$ . From the 2G standard to the current 4G standard, it is one of the preferred methods of data-rate speedup. The bandwidth expands  $500\times$  from  $20\,\mathrm{kHz}$  in the 2G standard to  $100\,\mathrm{MHz}$  in the 4G standard.

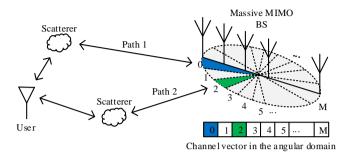

#### MULTI-PATH PROPAGATION

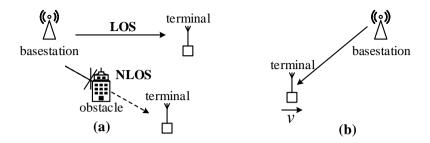

Propagation paths can be abundant in real life, and each path has a distinct attenuation, phase shift, angle of departure at the transmitter, and angle of arrival at receiver. Received signals are the sum of transmitted signals from all propagation paths. One important classification method for propagation environments is whether there is a Line-Of-Sight (LOS) connection between transmitter and receiver. Figure 2.3(a) shows illustrations of LOS and Non-Line-Of-Sight (NLOS) conditions. In NLOS conditions, the LOS path is blocked by obstacles, such as buildings, mountains, or trees.

Since the lengths of transmission paths vary in multi-path propagation environments, a transmitted signal arrives at the receiver as multiple copies at different times. This results in that signals are super-positioned at the receiver and may add up both constructively or destructively. The received signal dispersion leads to Inter Symbol Interference (ISI). In the early standards (e.g., 2G), the ISI causes errors and need to be fixed by an equalizer. However, in recent years, the multi-path propagation has been exploited to increase data rates by deploying multiple antennas, and this will be described later.

Figure 2.3. (a) LOS and NLOS conditions. (b) Illustration of Doppler shift.

#### TIME-VARIANT CHANNELS

In general, signal attenuations and phase shifts of propagation paths change with time. This may be caused by the movement of transmitter or receiver. Even if the transmitters and receivers are fixed, scatterers may move. These conditions bring up time variations in wireless channels.

If we consider the base station as a reference, the relative movement of the terminal (see Figure 2.3(b)) leads to a change in the frequency of a received signal, called the Doppler shift. The frequency shift is proportional to the speed of the terminal in the direction of signal propagation. The maximum Doppler shift ( $f_{\rm max}$ ) occurs when the direction of terminal movement is aligned with the direction of signal propagation and can be expressed as

$$f_{\text{max}} = f_{\text{c}} \frac{v}{c_0},\tag{2.3}$$

where  $f_c$  is the transmitted signal frequency, v the the terminal speed, and  $c_0$  the speed of light. The coherence time ( $T_c$ ) quantifies the time variation of the channel, i.e., how fast the channel changes. In general, it can be approximated as

$$T_{\rm c} \approx \frac{1}{f_{\rm max}}.$$

(2.4)

#### 2.2. WIRELESS TRANSMISSION TECHNOLOGIES

Due to the frequency-selective nature of multi-path propagation channels [9], splitting a wide bandwidth channel to several narrower ones, e.g., using OFDM [10], greatly alleviates the effect of ISI when compared to a single wideband carrier channel. Since the available bandwidth resource is limited, the spatial resource is utilized to boost the data-rate in addition to the frequency domain. For example, MIMO increases the capacity using multiple transmit

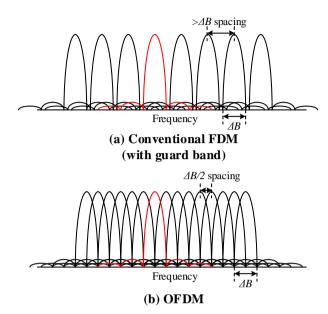

**Figure 2.4.** Subcarriers in conventional FDM and OFDM.  $\Delta B$  is the bandwidth of subcarriers.

and receive antennas. MIMO and OFDM technologies are jointly deployed in the current 4G standard and are under consideration for the upcoming 5G.

#### 2.2.1. ORTHOGONAL FREQUENCY-DIVISION MULTIPLEXING

In 1966, Chang [10] proved that Inter-Carrier Interference (ICI) free multiplexing can be performed in the frequency domain with overlapping spectra – a principle later adopted in OFDM. The OFDM scheme is one of the Frequency-Division Multiplexing (FDM) schemes which use several parallel subcarriers to carry data. The key idea of FDM is to divide the occupied bandwidth into several subcarriers without introducing ICI. Unlike the non-overlapping property in FDM, subcarriers in OFDM are closely spaced and overlapping in the frequency domain but still orthogonal to each other subcarriers, as illustrated in Figure 2.4. Because of this arrangement, the spectral efficiency of OFDM schemes is higher than of conventional FDM schemes. Another advantage of OFDM is that its orthogonality allows the modulator and demodulator to be efficiently implemented using the Fast Fourier Transform (FFT).

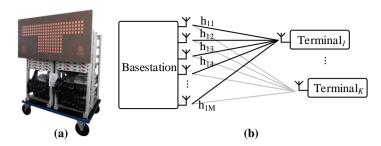

Figure 2.5. Illustration of small-scale MIMO system: (a) A four-antenna MIMO router (source http://www.tp-link.se) (b) System model of a  $4\times4$  MIMO.

#### 2.2.2. SMALL-SCALE MIMO SYSTEMS

By exploiting the characteristic of multi-path propagation in the spatial domain, MIMO multiplies the capacity of transmission in the same bandwidth by using multiple transmitting and receiving antennas [11][12]. Similar to OFDM, it is a popular component in current wireless transmission standards, including IEEE 802.11n and IEEE 802.11ac (Wi-Fi), HSPA+ (3G), LTE (4G), etc [13][14]. Since the numbers of antennas at each side are usually less than ten under current standards, this kind of MIMO systems is referred as small-scale MIMO systems in this thesis. An important usage of small-scale MIMO systems is called spatial multiplexing, where each antenna transmits independent data signals separately to boost the data rate [12]. It is necessary to note that simultaneously supporting multiple users with small-scale MIMO, i.e., Multi-user MIMO [15], is excluded from this thesis.

Figure 2.5 illustrates a  $4 \times 4$  MIMO system. Considering an  $M \times M$  narrowband MIMO system, the received signals  $\mathbf{y} = [y_1, y_2, y_3, ..., y_M]^T$  can be expressed as

$$\mathbf{y} = \mathbf{H}\mathbf{x} + \mathbf{n}$$

$$= \begin{bmatrix} h_{11} & h_{12} & h_{13} & \dots & h_{1M} \\ h_{21} & h_{22} & h_{23} & \dots & h_{2M} \\ h_{31} & h_{32} & h_{33} & \dots & h_{3M} \\ \dots & \dots & \dots & \dots \\ h_{M1} & h_{M2} & h_{M3} & \dots & h_{MM} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \\ x_3 \\ \dots \\ x_M \end{bmatrix} + \begin{bmatrix} n_1 \\ n_2 \\ n_3 \\ \dots \\ n_M \end{bmatrix},$$

(2.5)

where  $\mathbf{H} \in \mathbb{C}^{M \times M}$  is the complex Channel State Information (CSI) matrix representing the propagation between each transmitter and receiver antenna, and  $h_{ij}$  encapsulates the attenuation and phase shift between the j-th transmitting antenna and the i-th receiver antenna in a singe complex number.  $\mathbf{x} \in \mathbb{C}^{M \times 1}$  is the transmitted signal and  $\mathbf{n} \in \mathbb{C}^{M \times 1}$  the noise vector. Due to the multi-path

**Figure 2.6.** Illustration of massive MIMO system: (a) An assembled massive MIMO testbed at Lund University (LuMaMi) [16] (b) System Model of an  $M \times K$  system.

propagation, the amplitude and phase of each  $h_{ij}$  can be distinct.

When the transmitter is unaware channel information and all the transmitter antennas are assigned equal power, the capacity of the spatial-multiplexing MIMO system becomes

$$C = \log_2 \left[ \det \left( \mathbf{I}_M + \frac{\gamma}{M} \mathbf{H} \mathbf{H}^H \right) \right] [\text{bit/s/Hz}], \tag{2.6}$$

where  $I_M$  is an  $M \times M$  identity matrix. Assuming a full rank H and M identical eigenvalues, the capacity results in

$$C = M\log_2(1+\gamma) [\text{bit/s/Hz}]. \tag{2.7}$$

The above equation shows that capacity is linearly proportional to the number of antennas. MIMO is one of the preferred methods to increase data-rate, and the maximum MIMO configuration is up to  $8 \times 8$  in the current LTE-A standard.

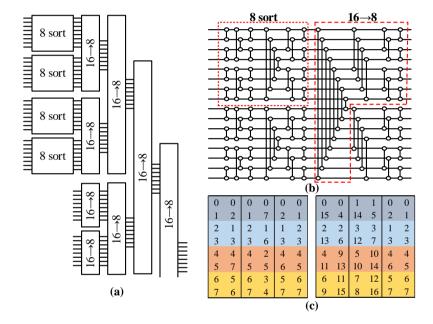

#### 2.2.3. MASSIVE MIMO SYSTEMS

Though more antennas lead to a higher transfer rate, it is infeasible to deploy many antennas on handheld terminals like cell phones, because of the limited physical size. In order to further increase the data rate of the entire cell, massive MIMO (also known as Large-Scale Antenna Systems or Very Large MIMO) is a promising technology for the next generation mobile network (5G) [17]. Most massive MIMO systems are assumed to have an antenna arrays containing hundreds of antennas at the base station while serving ten or even more single-antenna terminals. In 2010, Marzetta [18] first discussed the possibility of increasing the number of antennas in the base station to further exploit the spatial domain resource. Results show that the inter-user interference disappears when the number of base station antennas grow without

bounds. After that, relevant research has been conducted continuously during the past few years, and several testbeds have been established as a proof-of-concept, including Argos [19], LuMaMi [16], etc. These studies have shown that massive MIMO gives a great improvement over existing 4G system in terms of spectral efficiency.

An M antenna massive MIMO base station serving K single-antenna terminals is shown in Figure 2.8(b). The user-received downlink signal  $\mathbf{y} \in \mathbb{C}^{K \times 1}$  is

$$y = Hx + n, (2.8)$$

where  $\mathbf{H} \in \mathbb{C}^{K \times M}$  is the downlink CSI matrix,  $\mathbf{x} \in \mathbb{C}^{M \times 1}$  the transmitted signal from the M base station antennas, and  $\mathbf{n} \in \mathbb{C}^{K \times 1}$  the noise. In most cases, we assume M >> K to achieve better inter-user inference cancellation in massive MIMO. In the downlink, precoding is employed to separate data streams for each user, i.e., to eliminate inter-user interference.

Under above assumptions, linear precoding has a near-optimal performance and can be expressed as

$$\mathbf{x} = \mathbf{W}\mathbf{s},\tag{2.9}$$

where  $\mathbf{W} \in \mathbb{C}^{M \times K}$  is the precoding matrix and  $\mathbf{s} \in \mathbb{C}^{K \times 1}$  is the K symbols to the users to be precoded.

For our simplified case, with equal power allocation among users, the achieved capacity becomes [20]

$$C = \sum_{i=1}^{K} \log_2 \left( 1 + \frac{\gamma \left| [\mathbf{HW}]_{i,i} \right|^2}{\gamma \sum_{\substack{j=1\\j \neq i}}^{K} \left| [\mathbf{HW}]_{i,j} \right|^2 + M} \right).$$

(2.10)

Massive MIMO has great advantages when compared to conventional small-scale MIMO. In summary, these advantages include but not limited to:

- Large Capacity: The aggressive spatial multiplexing scheme in massive MIMO can increases the capacity by ten times or more.

- Inter-user Interference Canceling: When M >> K and  $M \to \infty$ , the rows of **H** become asymptotically orthogonal, and thereby we have

$$\mathbf{H}\mathbf{H}^{H}\approx M\mathbf{I}_{K}.\tag{2.11}$$

Assuming a precoding matrix  $\mathbf{W} = \mathbf{H}^H$ , the received signals can be expressed as

$$\mathbf{y} \approx M\mathbf{s} + \mathbf{n},\tag{2.12}$$

where the inter-user interference is eliminated.

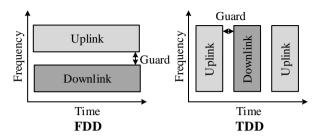

Figure 2.7. FDD and TDD system.

- **Power Efficiency:** The transmitted power in a massive MIMO system can be scaled down proportionally to the number of antennas in the base station without loss of performance when compared to a SISO system [21].

- Cheaper Hardware: With massive MIMO, the high-power and expensive amplifiers used in small-scale MIMO system for driving the antennas can be replaced by many low-power and cheap amplifiers. Besides, the accuracy requirement of each amplifier is relevantly reduced.

- Channel Hardening: With the large number of antennas at the base station, the spatial diversity leads a fading channel behaves like a non-fading channel [22], i.e., channel hardening. It improves the reliability of the transmission in massive MIMO.

#### **FDD AND TDD**

Figure 2.7 shows the main methods for duplexing in cellular networks, namely Frequency Division Duplexing (FDD) and Time-Division Duplex (TDD). In an FDD system, the uplink and downlink signals are transmitted at different frequencies. TDD systems allocate different time slots for uplink and downlink on the same frequency. Both TDD and FDD have advantages and disadvantages [23]. For example, FDD provides a higher coverage than TDD, thereby needs fewer base stations to cover same area [24]. Besides, up and downlink channels in TDD systems can be considered reciprocal and the need for CSI feedback can be eliminated. In FDD, receivers have to feed back CSI to transmitters if CSI is needed at the transmitter side, since the uplink and downlink located on different frequencies and uncorrelated.

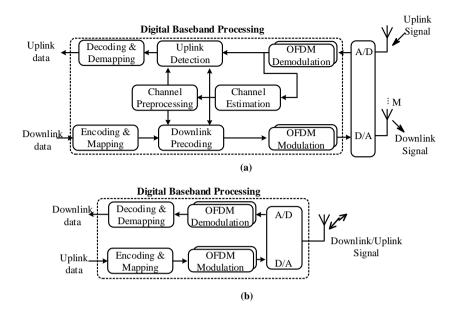

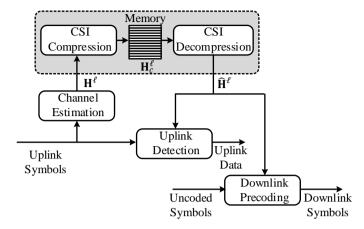

**Figure 2.8.** Block diagram of the TDD OFDM massive MIMO (a) base station (b) terminal.

#### 2.3. OVERVIEW OF DIGITAL BASEBAND PROCESSING

Advanced wireless technologies provide the possibility of transmitting a large amount of data in the atmosphere. In real implementations, all these technologies build on digital baseband processing to detect "what was sent" and decide "what should be sent." In this section, we discuss the digital baseband system in the context of massive MIMO while taking small-scale MIMO as a reference. Since the standardization progress of 5G is still on-going, we make assumptions that except the massive MIMO concept, most features and data flows are inherited from 4G standard in the baseband processing. Figure 2.8 shows the schematic of a TDD OFDM massive MIMO system, where the upper half represents the base station and lower part represents the single-antenna terminal. For simplicity, most non-digital components are omitted in the figure, including the RF front-end. The A/D and D/A perform the conversion between analog signals and digital data per antenna.

#### 2.3.1. BASE STATION SIDE

The base station and terminals both play the role of transmitters and receivers. For small-scale MIMO, channel estimation and detection appear on both sides. while most digital baseband processing, especially the MIMO processing part

in TDD massive MIMO is centered at the base station.

#### OFDM MODULATION/DEMODULATION

OFDM demodulation collects the sampled time-domain digital signals from the uplink and transforms them to frequency-domain (aligned by subcarriers) using an FFT. In contrast, OFDM modulation transforms the frequency-domain data to the time-domain using an Inverse FFT (IFFT). For small-scale MIMO or massive MIMO systems, each antenna needs an OFDM modulator/demodulator pair.

#### CHANNEL ESTIMATION

The base station relies on the knowledge of channel information (often represented as a CSI matrix) to precode the downlink symbols and detect the uplink data. The principle of channel estimation is to estimate how the channel attenuates and rotates known signals, e.g., pilots, during transmission.

#### DOWNLINK PRECODING

Unlike small-scale MIMO, the downlink symbols require additional precoding in massive MIMO. There are three commonly-used linear precoding schemes, Matched-Filtering (MF), Zero-Forcing (ZF) and Minimum Mean Squared Error (MMSE) [25]. The formula expressions of these schemes can be presented as

$$\mathbf{W} = \begin{cases} \mathbf{H}^{H} & \text{MF} \\ \mathbf{H}^{\dagger} = \mathbf{H}^{H} (\mathbf{H} \mathbf{H}^{H})^{-1} & \text{ZF} \\ \mathbf{H}^{H} (\mathbf{H} \mathbf{H}^{H} + \alpha \mathbf{I}_{K})^{-1} & \text{MMSE.} \end{cases}$$

(2.13)

Among them, the MF scheme maximizes the received SNR at each terminal while the ZF scheme eliminates the inter-user interference. In between these two, MMSE is a compromise scheme that makes a trade-off between the SNR and canceling the inter-user interference, where  $\alpha$  is a parameter relevant to SNR.

Sending pilot symbols from every antenna in a base station consumes more time than from users. Therefore, channel estimation in downlinks takes more resource than in uplinks. In (2.13), the precoding matrix **W** is computed based upon the downlink CSI matrix **H**. However, it is a great burden for a massive MIMO system to obtain channel information through channel estimation in the downlink. Furthermore, the channel estimation results need to be fed back from each user through the uplink, occupying precious time and frequency resources. Therefore, in a TDD massive MIMO system, the downlink CSI matrix is usually obtained from the uplink CSI matrix with the reciprocity property of the channel [26].

#### **UPLINK DETECTION**

In a MIMO system, detection is based on the consideration of all received signals from antennas. It becomes more complicated with the increased number of antennas. Detection can be categorized as linear and non-linear. Non-linear detection is more complex than linear detection. For a small-scale MIMO, non-linear detector, i.e., sphere detectors [27], is used for its near-optimal performance.

In massive MIMO, simple linear detectors also provide good performance. Similar to downlink precoding, detectors include MF, ZF, or MMSE are usually used in the uplink detection. Non-linear detections are rarely used since the complexity has an exponential increase with the number of antennas.

#### 2.3.2. TERMINAL SIDE

In small-scale MIMO systems, the baseband component in the base stations and terminals are mostly symmetric, i.e., both are equipped with channel estimation and data detection. However, in massive MIMO systems, most computation-intensive operations are allocated in the base station side. On the terminal side, most data detection and channel estimation are trivial in nature, and no precoding is demanded. Since most power consuming baseband processing is omitted, one direct benefit is the extension of terminal battery life.

#### 2.4. OPERATION PROFILING

Table 2.1 lists the most common operations and their computational complexity in baseband processing for massive MIMO. For example, OFDM modulation/demodulation introduces FFT/IFFT, and the downlink precoding in (2.13) introduces matrix-wise multiplications, additions, and inversions. Most listed operations are matrix-wise or vector-wise, and most operands are represented in complex-valued format. In Table 2.1, vector- and matrix-wise operations have operand vectors of length n and operand matrices of  $n \times n$ , respectively.  $\mathcal{O}(\cdot)$  represents computational complexity. For example, matrix multiplications have a computational complexity of  $\mathcal{O}(n^3)$  which denotes the number of scalar multiplications in one  $n \times n$  matrix multiplication is proportional to  $n^3$ .

The sizes of input data are proportional to or equal to the number of users or antennas in the base station, which is single-digit in small-scale MIMO and comes to a magnitude of hundreds in massive MIMO. Since the complexity order of operations is on  $\mathcal{O}(n^2) \sim \mathcal{O}(n^3)$ , overall computational complexity has a significant increase when n grows from four to hundreds. From hard-

ware point of view, this sophisticated computing in combination with the hard timing constraints poses a great challenge to the computational performance of processors

#### TIMING CONSTRAINTS

In digital baseband processing, all listed operations are repetitively executed with respect to a strict computing deadline. The processing requirement is real-time, and latency constraints are usually very strict. Containing one or multiple operations, each baseband stage processes results from previous stages and pass the output to the next stage as input.

The expected latency of 5G system is as low as 1 ms [29]. In this regard, the time left for digital baseband processing is on the order of hundreds of microseconds. Within this time constraint, digital baseband processors have to perform OFDM demodulation, channel estimation, downlink precoding, and OFDM modulation. Failing to comply with timing constraint in any stage, e.g., fail to accomplish OFDM modulation before the corresponding symbol has to be transmitted, the frame structure will become corrupt, and the overall system will not be able to transmit or receive data.

#### INTENSIVE DATA FLOW

The sizes of input and output data are proportional to the number of users or antennas in the base station. For example, CSI matrices  $\mathbf{H}$  are rapidly updating and frequently accessed. The CSI matrix size of a  $128 \times 16$  massive MIMO system is about one hundred times larger than a  $4 \times 4$  small-scale

| Data Type    | Operation                   | Complexity                |

|--------------|-----------------------------|---------------------------|

|              | FFT/IFFT                    | $\mathcal{O}(n\log_2 n)$  |

|              | Vector Addition/Subtraction | $\mathcal{O}(n)$          |

| Vector-Wise  | Vector Multiplication       | $\mathcal{O}(n)$          |

|              | Sorting                     | $\mathcal{O}(n \log_2 n)$ |

|              | Selection                   | $\mathcal{O}(n \log_2 n)$ |

|              | Matrix Multiplication       | $\mathcal{O}(n^3)$        |

| Matrix-Wise  | Matrix Addition/Subtraction | $\mathcal{O}(n^2)$        |

| watrix-vvise | Inversion                   | $\mathcal{O}(n^3)$        |

|              | QRD, SVD                    | $\mathcal{O}(n^3)$        |

**Table 2.1.** Operations and their Complexity in the Digital Baseband [28]

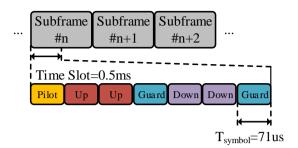

MIMO in the 4G standard. In the 4G standard, the refreshing interval of CSI matrices is about 0.25 ms, which is the same order of magnitude in massive MIMO since we expect them to operate under the same conditions.

#### MULTIPLICATION DOMINATED COMPUTING

Multiplications, or more specifically, Multiply-ACcumulate (MAC) are the most common function in digital baseband algorithms. It not only exists in vector-wise and matrix-wise multiplications, but also in FFTs, matrix decompositions, and even matrix inversions. Besides, it is quite easy to find data-level parallelism where several multiplications can be executed simultaneously.

#### **PREDICTABILITY**

With a few exceptions, operations in digital baseband processing are highly regular and predictable. First of all, the size of input and output data in each stage as well as desired processing speed are fixed. Secondly, the execution time of each operation is determined. Programmers and hardware designers can accurately estimate the execution time of each stage. At last, data access patterns are predicable and irrelevant with inputs. For example, the (2.9) explicitly denotes a multiplication between **W** and **s** without alternatives.

This chapter reviewed basic concepts of wireless communication and discussed the digital baseband processing part in massive MIMO. The operations in the MIMO processing are characterized. Let us now look at the hardware-level implementation of these algorithms.

## **Digital Integrated Circuit**

After its invention in the 1950s, the integrated circuit has been put into the newly invented computer system. Mainly due to the semiconductor device fabrication technology, the computational performance of processors has been improved at an explosive speed. Advances in fabrication technology shrink the size of transistors, enabling more transistors to be integrated on a chip. According to Moore's prediction in 1965, the number of transistors on one chip is doubling almost every two years<sup>1</sup>. This is known as "Moore's Law" and has been proved to be true during the last decades. For example, the transistor count of the Intel Broadwell Xeon produced in 2017 exceeds 7.2 billion, approximate 1000 times more than the Intel Pentium II Klamath which was introduced 20 years ago.

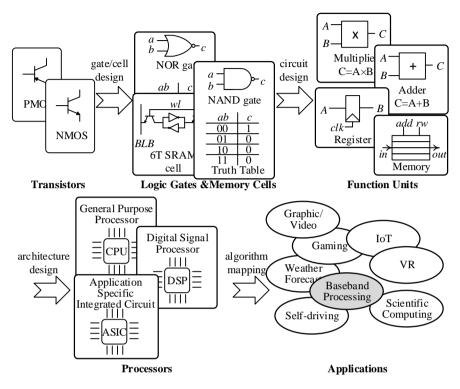

In a modern processor, most components are digital circuits, and all information is coded in a binary form<sup>2</sup>, where high voltage represents "1," and low voltage represents "0." Figure 3.1 abstracts different design level for digital integrated. Logic gates are generally considered as the basic unit in large scale integrated digital circuits. Usually, designers use standard cell libraries supplied by fabricators to reduce the design time and improve reliability. With logic gates, designers can build up a variety of complex functional units, e.g., multipliers which product the multiplication of inputs and registers which store the data temporarily. At a higher level, connected functional units compose processors, which can be classified according to its architectures and target applications. One example is the well-known General Purpose Processor (GPP), which is designed for multiple applications and provides high

<sup>&</sup>lt;sup>1</sup>He predicted a doubling every year first and then revised to doubling every two years.

<sup>&</sup>lt;sup>2</sup>There exists ternary systems [30], but they are only for research purpose now.

Figure 3.1. Design levels for digital circuits designers.

programmability. Another example is Application Specific Integrated Circuit (ASIC), which is customized for a particular application. It is usually not programmable and has high efficiency.

During the design stage, hardware designers are responsible to jointly consider design specifications and hardware constraints. A suitable Very-Large-Scale Integration (VLSI) architecture need to be chosen while ensuring the functionality of applications. The most common design specifications include latency, throughput, flexibility, accuracy, etc. From hardware aspects, the processor is limited by power consumption, chip area, price budget, and available fabrication technology, etc. Advanced fabrication technology allows designers to place transistors at a higher density, providing more computational capacity. However, the expense per unit area increases significantly with more advanced fabrication nodes.

The application specification and hardware constraint mutually influence each other. For example, high throughput applications generally require high degree of parallelism in circuit and high working clock frequency, which lead

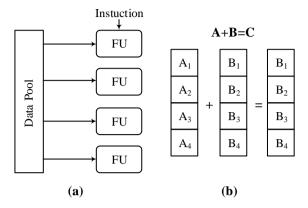

**Figure 3.2.** An illustration of SIMD with four functional units, (a) SIMD hardware (b) arithmetic form.

to a larger area and higher power consumption. In this chapter, we will survey popular technologies employed in modern processors, including architecture level and circuits level, which are relative to baseband processing as a background introduction. In the discussion of each technology, we will first review how these technologies are used in other applications and then discuss more specifically the application of baseband processing.

#### 3.1. ARCHITECTURE LEVEL TECHNOLOGIES

#### 3.1.1. PARALLEL COMPUTING

The concept of parallel computing has been exploited for decades and is one of the widely used methods to improve the throughput and energy efficiency. For computing-intensive applications, exploiting the possibility of parallel execution is an essential approach to accomplish the latency and throughput requirement.

For programmable processors, the possible parallelism can be categorized into Instruction Level Parallelism (ILP), Data Level Parallelism (DLP), and Task Level Parallelism (TLP). ILP is mainly exploited by executing more than one instruction simultaneous. Examples are Superscalar [31], where the instruction issue is controlled by hardware, and Very Long Instruction Word (VLIW) [32], where the parallelism among instructions are exploited by the compiler. TLP is mainly utilized in a multi-core system that runs multiple tasks across different cores simultaneously.

The main scope of this thesis is focused on DLP, which largely exists in baseband processing for wireless communication.

As is listed in Table 2.1, algorithms of MIMO digital baseband processing are mostly vector-wise operations and matrix-wise operations and full of DLP. One of the most popular architectures for exploiting DLP is Single Instruction Multiple Data (SIMD) [33]. Such architectures have been widely used in mainstream processors, such as GPP, Graphics Processing Unit (GPU), and Digital Signal Processor (DSP). Illustrated in Figure 3.2, a SIMD architecture executes the same instruction on multiple functional units simultaneously. The right side of Figure 3.2 shows a typical instruction of vector addition. Two vectors of length four are taken as inputs, and the addition is accomplished with only one single instruction. Before execution, the two operand vectors must be loaded in the same order which may require additional shuffling.

SIMD harvests a direct speedup without introducing complex control logic. The theoretical speedup rate equals to the number of functional units. In terms of energy reduction, the energy consumed by the control logic, e.g., instruction fetch and decoding, is apportioned by multiple operations, thereby the energy consumption per operation is decreased. Although SIMD provides both performance improvement and energy reduction, its efficiency is restricted by the following factors in practical applications [34]. First of all, SIMD only exploits DLP of the algorithms. For an application that is lacking DLP, the utilization of aligned functional units with the same functionality will not be used efficiently. Secondly, it is very important for a SIMD processor to have all the operands ready for execution simultaneously. This may lead to unaligned memory access or introduce extra waiting time for data fetch. Besides, the degree of DLP is not always a multiple of SIMD width, which means that the utilization of functional units is not always 100% during execution.

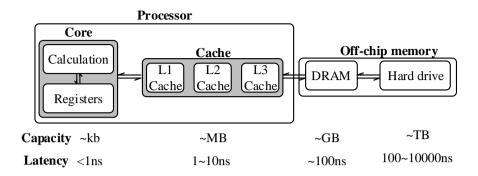

#### 3.1.2. MEMORY HIERARCHY

In order to hold inputs and intermediate results during computations, digital integrated circuit constitutes memories and registers to store information. The data organization method, i.e., memory hierarchy, has a great impact on the performance of the entire processor. This subsection briefly introduces common memory hierarchies and its characteristics.

In most modern processors, data is expressed in a binary string, and the smallest unit is a bit. Bit information is stored in two-state storage devices composed of several transistors. The capacity of storage devices is defined in terms of bits, e.g., kilobit(kb), megabit(Mb).

Data storage devices can be classified into registers, Static Random-Access Memory (SRAM), Dynamic Random-Access Memory (DRAM), Read-Only Memory (ROM). Two important properties of storage devices are latencies and throughputs. Latencies are the delay between the read/write request and

the moment of request accomplishment. Throughputs are defined as the size of accessed data per unit time. Faster storage devices usually have a higher hardware cost and thus smaller capacity, and slower storage devices usually have a smaller hardware cost and higher capacity. For example, registers generally consist of dozens of transistors and has a latency of nanoseconds. On the other hand, DRAMs have higher density and lower hardware cost cells which consist of down to one transistor and one capacitor for storing each bit. Memory systems consist of one or multiple memory banks, which are pieces of individual circuits with independent addressing.

As been discussed, parallel computing speeds up the calculation while expecting that all the operands are available immediately. In practice, the idea of speedup by unlimitedly expanding the number of parallel functional units is always limited by the data supply bandwidth. Therefore, a multilevel memory hierarchy, composed of a variety of memories with different sizes and speeds, is an economical and practical method to organize data and has been widely used in modern processors. The main goal is to reduce the hardware cost per bit to the cheapest memories while providing a speed close to fastest memories.

Figure 3.3 shows the levels of memory hierarchies as well as the typical capacity and response time. Memories are mapped in a sequence from faster and smaller to slower and larger, where registers are directly connected with calculation units. Typically, most off-chip main memories consist of DRAMs, and nearly all caches are composed of SRAMs. In order to reduce latency, preloading before computing is necessary. When desired operands are not in registers, the computational progress will stall and wait until the operands are fetched from caches. If the operands are not in caches, then the access request will be passed to lower memory levels until being found. For most digital baseband processing, the data accesses are predictable. This property makes it possible to explicitly pre-fetch data without complex cache replacement policies used in GPPs.

#### 3.2. CIRCUIT LEVEL TECHNOLOGIES

The power consumption of processors increases significantly with ever more complicated functionality and higher performance, challenging the package, cooling system, and power delivery. An extreme example, TianHe-2 [35], which is one of the most powerful computers in the world, has a power consumption of 24 MW. This magnitude of power consumption equivalents to a medium-sized city and the cooling system consumes close to one-fourth of the power. For digital baseband processing, though the magnitude of power consumption is not as high as a supercomputer, lowering the power consumption

**Figure 3.3.** Typical memory hierarchy in a modern processor. Note that the size and speed are current typical numbers (in 2017) and great differences might exist depending on systems.

benefits in many domains, e.g., lower electricity costs and longer battery life for a mobile terminal. Power consumption has drawn the attention of hardware designer, and there are many low-power technologies in circuit level.

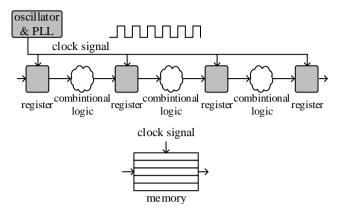

Most large-scale digital integrated circuits are synchronous. The global clock signal is generally used to conduct register level transfer. Generated by an electronic oscillator and Phase-Locked Loop (PLL), the clock signal repeatedly flips between "0" and "1" with a certain frequency (f). The time between two adjacent "0" to "1" flip is referred as the clock cycle (T). Illustrated in Figure 3.4, in synchronous circuits every storage units, including memories and registers, are connected with a broadcasted clock signal. The combinational logic which allocates between storage units is not connected by the clock signal. For such circuit, the total power consumption can be express as

$$P_{total} = \underbrace{\alpha C_{total} V_{DD}^{2} f}_{\text{dynamic power}} + \underbrace{I_{OFF} V_{DD}}_{\text{leakage power}}, \qquad (3.1)$$

where  $\alpha$  represents the activity factor of switching between 0 and 1,  $C_{total}$  the switching capacity,  $V_{DD}$  the supply voltage, and  $I_{OFF}$  the average leakage current [36]. Dynamic power is usually the dominant component of power consumption in a high-frequency and high switching activity processors.

Ideally, the clock edges arrive at all the storage units simultaneously, and thereby the calculation results of combinational logic are transferred through the storage units. To ensure correct functionality, synchronous circuits need to meet timing constraint that combinational logic latency should be smaller than the clock period. The propagation delay of combinational logic usually scales down if the  $V_{DD}$  increase, so parameters f and  $V_{DD}$  mutually restrict each other and can not be set arbitrarily.

**Figure 3.4.** Simplified illustration of synchronous circuit. Connections between memory, combinational logic and registers are largely simplified. For example, outputs of combinational logic can be connected to either other registers or other combinational logic in practice.

At the circuit level, a variety of methods can be deployed to optimize the power consumption. Here we discussed two commonly-used techniques as examples.

#### 3.2.1. CLOCK GATING AND POWER GATING

Switching off temporarily unused functional units is an effective method to reduce power consumption in modern processors, which does not impact the functionality or the throughput. Depending on whether turning off the power supply  $V_{DD}$  during the idle state, it can be classified as clock gating and power gating, respectively.

#### **CLOCK GATING**

In this content, turning off clock signals (clock gating) of unused blocks is an effective technique to save dynamic power consumption. It disables part of the circuit, so the switching activity becomes 0. Besides, since clock signals have a high fan-out and switch every clock cycle ( $\alpha = 1$ ), its distribution network accounts for a great potion of total power consumption, usually more than 40% [37].

#### **POWER GATING**

Power gating technique is proposed to further reduce the leakage power consumption, affecting architecture more than clock gating. By turning off the

supply voltage  $V_{DD}$  or ground of unused modules via control logic, power gating eliminates both dynamic power and leakage power consumption. However, when the module is waken-up from idle to active mode, the capacitance of power network takes a long time to recharge and increases delay.

#### 3.2.2. DYNAMIC VOLTAGE AND FREQUENCY SCALING

Besides clock-gating and power-gating, DVFS is another power saving technology, introduced in the 1990s [38]. The supply voltage and clock frequency used in a module are both dynamically adjusted, depending upon instantaneous workload. DVFS enables a trade-off between energy consumption and performance. In general, the energy consumption of a specific task, without considering of leakage power, can be expressed as

$$E_{task} \propto T_{exec} \dot{P}_{dynamic} = \alpha C_{total} n_{cc} V_{DD}^2, \tag{3.2}$$

where  $T_{exec}$  is the total execution time of the task, and  $n_{cc}$  is the corresponding number of clock cycles. According to (3.2), reducing supply voltage is a reasonable approach to reduce the energy consumption of a certain task, in a premise of being able to meet the timing constraint of the task. On the other hand, the available maximum clock frequency is proportional to the supply voltage  $V_{DD}$ . Their relationship can be express as

$$f_{max} \propto \frac{(V_{DD} - V_{th})^2}{V_{DD}},\tag{3.3}$$

where  $V_{th}$  is the threshold voltage. With DVFS, a processor can either provides high-performance or energy efficiency computing by switching the voltage and frequency. How to maintain the throughput when using DVFS is a major issue for applications like baseband processing that have a strict time constraint. The correlation the chosen frequency and instantaneous workloads need to be carefully considered.

In this chapter, several digital circuit design technologies are reviewed, including architecture and circuit levels. These technologies either increase computational speed, reduce power consumption of circuits, or provide a possible trade-off between computational speed and power consumption.

## Part I

# Energy-Quality Scalable Computing for Baseband Processing

With the slowdown of Moore's law [39], the energy down-scaling brought by advanced fabrication technologies is being challenged. Conventional approaches of energy-saving such as parallelism have become mandatory and exploited extensively. A new design dimension of trade-off has been recently proposed to enable further energy reduction, i.e., energy-quality scaling.

Traditionally, circuit and algorithms within a wireless system are designed under the guidance of meeting the worst-case demand. Due to the variable system requirement (e.g., BER) and external environment (e.g., SNR or Doppler shift), the trade-off between Quality of Service (QoS) and energy allows energy reduction by eliminating the excessive provided QoS.

From the system designers viewpoint, various design-levels can be exploited for the concept of energy-quality scaling. For example, in the functional unit level, precision adjustments and pruning the unused transistors is a direct method of saving energy. Another algorithm level example is to switch between accurate and approximate algorithms. In this chapter, we will discuss the energy-quality trade-off in the scope of the functional unit level and algorithm level. Results and discussion in this part are from the following papers:

- Y. Liu, L. Liu, V. Öwall, and S. Chen, "Implementation of a dynamic wordlength SIMD multiplier," 2014 NORCHIP, Tampere, 2014, pp. 1-4.

- Y. Liu, H. Prabhu, L. Liu, and V. Öwall, "Adaptive resource scheduling for energy efficient QRD processor with DVFS," in 2015 IEEE Workshop on Signal Processing Systems (SiPS), 2015, no. 2, pp. 1–6.

### Sub-word SIMD Multiplier

Wordlength refers to the number of bits for representing each operand. The accuracy of operands increases as the wordlength extends. Wordlength adjustment is a method to enable the trade-off between energy efficiency and processing accuracy. Longer wordlength brings a higher precision at a price of larger memories for storage, more complex computing logic, and larger bandwidth for data traffic. All of these hardware expanding demand a higher power consumption.

Sub-word parallelism is a method of packing multiple sub-word data as one full-length data. It enables run-time wordlength adjustment without significant overhead in hardware. In this way, the calculation blocks will work in in sub-word mode, but the other parts such as memories and data paths, will not change [40]. For the calculation, sub-word parallelism can be regarded as a dynamic length SIMD, which demands dedicated arithmetic units to support run-time switching between multiple sub-word calculations and one full-length calculation.

Sub-word parallelism allows a processor to boost calculation throughputs or reduce energy consumption when high precision is unnecessary. For baseband processing, adaptive controlling the precision of data according to current signal quality is an option to save energy [41]. Among kernel operations listed in Table 2.1, multiplications are the most indispensable operation where full of DLP that can be easily exploited. Dynamic wordlength multipliers provide an opportunity to explore energy reduction with minor accuracy loss. This chapter presents a dynamic wordlength multiplier with three or even more work modes.

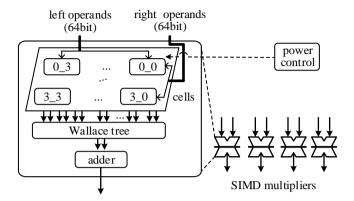

#### 4.1. PRIOR WORK AND STATE-OF-ART

Typically, modern long wordlength and high-performance multipliers consist of Booth encoders [42], Wallace tree [43], and a final adder. Booth encoders generate partial products which can be regarded as several vectors of different lengths. Figure 4.1 illustrates the partial products of a  $16\times16$  signed/unsigned multiplier [44]. Several signed extension bits (marked as 1, E, and S) are introduced to present negative participial products among Booth encoding in signed multiplications. An original Wallace tree compresses all partial product vectors until two vectors as the two operands of the final adder. Building blocks of Wallace tree are usually  $3\to2$ ,  $4\to2$ , and  $5\to2$  compressors, which compress multiple input bits and carry bits from the lower-weight compressor to two bits and carry bits for higher-weight compressor [45]. Wallace tree is formed up by these compressors to compress multiple partial product vectors into two vectors.

One general method of designing a dynamic wordlength multiplier is supporting short wordlength multiplication based on a long wordlength multiplier, masking unused partial product for shorter multiplication [46] [47]. In this top-down way, one w-bit multiplier can be split to support two  $\frac{w}{2}$ -bit multiplications, further be split to four  $\frac{w}{4}$ -bit multiplications, and so on. However, this method only exploits part of the available partial product and bears few number of multiplications in short wordlength mode. On the other hand, results of longer multiplications can be generated with four half-length multiplications in a bottom-up way. Assuming two 2w-bit operands, a and b, they can be split into two w-bit parts, Most Significant Bits (MSBs) and Least Significant Bits (LSBs), which can be expressed as

$$a = a_1 2^w + a_2 (4.1)$$

$$b = b_1 2^w + b_2, (4.2)$$

where  $a_1$  and  $b_1$  are MSBs,  $a_2$  and  $b_2$  are LSBs. Therefore, four w-bit multiplications can compose one 2w-bit multiplication. The 4w-bit result of 2w-bit multiplications can be presented as,

$$ab = a_1b_12^{2w} + a_1b_22^w + a_2b_12^w + a_2b_2, (4.3)$$

where  $a_1b_1$ ,  $a_2b_2$ ,  $a_2b_1$ , and  $a_2b_2$  have a length of 2w bits. However, this method is tortured by the extra latency introduced when the number of work modes is larger than two. Each additional work mode requires an extra summing process shown in (4.3), which sums up at most three values in one binary digit.  $6 \rightarrow 2$  compressors can be used to achieve this summing up process in Wallace tree, however, the delay is relevantly large and laying on the critical path of the multiplier.

| $\cap$                                                                                                                               | Line |

|--------------------------------------------------------------------------------------------------------------------------------------|------|

| _1\bullet x x x x x x x x x x x x x x x x x x x                                                                                      | 0    |

| 1E × × × × × × × × × × × × × × × × × ×                                                                                               | 1    |

| 1E x x x x x x x x x x x x x x x x x S                                                                                               | 2    |

| $1 E \times $ | 3    |

| <u>1 E x x x x x x x x x x x x x x X X X X X</u>                                                                                     | 4    |

| 1 EXXXXXXXXXXXXXXX S                                                                                                                 | 5    |

| 1 E X X X X X X X X X X X X X X X X X X                                                                                              | 6    |

| EXXXXXXXXXXXXXX S                                                                                                                    | 7    |

| XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                               | 8    |

| Last line of CPP S                                                                                                                   |      |

**Figure 4.1.** The Booth encoding results of a 16-bit multiplier.

#### 4.2. STICKY BOOTH ENCODING

In this chapter, a sticky Booth encoding is used to generate the partial products of a dynamic wordlength multiplier directly. Instead of using the bottom-up or top-down methods, sticky Booth encoding allows the use of shorter wordlength Booth encoder to generate partial products for a long wordlength multiplication. In this way, a multiplier equipped with the sticky Booth encoding can supply the partial products of multiple multiplications in short wordlength mode while maintaining low latency for long wordlength multiplications.

Traditional partial products are generated according to Booth encoding and can be divided into two parts: Core Partial Products (CPP) and Sign Extension Bit (SE). Shown in Figure 4.1, SE are 1, E, and S and the last line of partial products (line 8 for 16-bit multiplications). CPP are the rests marked as crosses in Figure 4.1. In sticky Booth encoding, CPP and SE are generated separately to hide the delay.

#### CORE PARTIAL PRODUCT CODING

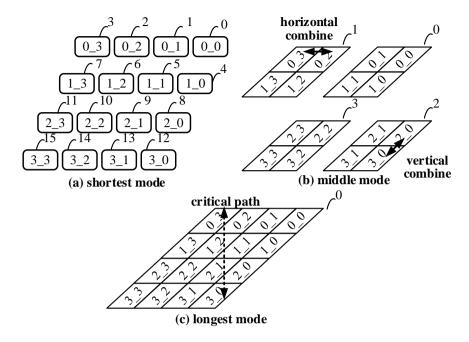

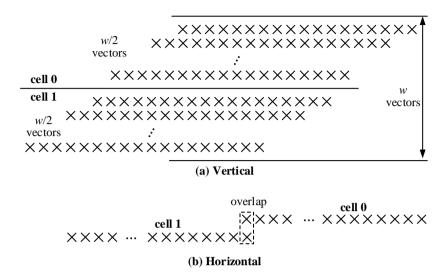

The smallest unit of CPP coding is defined as a cell which is basically the CPP of the shortest wordlength. Cells work independently in short wordlength mode and work jointly in long wordlength mode. Figure 4.2 illustrates combination patterns of a three modes multiplier. The combinations can be further categorized into vertical and horizontal combinations, where vertical combination merges two  $w \times w$  cells into CPP for a  $w \times 2w$  multiplication. It is necessary to note that directly combining CPP will lead to errors in signed multiplication.

Directly combining vertically neighboring cells does not impact the functionality. The number of CPP vectors for  $w \times 2w$  and  $w \times w$  multiplications are w and  $\frac{w}{2}$ , respectively. Shown in the upper half of Figure 4.3, vertically neighboring cells can be directly combined. On the other hand, two horizon-

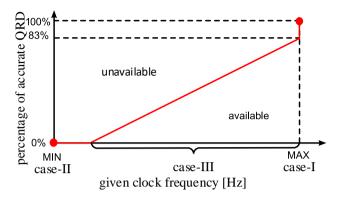

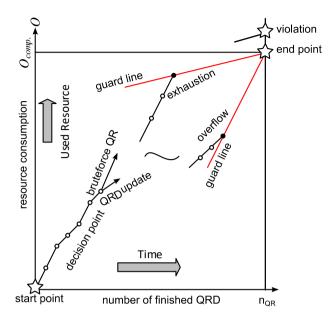

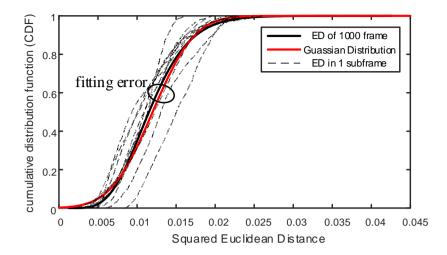

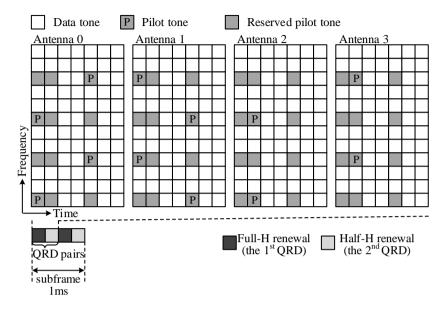

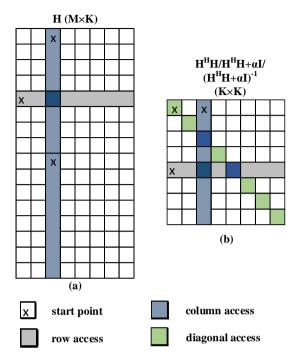

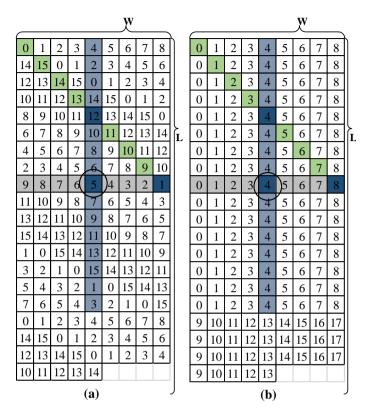

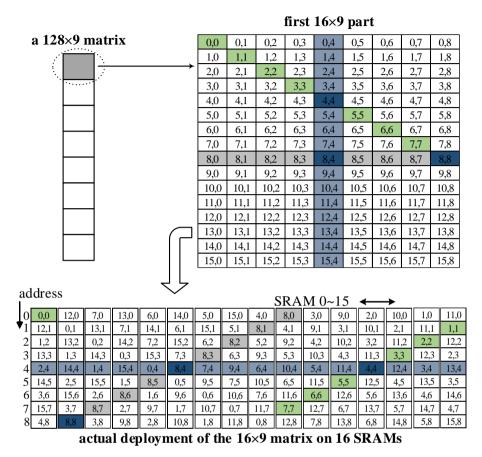

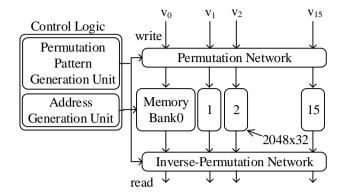

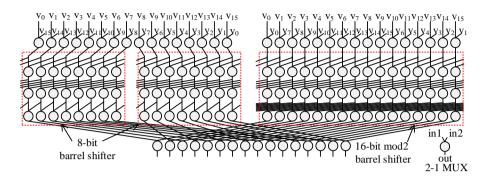

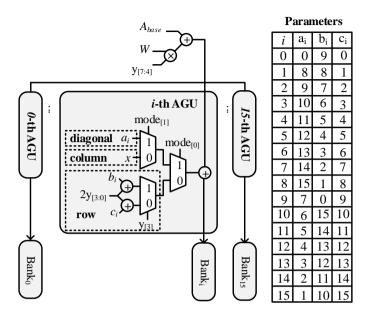

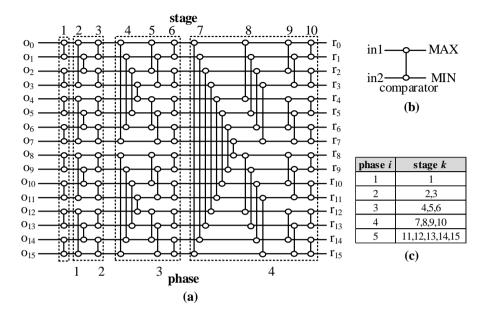

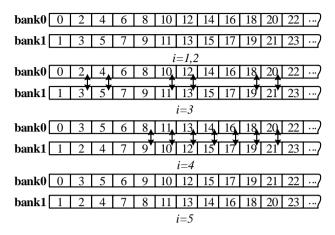

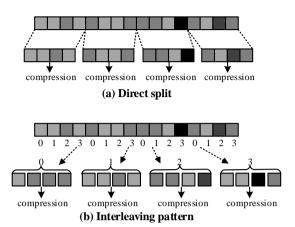

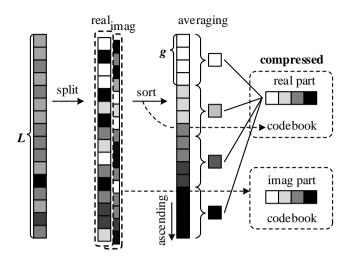

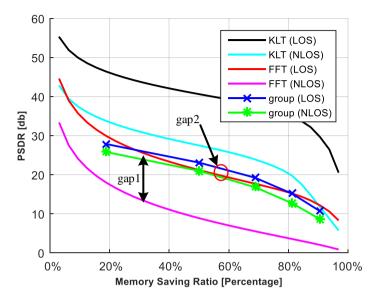

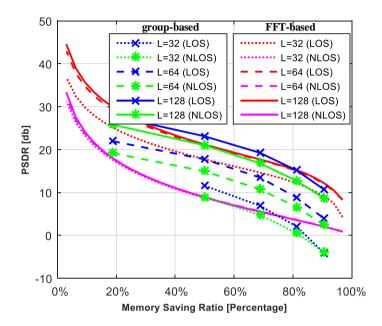

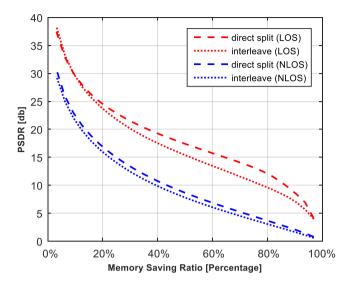

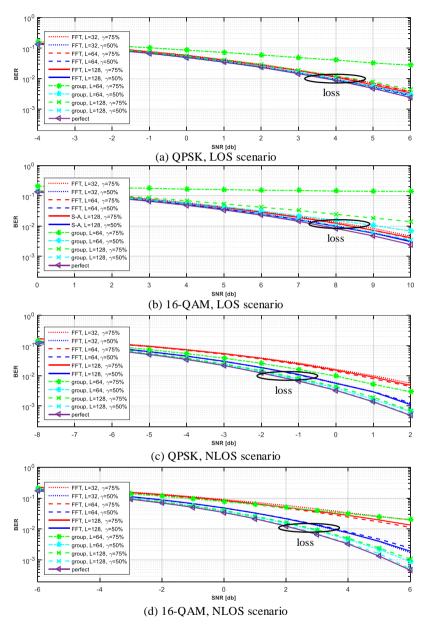

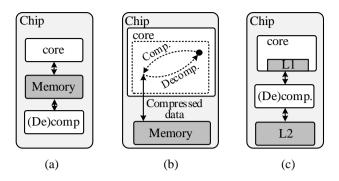

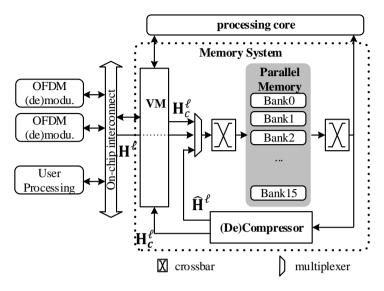

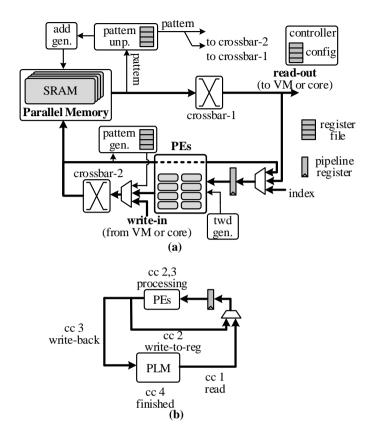

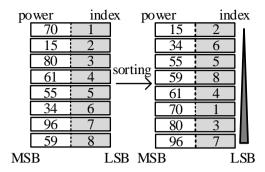

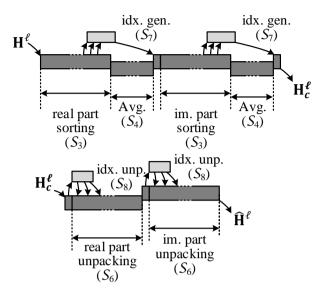

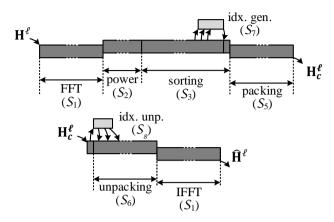

Figure 4.2. An illustration of cell combinations in three modes.