### LUND UNIVERSITY

### Algorithm-Architecture Co-Design for Digital Front-Ends in Mobile Receivers

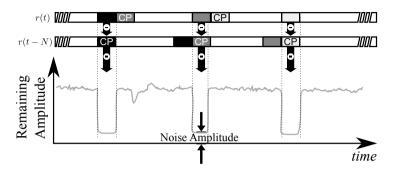

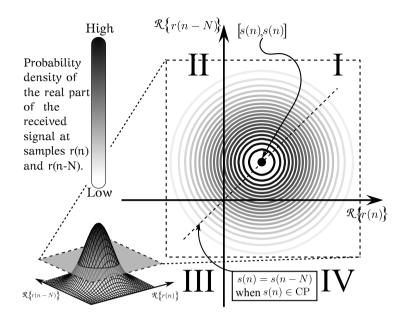

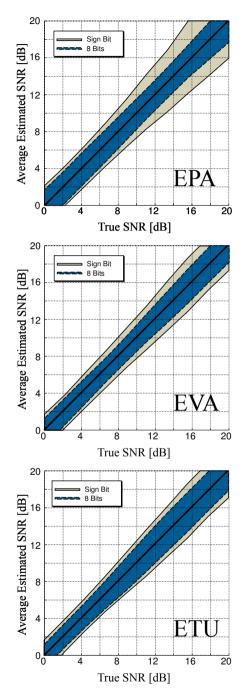

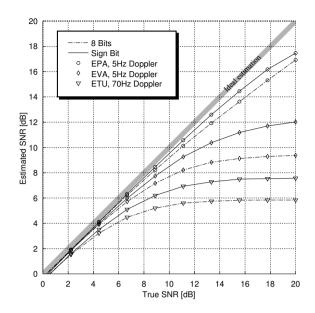

Diaz, Isael

2014

### Link to publication

Citation for published version (APA): Diaz, I. (2014). Algorithm-Architecture Co-Design for Digital Front-Ends in Mobile Receivers. [Doctoral Thesis (monograph), Department of Electrical and Information Technology].

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

### Algorithm-Architecture Co-Design for Digital Front-Ends in Mobile Receivers

Isael Diaz

### LUND UNIVERSITY

Doctoral Dissertation Circuit Design Lund, April 2014

Isael Diaz Department of Electrical and Information Technology Circuit Design Lund University P.O. Box 118, 221 00 Lund, Sweden

Series of licentiate and doctoral dissertations ISSN 1654-790X; No. 56 ISBN 978-91-7473-788-2

c 2014 Isael Diaz Typeset in GFS-Artemisia and Helvetica using  $\text{LAT}_{\text{E}}\text{X2}_{\mathcal{E}}$ . Printed in Sweden by Tryckeriet i E-huset, Lund University, Lund.

No part of this dissertation may be reproduced or transmitted in any form or by any means, electronically or mechanical, including photocopy, recording, or any information storage and retrieval system, without written permission from the author.

### Abstract

The methodology behind this work has been to use the concept of algorithmhardware co-design to achieve efficient solutions related to the digital frontend in mobile receivers. It has been shown that, by looking at algorithms and hardware architectures together, more efficient solutions can be found; i.e., efficient with respect to some design measure. In this thesis the main focus have been placed on two such parameters; first reduced complexity algorithms to lower energy consumptions at limited performance degradation, secondly to handle the increasing number of wireless standards that preferably should run on the same hardware platform. To be able to perform this task it is crucial to understand both sides of the table, i.e., both algorithms and concepts for wireless communication as well as the implications arising on the hardware architecture.

It is easier to handle the high complexity by separating those disciplines in a way of layered abstraction. However, this representation is imperfect, since many interconnected "details" belonging to different layers are lost in the attempt of handling the complexity. This results in poor implementations and the design of mobile terminals is no exception. Wireless communication standards are often designed based on mathematical algorithms with theoretical boundaries, with few considerations to actual implementation constraints such as, energy consumption, silicon area, etc. This thesis does not try to remove the layer abstraction model, given its undeniable advantages, but rather uses those cross-layer "details" that went missing during the abstraction. This is done in three manners:

In the first part, the cross-layer optimization is carried out from the algorithm perspective. Important circuit design parameters, such as quantization are taken into consideration when designing the algorithm for Orthogonal Frequency Division Multiplexing (OFDM) symbol timing, Carrier Frequency Offset (CFO), and Signal-to-Noise Ratio (SNR) estimation with a single bit, namely, the Sign-Bit. Proof-of-concept circuits were fabricated and showed high potential for low-end receivers. In the second part, the crosslayer optimization is accomplished from the opposite side, i.e., the hardwarearchitectural side. A Software Defined Radio (SDR) architecture is known for its flexibility and scalability over many applications. In this work a filtering application is mapped into software instructions in the SDR architecture in order to make filtering-specific modules redundant, and thus, save silicon area. In the third and last part, the optimization is done from an intermediate point within the algorithm-architecture spectrum. Here, a heterogeneous architecture with a combination of highly efficient and highly flexible modules is used to accomplish initial synchronization in at least two concurrent OFDM standards. A demonstrator was build capable of performing synchronization in any two standards, including LTE, WiFi, and DVB-H. Any intelligent fool can make things bigger, more complex, and more violent. It takes a touch of genius - and a lot of courage to move in the opposite direction.

- Ernst Friedrich "Fritz" Schumacher (1911 – 1977)

### Contents

| Contents        |     |        |                                       |      |  |  |  |

|-----------------|-----|--------|---------------------------------------|------|--|--|--|

| Preface         |     |        |                                       |      |  |  |  |

| Acknowledgments |     |        |                                       |      |  |  |  |

| 1               | In  | trodu  | ction                                 | 1    |  |  |  |

|                 | 1.1 | The ne | eed for abstraction                   | . 2  |  |  |  |

|                 | 1.2 | Mathe  | matical modeling vs. the real world   | . 3  |  |  |  |

|                 | 1.3 | Hardw  | vare implementation                   | . 4  |  |  |  |

|                 | 1.4 | Algori | thm-architecture co-design            | . 6  |  |  |  |

| 2               | W   | reles  | s communication basics                | 9    |  |  |  |

|                 | 2.1 | Functi | onal model of wireless communication  | . 10 |  |  |  |

|                 |     | 2.1.1  | Information source/sink               | . 10 |  |  |  |

|                 |     | 2.1.2  | Source coder/decoder                  | . 11 |  |  |  |

|                 |     | 2.1.3  | Channel coder/decoder                 | . 11 |  |  |  |

|                 |     | 2.1.4  | Modulator/demodulator                 | . 11 |  |  |  |

|                 |     | 2.1.5  | Equalizer                             | . 11 |  |  |  |

|                 |     | 2.1.6  | Tx/Rx front-ends                      | . 12 |  |  |  |

|                 |     | 2.1.7  | Propagation channel                   | . 12 |  |  |  |

|                 |     | 2.1.8  | Antenna techniques                    | . 13 |  |  |  |

|                 | 2.2 | Orthog | gonal frequency division multiplexing | . 14 |  |  |  |

|                 |     | 2.2.1  | OFDM transceiver                      | . 15 |  |  |  |

|                 |     | 2.2.2  | Cyclic prefix                         | . 16 |  |  |  |

|   |                                | 2.2.3   | Synchronization                            | . 18 |  |

|---|--------------------------------|---------|--------------------------------------------|------|--|

|   |                                | 2.2.4   | Spectrum in duplex arrangement             | . 19 |  |

|   | 2.3 The wireless channel       |         |                                            | . 20 |  |

|   |                                | 2.3.1   | Statistical description of the channel     | . 21 |  |

| 3 | Co                             | ommo    | n wireless technologies                    | 25   |  |

|   | 3.1                            | Applic  | ation-based classification                 | . 25 |  |

|   |                                | 3.1.1   | Wireless wide area network                 | . 25 |  |

|   |                                | 3.1.2   | Wireless local area network                | . 27 |  |

|   |                                | 3.1.3   | Wireless personal area network             | . 27 |  |

|   |                                | 3.1.4   | Satellite communication                    | . 28 |  |

|   |                                | 3.1.5   | Data rate vs. mobility                     | . 28 |  |

|   | 3.2                            | 3GPP    | long term evolution                        | . 29 |  |

|   |                                | 3.2.1   | Physical layer parameters.                 |      |  |

|   |                                | 3.2.2   | Synchronization and cell search            |      |  |

|   |                                | 3.2.3   | Carrier aggregation                        |      |  |

|   |                                | 3.2.4   | Terminal classification                    |      |  |

|   |                                | 3.2.5   | Channel models                             |      |  |

|   | 3.3                            | IEEE    | 802.11 wireless LAN                        |      |  |

|   |                                | 3.3.1   | Frame structure                            | . 38 |  |

|   | 3.4                            | U       | l video broadcast                          |      |  |

|   |                                | 3.4.1   | Physical layer structure                   | . 41 |  |

|   | 3.5                            | OFDM    | I standard specific parameters             | . 43 |  |

| ī | e:                             | an hit  | estimation                                 | 47   |  |

| • | 31                             | gii-bii | estimation                                 | 4/   |  |

| 4 | Α                              | • •     | of low-complexity estimation               | 49   |  |

|   | 4.1                            | Appli   | cability in OFDM Systems                   | . 50 |  |

| 5 | Si                             | gn-bit  | symbol timing and carrier frequency offset | 53   |  |

|   | 5.1                            | Full pi | recision estimation                        | . 54 |  |

|   | 5.2                            | Sign-b  | it derivation                              | . 55 |  |

|   | 5.3                            | Estima  | ation performance                          | . 57 |  |

| 6 | Sign-Bit signal to noise ratio |         |                                            |      |  |

|   | 6.1                            | Full pi | recision estimation                        | . 65 |  |

|   | 6.2                            | Sign-b  | it estimation                              | . 66 |  |

|   | 6.3                            | Estima  | ation performance                          | . 70 |  |

| 7 Complexity analysis and proof of concept         | 75    |

|----------------------------------------------------|-------|

| 7.1 Equivalent architecture                        | . 76  |

| 7.1.1 Time-frequency mode                          | . 76  |

| 7.1.2 SNR mode                                     | . 76  |

| 7.2 Sign-bit architecture                          | . 77  |

| 7.2.1 Time-frequency Mode                          | . 77  |

| 7.2.2 SNR mode                                     | . 78  |

| 7.3 Complexity trade-offs                          | . 79  |

| 8 Summary of Part I                                | 83    |

| II Custom DSP processing for LTE-A                 | 85    |

| 9 Common filtering methods and target architecture | 87    |

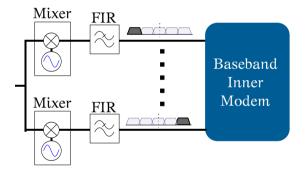

| 9.1 Common digital filtering methods               | . 88  |

| 9.1.1 FIR filtering                                | . 88  |

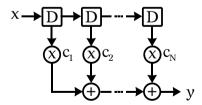

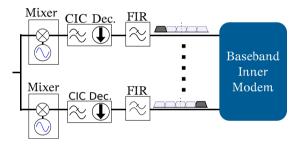

| 9.1.2 CIC filtering                                | . 90  |

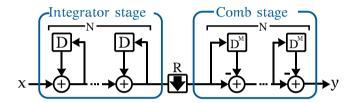

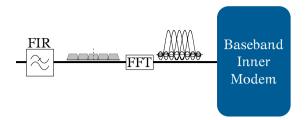

| 9.1.3 FFT-based filtering                          | . 91  |

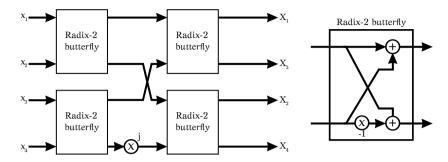

| 9.2 ADRES architecture                             |       |

| 9.2.1 ADRES template                               | . 92  |

| 10 Selective filtering in software-defined radio   | 97    |

| 10.1 Cost analysis and simulation results          |       |

| 10.1.1 Channelization methods                      |       |

| 10.1.2 CIC filter + FIR                            |       |

| 10.1.3 FFT filtering                               |       |

| 10.2 Complexity analysis                           |       |

| 10.3 Performance analysis                          |       |

| 11 Summary of Part II                              | 103   |

| III Multi-standard support                         | 105   |

| 12 EU multibase project                            | 107   |

| 12.1 Description                                   | . 108 |

| 12.2 Organization                                  | . 110 |

| 12.3 Achievements                                  | . 112 |

| 13 Functional platform                             | 115   |

| 13.1 Specifi | c requirements per standard  | 15 |

|--------------|------------------------------|----|

| 13.1.1       | Sample rate                  | 15 |

| 13.1.2       | Synchronization              | 16 |

| 13.2 Archit  | ecture functionality         | 16 |

| 13.2.1       | Automatic gain control       | 17 |

| 13.2.2       | Compensation                 | 18 |

| 13.2.3       | Decimation chain             | 18 |

| 13.2.4       | Synchronization engine       | 18 |

| 13.2.5       | Buffer and bus interface     | 20 |

| 14 DFE-Rx    | proof of concept 12          | 1  |

| 14.1 Synthe  | esis of the architecture     | 21 |

| 14.1.1       | Area breakdown               | 21 |

| 14.2 Verific | cation                       | 24 |

| 14.3 Result  | s                            | 24 |

| 15 Summa     | ry of Part III 13            | 1  |

| 16 Thesis s  | summary 13                   | 3  |

| 16.1 Sign-b  | it estimation                | 33 |

| 16.2 Custor  | n DSP Processing for LTE-A13 | 34 |

| 16.3 Multi-  | standard support             | 35 |

|              |                              |    |

| Appendix                | 137 |

|-------------------------|-----|

| Popular science summary | 139 |

| Acronyms                | 141 |

| Glossary of symbols     | 145 |

| Bibliography            | 147 |

### Preface

This dissertation summarizes the work carried out during the period between August 2008 and April 2014, at the department of Electrical and Information Technology of Lund University. Most of the relevant results from these fruitful years have been published in scientific journals, international conferences, or publicly available research reports, which are listed as follows:

- DIAZ, I., WILHELMSSON, L., SOFOTASIOS, P., MIAO, Y., TAN, S., EDFORS, O., AND ÖWALL, V. "A new approach to Sign-Bit based parameter estimation in OFDM receivers," *submitted to Springer Circuits, Systems, and Signal Processing*, March 2014.

- The author parted from the original idea of Mr. Wilhelmsson, simulated various realistic scenarios, with the help of some co-authors developed a hardware architecture as proof of concept, while others contributed with important mathematical insights.

- DIAZ, I., ZHANG, C., HOLLEVOET, L., SVENSSON, J., RODRIGUES, J., WILHELMS-SON, L., OLSSSON, T., VAN DER PERRE, L., AND ÖWALL, V. "A New Digital Front-End For Flexible Reception In Software Defined Radio", *Elsevier*, *Microprocessors and Microsystems: Embedded Hardware Design, invited* to special issue on NORCHIP, March 2014.

- The author was invited to submit an extended version of the work presented at NORCHIP in 2013. The additional material included supplementary implementation results and theoretical analysis.

- DIAZ, I., ZHANG, C., HOLLEVOET, L., SVENSSON, J., RODRIGUES, J., WILHELMS-SON, L., OLSSSON, T., VAN DER PERRE, L., AND ÖWALL, V. "Next generation digital front-end for multi-standard concurrent reception", *NORCHIP Conference*, November, 2013.

IF The author was the main integrator of the various parts conforming

the front-end presented in this article, the author was also the main responsible of the algorithm development of one crucial module in the design, i.e., the synchronization engine. Finally, the author was the main participant in the verification of the entire front-end.

- DIAZ, I., TORREA-DURAN, R., POLLIN, S., VAN DER PERRE, L., AND ÖWALL, V., "Selective Channelization on an SDR Platform for LTE-A Carrier Aggregation," *IEEE International Conference on Electronics, Circuits, and Systems*, October, 2012.

- The author carried out the study that resulted in the publication of this article with technical assistance and guidance from the co-authors.

- WILHELMSSON, L., DIAZ, I., OLSSON, T., AND ÖWALL, V., "Analysis of a novel low complex SNR estimation technique for OFDM systems," *IEEE Wireless Communications and Networking Conference*, March, 2011.

- The author performed performance simulations and hardware implication analysis.

- WILHELMSSON, L., DIAZ, I., OLSSON, T., AND ÖWALL, V., "Performance analysis of sign-based pre-FFT synchronization in OFDM systems," *IEEE 71st Vehicular Technology Conference*, May, 2010.

- The author provided with important aspects regarding practical implementation of the presented algorithms.

- DIAZ, I., WILHELMSSON, L., RODRIGUES, J., LÖFGREN, J., OLSSON, T., AND ÖWALL, V., "A sign-bit auto-correlation architecture for fractional frequency offset estimation in OFDM," *IEEE International Symposium on Circuits and Systems*, May, 2010.

- The author created a hardware implementation, synthesized and did place-and-route, to more accurately estimate hardware complexity.

- DIAZ, I., WILHELMSSON, L., RODRIGUES, J., OLSSON, T., AND ÖWALL, V., "Sign-Bit based architecture for OFDM acquisition for multiple-standards," *NORCHIP*, November, 2009.

- The author performed Matlab simulations, created a hardware implementation that complied with its algorithm specification and analyzed the hardware costs and benefits.

There is also a list of publications where the author has contributed, yet are not formally part of this dissertation, this list include the following:

• OLSSON, T., CARLSSON, A., WILHELMSSON, L., EKER, J., VON PLATEN, C., AND DIAZ, I., "A reconfigurable OFDM inner receiver implemented in the CAL dataflow language," *IEEE International Symposium on Circuits and Systems*, May, 2010.

- DIAZ, I., SATHYANARAYANAN, B., MALEK, A., FOROUGHI, F., AND RODRIGUES, J. "Highly Scalable Implementation of a Robust MMSE Channel Estimator for OFDM Multi-Standard Environment", *IEEE Workshop on Signal Processing Systems*, October, 2011.

- ZHANG, C., DIAZ, I., ANDERSSON, P., RODRIGUES, J., AND ÖWALL, V., "Reconfigurable cell array for concurrent support of multiple radio standards by flexible mapping," *IEEE International Symposium on Circuits and Systems*, May, 2011.

- ZHANG, C., DIAZ, I., ANDERSSON, P., RODRIGUES, J., AND ÖWALL, V. "Reconfigurable cell array as enabler for supporting concurrent multiple standards in mobile terminals," *10th Swedish System-on-Chip Conference*, May, 2010.

In this thesis is demonstrated that by jointly studying systems, algorithms and hardware architectures, it is possible to develop solutions that mitigate the often contradicting demands of performance, flexibility and energy efficiency. Even though applied to the area of the digital front-end in mobile receivers in wireless communication, the author is confident the approach is valid far outside this field.

This document is divided into several introductory chapters and three parts. The first chapters introduce basic concepts of wireless communication and hardware design needed to understand the scientific contributions. The three parts contain the main contribution areas where the author focused on creating something new and useful for the scientific community.

Part I on page 49 deals with a novel methodology to reduce hardware complexity in low complexity receivers. Part II on page 87 explores the capabilities of highly optimized generic architectures to performed filtering in Long Term Evolution - Advanced (LTE-A), a task so computationally intensive that it is usually done with very specialized hardware. Finally, Part III on page 107 combines algorithm development with a hardware construction techniques in order to deal with the challenges imposed by multi-standard concurrent reception.

The research work included in this dissertation was sponsored by Seventh Framework Programme for Research (FP7) European Union (EU) project Multibase and VINNOVA Industrial Excellence Center - System Design on Silicon.

### Acknowledgments

The number of pages in this thesis is insufficient to name all those who helped me in along this road, nonetheless I will mention a few with hope that my clumsy self does not bedim the important contribution of those not mentioned here.

First, I would like to express my gratitude to my supervisor Professor Viktor Öwall, who always provided his guidance and support as a good leader and true friend, it has been an honor to work for you "jefe", and thanks for singing my paychecks too. My gratitude also goes to my other two great mentors, Professor Ove Edfors and Dr. Leif Wilhelmsson, I learned profoundly much from both of you, I only regret I finish my degree before being able to squeeze-out the last bit of knowledge you both have. I would also like to thank Professor Liesbet Van der Perre and people at IMEC for allowing me to do research in their team as just one more member, especially Lieven Hollevoet, who to this day helps me to stay out of trouble with Belgian authorities.

Thanks to everyone at the EIT department, especially for those in the digital ASIC group, you are all like a family to me and I am happy to have developed ever lasting friendships with each and every one of you, the interesting discussions and joyful moments had nourished me deeply and I am infinitely grateful for that. My appreciation also goes to the secretaries and technical staff who made my life as PhD student smooth and satisfying; it is more pleasant to carry out your work when someone handles the paper-work and technical details.

I would also like to express my appreciation to my Mexican and Norwegian families. My Mexican family always cultivated in me the best values of honesty, hard-work, and perseverance. They were always so assure of some greatness in me to a point where they manage to convince me. And my Norwegian family that accepted me with wide open arms and adopted me as

one of their own, and helped us in ways I couldn't imagine.

Last and most importantly, I want to thank my beautiful wife Maria. We took this project together and this achievement is every bit yours, even more so since you made it possible. To Elias and Helena, "mis hermosos", even though you were not the reason why I started this, you are the reason why I went on finishing it and the reason I go on doing anything else in my life. Without you I would have finished in half the time.

> Isael Diaz Palacios Lund, March 2014.

## 1

### Introduction

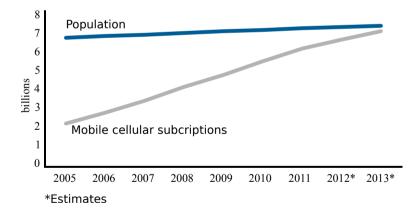

Wireless communications is one of the fastest growing market segments. According to estimations by the International Telecommunication Union (ITU), see Figure 1.1, there is today the same number of mobile subscribers as the number of people living on this planet [1]. Furthermore, it is expected to accelerate with the incorporation of the Internet of Things (IoT), where many more devices will be connected wirelessly to the Internet.

Figure 1.1.: Number of Mobile subscribers in the world [1].

The IoT intends to connect to the Internet each and every device that benefits by any way from being connected. Some estimations predict that we will have 50 billion devices connected to the Internet by the year 2020 [2]. Among the application areas that are expected to benefit from this highly connected infrastructure are, wireless sensor networks, automated highways, machineto-machine communication, automated factories, smart homes, appliances, remote tele-medicine, etc. There are already some insights on how all these devices will shape our future connectivity. For example, sensor networks will play a major role in connecting trillion of sensors to the Internet. These sensors will be located everywhere and will provide information about every-thing around us. This unleashed layer of connectivity is commonly called sensory swarm [3]. Even though true wireless ubiquity and sensory swarm are evidently part of our future, there are still major technological challenges that need to be overcome.

Today, these challenges are addressed by two efforts combined. The first consists in making better use of the radio resources by designing better Radio Access Technologies (RATs), and the second consists in designing efficient implementations of radio transceivers in order to take the most advantage of the radio resources with minimum energy consumption.

This thesis deals with the second effort, i.e., efficient design of radio transceivers, and does that by taking a cross-disciplinary approach; i.e., by combining algorithm design and circuit construction techniques to benefit the most from both disciplines.

In order to place into context the contributions presented in this thesis, a number of introductory chapters are included. These chapters deal with important concepts in wireless communication and wireless communication standards. They are not intended to give a detailed description on these significant complicated subjects, but rather, give some reference information on terms and concepts used later in the thesis.

### **1.1. THE NEED FOR ABSTRACTION**

In order to cope with the complexity of designing advanced wireless communication infrastructures, the entire infrastructure is divided into abstraction layers so that each layer is independent and serves as a division between knowledge of specific fields. One of the most common examples of this abstraction is the Open Systems Interconnection (OSI) layer used in network design as a framework for dividing protocols into various layers. This abstraction provides a divide-and-conquer approach to the already complex task of designing a fully operational data network [4]. A brief description of the layers is presented as follows:

**7. APPLICATION:** This layer is in charge of the interaction with the user. It presents information in a format understood by the user and receives commands to be translated into internal protocols to be passed to lower layers.

**6. PRESENTATION:** Provides services to the application layer. This is done using a specific semantic the user can interpret independently from the data. Typical tasks within this layer are: data encapsulation, encryption, encoding, *etc*.

**5. SESSION:** Is in charge of the connection between terminals or computers in the network, determines whether the connection between the communicating parts is two-way or one-way. In the first, both parties transmit at the same time whereas in the latter only one active transmission is allowed. This layer is in charge of opening and closing connection sessions as required.

4. **TRANSPORT:** This layer is in charge of sending packages from one address to another in the network. It typically adds error control methods to the communication and maintains control over failed and successfully sent packages.

**3. NETWORK:** This layer defines protocols needed to transfer packages from a point to any other point within the network. Here many packages are clustered within datagrams. Each datagram is given a specific path or route to find its destination within the network.

**2. DATA LINK:** This layer is in charge of providing a reliable connection between two directly connected nodes. It is also in charge of detecting and correcting errors occurred in the physical layer. It defines protocols to be used in the delivery of information in dependence to the network topology. e.g., point-point, point-to-multi-point, ring connection, *etc.*

1. PHYSICAL: Typically called PHY for short, is in charge of defining the protocol between two directly connected points in the network and the specification of all electrical and physical properties of the connection. The protocol varies in accordance to the transmission medium, e.g., copper, fiber cable, wireless connection, *etc.* This thesis mainly deals with the Physical Layer (PHY) layer, and the trade-offs present with its implementation. While some of the innovations presented impact directly the PHY layer, it might carry out repercussions to higher layers within the OSI model as well.

### 1.2. MATHEMATICAL MODELING VS. THE REAL WORLD

Further abstraction is found in the way the protocols within each layer are implemented. Specially in the PHY layer where the actual transmission of information takes place via the interaction of physical forces (in radio applications the force in use is electromagnetic). These interactions are modeled as mathematical processes with many ideal (non-realistic) assumptions. On the one hand, in wireless communications it might be theoretically possible to accurately model all natural processes involved in the wireless transmission. However, this is often not desired, as the actual implementation of such systems is too complex to be done in practice, thus, approximate models are used instead of precise ones.

On the other hand, in circuit design, there are also mathematical models that describe the interaction between the different components that constitute all parts in a circuit, e.g., capacitors, transistors, cables, resistors *etc*. However, as circuits grow larger in size and hence in number of elements, abstractions models are used to handle the large complexity. A common division in circuit design is the partition between analog and digital circuitry. The way each partition works and the way each is designed is completely different.

Due to the large complexity enclosed within each of these abstraction models, there is a well-defined language for each of the disciplines, and it becomes increasingly more difficult for a single individual to be able to master them all. Even though abstractions bring clear benefit in hiding complexity it might also hinder quality, given that possible cross-layer optimizations are set aside or simply ignored. In this thesis the cross-layer optimization is the central object of analysis, more specifically in the realm of mobile terminals.

#### **1.3. HARDWARE IMPLEMENTATION**

In the early days of electronic design, circuits were designed for a unique purpose. However, as technology improved, more and more transistors were fit in the same area, to be more precise, in 1965 Gordon Moore predicted that the number of transistors that could be placed in a single die increased exponentially with time [5]. This statement became known as "Moore's law", which was a term coined by Carver Mead, and has driven the electronic industry for the last 50 years.

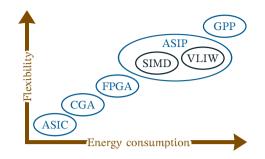

As the number of transistors in a single chip increased, the semiconductor industry has found ways to connect them in various types of configurations. Each configuration (hardware architecture) represents a different paradigm in terms of energy consumption and flexibility, ranging from the very energy efficient (ASIC) to the very flexible (GPP). Figure 1.2 on the facing page illustrates a general map on how common hardware configurations are compared in the flexibility-energy spectrum. Application-specific instruction-set processors (ASIPs) are architectural heterogeneous devices, hence, they contain various types of sub-architectures, e.g., Very Long Instruction Word (VLIW), Single Instruction Multiple Data (SIMD), and others. Each of the architectures depicted in the figure is briefly described in the following paragraphs.

Figure 1.2.: Flexibility vs. energy consumption of popular processor architectures.

**ASIC:** Application-Specific Integrated Circuits (ASICs) are the customized Integrated Circuits (ICs) for a particular application; they are considered the most energy-efficient alternative for the task they are designed to accomplish. They can be found as stand-alone ICs or as hardware accelerators in System On Chip (SoC) environment. The main drawbacks of ASICs are their lack of flexibility, high fabrication cost, and long development time.

**CGA:** Coarse-Grain Architectures (CGAs) borrow some characteristics from Field-Programmable Gate Arrays (FPGAs) like, the ability to be programmed and short development time. However, CGAs lack gate-level programmability, which increases their energy efficiency by sacrificing flexibility. A CGA consists of multiple Functional Units (FUs) interconnected via a Network on Chip (NoC), where a FU is a single processing element capable of performing basic arithmetic operations, depending on the intended application more complex operations are sometimes included in the FUs.

**FPGA:** Field-Programmable Gate Arrays (FPGAs) are digital ICs specifically designed to be configured by the end-user. They consist of a large matrix of bit-level programmable logic blocks, interconnected via flexible interconnections that can also be programmed. Configurable Logic Blocks (CLBs) can be configured to match the desired functionality, that functionality can be reprogrammed while they are placed in their field of action. Among some of the advantages of FPGAs over ASICs are: higher flexibility, scalability, lower price, and shorter development time.

**SIMD:** SIMDs borrows the concept of simple FU from CGA, but they differ drastically on the way they are programmed and how they are interconnected. As their name implies, all FUs, or processing units, load and execute the same instruction, and the interconnection between FUs is limited. They are

considered vector computers and are extremely beneficial in applications with high degree of data parallelism, like image processing.

**VLIW:** Very Long Instruction Word (VLIW) architectures are conceptually considered Multiple Instruction Multiple Data (MIMD) computers. They consists of 2 or more parallel processors, and their name is derived from the fact that a single instruction word is long enough to control all processors in the architecture, The burden of task scheduling is shifted to the compiler, which leads to less control logic in the data-path, which can be beneficial in some applications. VLIW architectures offer significant benefits in applications with high level of Instruction Level Parallelism (ILP).

**GPP:** General Purpose Processors (GPPs) are behind every personal computer, their introduction goes back to the early days of computing. As its name implies, it is designed for a large variety of applications giving GPP very high flexibility but also high energy consumption, i.e., GPPs contain large memories and several type of interfaces, complex arithmetic modules, such as floating point, *etc.*,

### 1.4. ALGORITHM-ARCHITECTURE CO-DESIGN

The best implementation for any application requires a fine tuning between both algorithm and architecture. Given that design constraints vary considerably among different applications, e.g., silicon area, speed, transmission rate, power, *etc.*, a general abstraction model results in sub-optimal implementations. Thus, efficient implementations can only be realized if both algorithm and architecture are prepared towards a common goal. As an example, consider the fastest wireless transfer record, which is 100 Gbps over 20 m [6]. This achievement was possible thanks to the right combination of theoretical modeling and a precise implementation. Theoretically, the maximum transmission rate depends on the transmission bandwidth, channel conditions, *etc.* However, the theory is only half of the story, even under the most precise mathematical model of the channel, if the hardware realization is imperfect, those perfect conditions cannot be met.

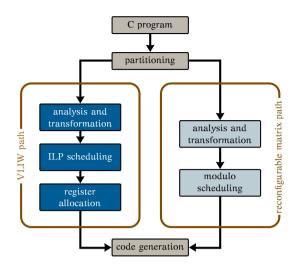

In this thesis, the algorithm-architecture optimization is carried out by the following methodologies:

**TAKING THE SIDE OF ALGORITHM DESIGN:** Here an application specific algorithm is taken, e.g., signal detection, channel estimation, symbol decoding, modulation, *etc.* The algorithm is designed with basis of transmission performance. Once the algorithm is defined, imperfections originated in the circuit realization are included. Then, proper adjustment to the algorithm follows in order to account for those imperfections. If the appropriate adjustments were performed, the modified algorithm presents a more adequate alternative than the original. Often the goal is not performance, but energy consumption, die size or other. In that case the adjustments have to be done according with that specific goal in mind so that the final result is better than the original in terms of a specific design parameter; performance is traded for energy consumption.

**TAKING THE ARCHITECTURE SIDE:** In modern mobile terminals it is challenging to arrive at an optimal implementation. This is due to the fact that most modern terminals are multi-purpose. Under these circumstances it is attractive to look into the hardware side for optimization opportunities. Modern architecture configurations such as VLIW, Coarse Grain Reconfigurable Architecture (CGRA), SIMD, provide a high degree of flexibility as they exploit parallelism inherent in the algorithm or application. Then by selecting an appropriate combination of these configurations, it is possible to increase: usability, cost-effectiveness, platform life-cycle, *etc.* Therefore, in this methodology a group of applications or a single multi-scenario application is chosen, then a combination of architectures is selected that optimizes a specific design criteria, e.g., area, speed, transmission rate, power, cost-effectiveness, platform life-cycle, *etc.* As a result, the final architecture represents a better alternative in terms of that optimization constraint, than multiple highly specialized circuits designed for all possible cases.

# 2

### Wireless communication basics

The work done in this thesis applies to one type of wireless communication, namely wide-band digital communication with Orthogonal Frequency Division Multiplexing (OFDM) technology. More specifically, it applies to initial signal acquisition and filtering in the receiver terminal, which are parts of what is often referred as Digital Front-End (DFE). However, the underlying concepts behind algorithm-architecture co-design can find application in many other disciplines. In in this chapter a general introduction of wireless communication is given, in order to place the relevance of this thesis in a larger context.

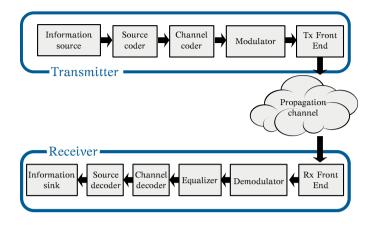

The basic principle of wireless communication consists of transmitting information from an information source, referred as Transmitter (Tx), to an information destination, referred Receiver (Rx), via a wireless propagation channel. The Tx can modify the information to make it better suited for reception. Then it can make better use of the transmission medium by using modulation and can also protect it from unwanted listeners by encryption. It can make it more resistant to errors by adding coding. Finally, the Tx can format it so that multiple Rxs can extract only portions of it. Conversely, the Rx needs to perform the inverse transformations in order to interpret the received data; it also needs to correct for any error introduced by the propagation channel.

In wireless communications one of the main challenges remains in the propagation channel, and there are three fundamental aspects that make communication difficult. The first is the fact that the propagation channel properties vary with time, known as fading. The second is the fact that there is no physical connection between both transmitting ends, resulting in significant interference and synchronization issues during the communication [7]. The third is the unavoidable imperfections in practical implementations resulting in additional noise.

Figure 2.1.: Block diagram of a typical transmission link.

### 2.1. FUNCTIONAL MODEL OF WIRELESS COMMUNICATION

The communication link can be abstracted in a functional model which involves generation of information, its preparation for transmission, the actual transmission over the channel, reception, correction of received information, and its final interpretation at the receiver end. These abstractions are illustrated in Figure 2.1, where a functional block diagram of a typical communication link is illustrated in several blocks.

There are more modules in a real transmission system that are not illustrated in this diagram. Among these modules are, those for packaging, pilot insertion, *etc*.

In the diagram, each block represents a data transformation. Various data transformations are necessary to increase the chances of the information being successfully interpreted by the Rx. Some transformations are directly related to the properties of the information to be transmitted and other related to the characterization of the transmission medium, or propagation channel, as it will be clear in the remainder of this section.

### 2.1.1. INFORMATION SOURCE/SINK

The information source and sink represent the origin and destination of the intended data. In principle the information to be transmitted can be anything, and typical examples include, voice, music, image, video, or any other form of digital media.

### 2.1.2. SOURCE CODER/DECODER

The source coder typically uses known properties of the signal in order to remove redundancy and thus, reduce it to a minimal representation. among such coders there are speech coders, image/video coders, audio coders, *etc.*

### 2.1.3. CHANNEL CODER/DECODER

The channel coder introduces a structure redundancy that can be used on the receiver side to minimize errors. Many types of codes are available and it is still an active research field. Some examples are, block codes, convolutional codes, turbo codes, and intricate types such as Low-Density Parity-Check Code (LDPC).

### 2.1.4. MODULATOR/DEMODULATOR

The modulation consists of mapping information bits to signal waveforms that carry the desired information in a format better suited for transmission. Conversely, the demodulation does the opposite operation. However, since the transmission medium influences the received waveform, an additional equalization step is required at the receiver.

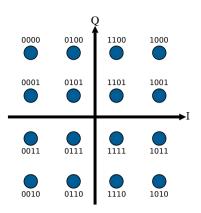

Each waveform can carry from a single to any number of bits, with the main limitation that as the number of bits increases, the probability of losing some information is increased. The main motivation in choosing a specific modulation is to transmit as much information as possible over a channel with a specific bandwidth, while at the same time satisfying a given probability of error, better known as Bit Error Rate (BER).

A list of common digital modulations techniques include among others: Pulse Amplitude Modulation (PAM), Phase Shift Keying (PSK), Frequency Shift Keying (FSK), and Quadrature Amplitude Modulation (QAM). Special attention is given to QAM, since it has been widely adopted in cellular and Local Area Networks (LAN) systems, as this type of modulation is capable of enclosing a large number of bits per Hz. In QAM the information is placed as amplitude values on two orthogonal signals (in-phase and quadrature), typical realizations include 4QAM, 16QAM, 64QAM, and 256QAM. Figure 2.2 on the following page depicts a constellation diagram for 16QAM with Gray coding<sup>1</sup>.

### 2.1.5. EQUALIZER

When waveforms carrying the desired information are exposed to the transmission medium, e.g., a wireless medium, they are unavoidably affected by it, making difficult the correct interpretation of the received information. An equalizer can be used to remove the effects introduced by the channel; this

<sup>&</sup>lt;sup>1</sup>Gray coding is a binary representation designed so that neighboring constellation point differ only by one bit.

Figure 2.2.: Constellation diagram of rectangular 16QAM with Gray coding.

is done by relying on various equalization techniques. In some cases, as typically done in OFDM, the equalization stage is divided in detection (estimation) and correction (equalization).

In general, equalizers can be characterized by type, structure and algorithms [8]. There are countless equalization methods, and it is to this day, a very active field of research.

### 2.1.6. TX/RX FRONT-ENDS

The Tx front-end has the function of taking a baseband signal and placing it at a carrier frequency. Then, it follows that the Rx does exactly the opposite operation. Modern front-ends are typically divided in an Analog Front-End (AFE) and a DFE, where the limits of what operations belong to what domain (analog or digital) are not well defined, and it's closely related to specific transceiver architecture. In this thesis, a special focus is given to the DFE, especially when operating in connection to Software Defined Radio (SDR) architectures.

#### 2.1.7. PROPAGATION CHANNEL

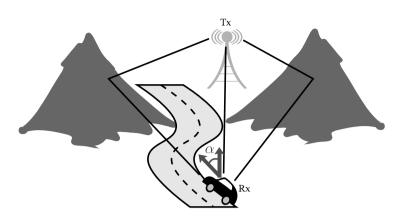

The propagation channel in combination with the receiver's noise level limits the ultimate transmission efficiency. Wireless communication channels are characterized by multi-path propagation. As the signal travels from Tx it is reflected, diffracted and scattered by structures encountered on its path towards the Rx forming what is denominated as multi-path components. These components are added at the receiver end, and need a special treatment.

An illustration of the multiple path transmission concept is shown in Figure 2.3 on the next page. In the figure, there a signal bouncing off two

Figure 2.3.: Muti-path components present in wireless communication.

mountains, and hence creating two multi-path components together with a direct line of sight component. Another typical characteristic of wireless channels is the presence of Doppler effect, due to the aforementioned multi-path components, and the mobility of either Tx or Rx. The relative motion produces frequency shifts on the transmitted signal. This is illustrated in Figure 2.3. Doppler effect can be an important source of imperfections in the transmission link. More about the propagation channel and Doppler effects in Section 2.3 on page 20.

#### 2.1.8. ANTENNA TECHNIQUES

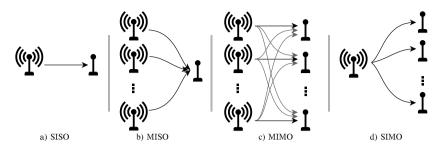

Multiple-antenna techniques can be used to increase transmission data-rate or to improve reliability. More specifically, it is possible to utilize multiple antennas for: a) beam-forming, b) increase diversity, c) suppress interference, and d) spatial multiplexing. The improvement takes place without any increase of transmission bandwidth. However, these techniques have a significant cost in terms of hardware and computational requirements in both Tx and Rx. Possibly the simplest technique, from the implementation perspective, is the use of the additional antennas to provide antenna diversity. Since different versions of the same signal are received by several antennas, the receiver can choose which antenna to listen to based on its associated channel quality.

Multiple antennas systems can be classified in four categories: Single Input Single Output (SISO), Multiple Input Single Output (MISO), Multiple Input Multiple Output (MIMO), and Single Input Multiple Output (SIMO), depicted in Figure 2.4 on the following page.

Figure 2.4.: Four different types of antenna configurations, a) SISO, b) MISO, c) MIMO, and d) SIMO

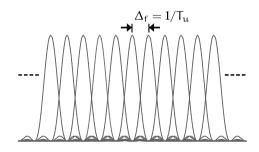

Figure 2.5.: Frequency domain bandwidth occupied by an OFDM system with a sub-carrier spacing  $\Delta_f$ , specifically designed to maintain orthogonality.

### 2.2. ORTHOGONAL FREQUENCY DIVISION MULTIPLEXING

OFDM is a modulation technique that consists of placing information on multiple carrier frequencies (sub-carriers, or tones). This is particularly beneficial for high data rate transmission in delay dispersive environments. OFDM converts a high data rate transmission into several parallel lower data rate transmissions. The lower data rate transmissions are orthogonal and can be easily equalized.

The sub-carriers are placed at the minimum allowed frequency separation needed to maintain orthogonality. The spectral efficiency of such implementation is rather high compared to other communication technologies. This can be shown in Figure 2.5, where the sub-carrier spacing  $\Delta_f$  equals the inverse of the symbol timing  $T_u$ ; necessary to ensure the orthogonality.

Various modern RATs have adopted OFDM technology as the modulation technique at the core of the standard specification. The popularity of OFDM can be traced to one or more of the following benefits:

• high spectrum efficiency, resulting from dense sub-carrier packing,

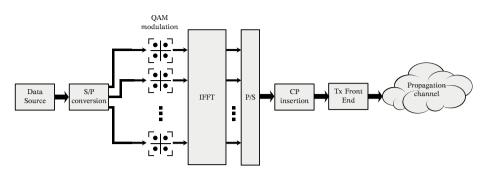

Figure 2.6.: Block diagram of an OFDM transmitter.

- it can operate on highly frequency selective channels (delay dispersive environment), and

- the simplification of equalization techniques in the receiver terminal which is typically provided with limited resources.

In the remainder of this chapter some basic concepts regarding OFDM technology are discussed. However, it is important to note that only the aspects affecting the work in this thesis are addressed, and others are intentionally left out. If reader feels the need of acquiring deeper knowledge regarding the subject, they are encouraged to read [9] [10], [11], [12], and [13].

#### 2.2.1. OFDM TRANSCEIVER

As previously discussed, the key idea behind OFDM is to divide the spectrum into several narrow-band channels, in order to make each narrow-band channel immune to frequency selectivity, i.e., each sub-carrier experiences a quasi-flat fading channel. This is typically done with the aid of Inverse Fast Fourier Transform (IFFT) and Fast Fourier Transform (FFT) modules sitting in the transmitter and the receiver, respectively. A block diagram illustrating the most important parts of an OFDM transmitter is depicted in Figure 2.6, where Serial to Parallel (S/P) and Parallel to Serial (P/S) are purely conceptual as they don't affect the actual information in any manner.

The QAM modulation phase in the figure, corresponds to the modulation introduced in Subsection 2.1.4 on page 11. In OFDM the modulation used is typically restricted to QAM and PSK [11]. A Guard Interval (GI) filled with a Cyclic Prefix (CP) is used in order to avoid Inter-Symbol-Interference (ISI) and Inter-Carrier-Interference (ICI). However, as it will be seen in Subsection 2.2.2 on the following page, it leads to a loss of transmission efficiency.

As one can expect, the receiver applies the inverse operations of all the depicted modules in reverse order, i.e., Front-End (FE)  $\rightarrow$  CP removal  $\rightarrow$  S/P

$\rightarrow$  FFT  $\rightarrow$  QAM demodulation  $\rightarrow$  P/S  $\rightarrow$  data sink. It is important to note that the OFDM transceiver chain is easily placed in a communication link system perspective, this can be visually conceived by replacing the Modulator/Demodulator block from Figure 2.1 on page 10, with the OFDM transceiver chain without duplicating the FEs.

The utilization of FFT modules is an efficient way for placing the modulated symbols onto each sub-carrier. There are two possibilities to map the sub-carriers onto the number of available FFT points: First, if the number of sub-carriers is not a power of two, one can leave zero sub-carriers at the boundaries of the FFT and place information only on the middle FFT points. This is done in several RAT specifications, e.g., Long Term Evolution (LTE), IEEE 802.11 (WiFi), among others, since it leads to simpler reconstruction/transmission filters. Second, is to use a mixed-radix FFT with equal number of points as the number of sub-carriers available. This solution is less efficient from the perspective of hardware implementation, but it might be beneficial in some well defined scenarios [14] and [15].

### 2.2.2. CYCLIC PREFIX

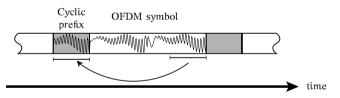

The Guard Interval (GI) extends the duration of the OFDM symbol to allow the channel's impulse response to settle during the duration its duration in order to avoid ISI. This is also graphically depicted in Figure 2.7, where it can be seen that the last part of the symbol is copied to the start of the GI, just before the OFDM symbol. This is done in the time domain and it is referred as CP insertion.

Figure 2.7.: Typical OFDM symbol with its corresponding CP.

ISI is the undesired interaction between consecutive OFDM symbols due to the influence of the propagation channel to the transmitted signal. The propagation channel can be modeled as a Linear Time Invariant (LTI) system<sup>2</sup> with a limited memory, and therefore, a convolution with the channel produces the transient period at the beginning and end to each OFDM symbol. The duration of this period is given by the length of the channel's impulse

<sup>&</sup>lt;sup>2</sup>In reality, the wireless propagation channel is time invariant only for some special cases. However, the channel can be considered quasi-stationary for a short period of time, given by the relative motion between Tx and Rx, read more about channel modeling and its properties in Section 2.3 on page 20.

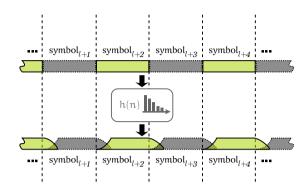

Figure 2.8.: OFDM symbols that lack Guard Interval. The dark intersection area corresponds to that ISI introduced by the propagation channel h.

response. This is illustrated in Figure 2.8, where it can be seen the ISI as the intersection between the transient of the previous symbol with the transient of the current one.

Then, by removing the part of the CP at the receiver, given that the CP is larger than the channel's impulse response, ISI can be completely mitigated. However, a careful choice for the duration of such CP has to be made, since an increase of the duration of CP results in loss of spectral efficiency. The CP has another important contribution, since it allows the equalization to become a simple multiplication per sub-carrier in the frequency domain.

### FREQUENCY ERRORS IN OFDM

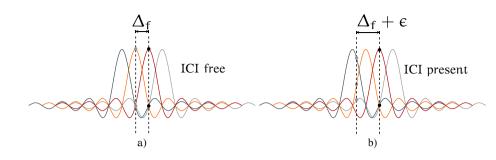

There are two types of frequency misalignments in OFDM, both resulting in undesired ICI. First, a frequency offset between local oscillators causing a slight shift in the carrier frequency, more commonly referred as Carrier Frequency Offset (CFO). Second, a frequency offset between master clocks, at both Tx and Rx which results in frequency misalignment between sub-carriers, this misalignment is commonly known as Sampling Frequency Offset (SFO).

ICI is the loss of orthogonality between sub-carriers. In order for OFDM to function properly, the transmitter and receiver sub-carriers must be perfectly aligned, and the FFT modulation has to be applied to exactly a complete symbol period. The presence of CFO breaks the sub-carrier alignment from transmitter and receiver, even though the sub-carrier spacing is the same at both ends. Furthermore, a SFO contributes by an apparent scaling of the spectrum as seen by the receiver.

ISI is illustrated in Figure 2.9 on the next page, where it is seen that the OFDM system with ICI contains a frequency separation of  $\Delta_f$ . In the sub-figure to the right the desired sub-carrier spacing plus an error  $\epsilon$  due

Figure 2.9.: OFDM frequency bandwidth a) without ICI, and b) with ICI due to frequency misalignments.

to misalignment. As a consequence, the point is not sampled at the zero crossing, opposite to what is seen in the sub-figure to the left, where there is no ICI, i.e., the sub-carrier spacing is exactly  $\Delta_f$ , at the sampling point. ISI due to frequency misalignments drastically affect the perceived Signal to Interference Ratio (SIR) and need to be eliminated. In this thesis, the CFO estimation and removal is addressed and studied in some detail.

### 2.2.3. SYNCHRONIZATION

Synchronization is a crucial process in any digital communication scheme. The need for synchronization arises from the fact that Tx and Rx do not possess a common time nor frequency reference.

When a mobile terminal is initiated, it needs to search for a signal that announces the presence of a base station in the proximity. This process is typically called *acquisition* [16], and it is one of the important procedures in the establishment of a successful communication link. Typically during *acquisition*, the mobile terminal performs synchronization, i.e., symbol-timing detection, initial CFO estimation, CFO correction, and initial channel estimation. In this thesis the synchronization process is given special attention, more particularly the part of acquisition. The methods and architectures presented later in this document are designed to estimate, among other parameters, symbol timing, and CFO, during acquisition stage.

Synchronization in OFDM can tolerate relatively large errors in the symboltiming estimation in comparison to a single-carrier system [11]. However, in contrast to single-carrier systems, it is more sensitive to frequency misalignments; due to the overlapping of narrow-band spectrum in OFDM.

Two types of synchronization methods can be found in literature, namely, data-aided and non data-aided (blind). The first type uses information embedded in the signal for this particular use, whereas the second relies on the CP and typically suffer from lower performance, since the CP is affected by ISI.

There are many methods in literature for aided and non-aided synchronization. Some examples of aided synchronization include Maximum Likelihood (ML) estimation [17], and some customizations of this given in [18–20]. Among the non-aided methods, one of the most commonly cited is the one using the CP [21]. In this thesis, the author explores both types, but gives special attention to non-aided, as in some cases can also be used to estimate other parameters, such as Signal-to-Noise Ratio (SNR).

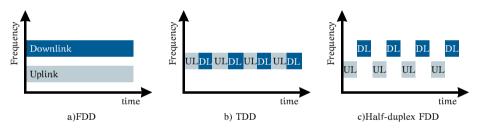

### 2.2.4. SPECTRUM IN DUPLEX ARRANGEMENT

A duplexing arrangement is not confined to OFDM systems, neither to wireless communication, and it has wide application among all types of communication. Full duplexing allows communication to happen in two directions simultaneously, i.e., from Tx to Rx, and vice versa. In wireless communication the most logical partition when duplexing is in time and/or frequency. Thus, two obvious multiplexing configurations are Frequency Division Duplexing (FDD) and Time-Division Duplexing (TDD), and some hybrid in between, like half duplex FDD. These are depicted in Figure 2.10, and briefly described as follows.

Figure 2.10.: Frequency and time division multiplexing.

**FREQUENCY DIVISION DUPLEXING**, is the duplexing scheme where the entire transmission bandwidth is divided into two completely separate transmission bandwidths, one for Uplink (UL), and one for Downlink (DL). The advantage of such a configuration is that communication between both ends can happen simultaneously. However, it requires a paired spectrum and it imposes complexity in the receiver, as it needs completely independent and well isolated Tx/Rx chains with no straight-forward hardware reuse.

**TIME DIVISION DUPLEXING**, is the scheme where the transmission of UL or DL is done in turns. Contrary to what happens in FDD, this scheme does not require paired spectrum and thus, it is easier to allocate in a fragmented spectrum. As a consequence, this is scheme is the preferred choice for many operators.

HALF DUPLEX FDD, is a duplexing scheme where there is an exclusive part of the spectrum of each transmission and reception, and these two operations do not take place at the same time, this is typically used to reduce complexity at the terminal,i.e., many hardware blocks can be reused, and it is supported by several RATs, e.g., Global System for Mobile communication (GSM) and LTE.

#### 2.3. THE WIRELESS CHANNEL

Many things can be said about wireless channels, they can be classified by many criteria e.g., based on representation, modeling-technique, communication topology, statistical parameters, *etc.* The author has no intentions into discussing details about wireless communications channels, but rather, just to put into context the application field of the work presented. For that reason some important concepts are briefly described in this section.

Figure 2.11.: A two-dimensional sine wave propagating in a three multi-path components environments, the three reflected signals super imposed and form a complicated wave in space.

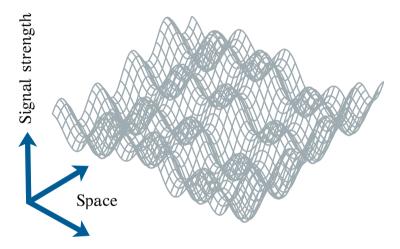

The wireless channel is one of the most important elements in the wireless communication scheme. The channel in combination with noise set the ultimate limit of the communication performance. Contrary to a wired channel, in wireless channels there are multiple propagation paths that can contribute constructively and destructively to the received signal, i.e., the transmitted signal is reflected, diffracted, or scattered along each multi-path on its way to the receiver. This is illustrated in Figure 2.11 where the superposition of three reflected paths are depicted, note that the resulting superposition does differ from a uniform two-dimensional sine wave propagation, as the phases of the reflected copies and its amplitudes disturb each other.

There are, however, other scenarios where there is no multi-path components to disturb the transmitted signal. Those scenarios are governed by *free space attenuation*, where the received signal strength is a function of the communication distance.

There are channel modeling techniques that take into consideration many elements in the propagation path of the signal, e.g., reflection, scattering and diffraction and resolve many multi-path components. However, these methods are often very complex as they need specific knowledge of the electric properties of materials involved in the transmission. Furthermore, considering that in a real scenario many objects move, e.g., cars, people, even the hand that holds the receiver terminal. Therefore, it is often chosen to describe the channel as an stochastic process with certainties and probabilities.

#### 2.3.1. STATISTICAL DESCRIPTION OF THE CHANNEL

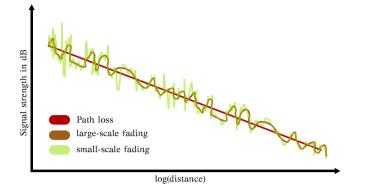

Due to the large complexity required to resolve all individual multi-path components, it is often desired to describe a channel statistically. This implies that the channel is fully characterized not by individual channel realizations but by its full statistics. As a consequence the received power variation are classified in two categories, path-loss and fading. Briefly described as follows.

#### PATH-LOSS

The Path-loss is an unavoidable loss of signal strength due to the distance the transmitted wave has to travel to reach the receiver. It also depends on the transmission frequency, and is closely related to *free space attenuation*, mentioned on this page, and be seen in Figure 2.12 on the next page as a straight line with negative slope.

#### FADING

Fading describes the variations of the signal as seen from the receiver. Fading varies in relation to time, transmission frequency, and geographical position. Strong interference is typically known as a *deep fade* and it impacts negatively the communication link by a severe drop of the received SNR.

Fading is typically modeled as a stochastic process that varies in amplitude and phase of the transmitted signal. It is commonly characterized by largescale and small-scale fading, visually depicted in Figure 2.12 on the following page.

• large-scale or macroscopic fading, is the result of the environment changing due to motion. Its behavior is typically attributed to shadowing of large objects, e.g., buildings, mountains, *etc.* Experimental

Figure 2.12.: Fading and its three parts, path-loss, large-scale, and small-scale fading.

results show that fading can be modeled by a log-normal distribution; i.e., the amplitude in dB follows a Gaussian distribution.

• small-scale or microscopic fading, refers to signal strength variation over very short distance (approximately around one wavelength), and these fluctuation are mainly attributed to multi-path components. Smallscale fading is mathematically modeled as a Rayleigh distribution if there is no dominant component present, commonly known as Line of Sigth (LOS), or as a Rician distribution in case of an existing LOS component.

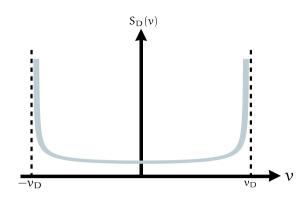

#### DOPPLER SPECTRA

When either Tx, Rx, or something in the environment are moving during transmission, the various directions of the multi-path component produce different frequency shifts on the received signal. As a consequence, the spectrum perceived by the receiver is shifted. The typical visualization of this phenomenon is the transmission of a single sine wave over a narrow channel, where there is infinite number independent and identically distributed (i.i.d.) isotropic multi-path components. Under this assumption, the resulting Doppler spectrum has a bathtub shape, and it is delimited by the maximum Doppler shift ( $v_D$ ), illustrated in Figure 2.13 on the next page.

Note that the Power Spectral Density (PSD) is infinite at the maximum Doppler shift. However, remember that this is an illustration of an ideal assumption never true in practice. The maximum Doppler shift is an important parameter since it describes the *frequency dispersion*. It can also serve as an indicator of *temporal variation*, indicating to what extent a channel can be considered time-invariant.

Figure 2.13.: Illustration of ideal Doppler spectrum with infinite number of multi-path components arriving from all possible directions to the receiver.

#### CHANNEL ASSESSMENT

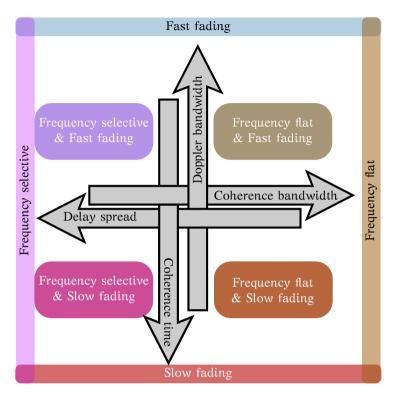

A channel can be generalized based on two pairs of parameters, namely, *delay spread-coherence bandwidth* and *coherence time-Doppler bandwidth*. They provide a very general idea on how a channel behaves during most transmissions, thus they can be used as tools to intuitively assess a particular channel. Note that, this is a very generalized simplification and only serves as an intuitive way to asses wireless channels.

- *Delay spread*, describes the approximate duration of the impulse response of the channel, and it is connected to the *frequency selectivity*. Frequency selectivity mainly depends on the environment and the transmission bandwidth, since narrow-band systems suffer more from selectivity than wide-band systems [9].

- *Coherence bandwidth*, is often used as an indication on how stable the channel is in the frequency domain, the larger the coherence bandwidth the flatter the channel. It maintains an inversely proportional relation to the *delay spread*.

- Doppler bandwidth, is the bandwidth given by the Doppler spectra, already described on the facing page. It is connected to the environment and the motion, larger speeds result in larger Doppler bandwidth. It is inversely proportional to the channel's *coherence time*.

- *Coherence time* is a parameter that tells for how long the channel can be considered static, i.e., time-invariant. A large delay spread results in a small coherence bandwidth, and consequently the channel is perceived as "frequency selective", or "frequency flat" if the opposite applies.

Figure 2.14.: Channel assessment in relation to, coherence time, Doppler bandwidth, coherence bandwidth, and delay spread.

It can be said that if a channel has a large Doppler bandwidth, it also contains a short coherence time, and as a consequence can be categorized as "fast-fading". If the opposite is true, the channel is of "slow-fading" nature. These relations are illustrated in Figure 2.14.

# 3

### Common wireless technologies

Wireless communication is so essential in today's typical life that it can be found virtually anywhere, in stationary and mobile applications, e.g., twoway radios, mobile phones, computers, personal assistants, garage openers, computer accessories, headphones, television, cordless phones, *etc.* The list just keeps growing. In order to enhance device compatibility, interoperability, safety and quality, standardization bodies have defined a set of wireless standards. These standards specify the implementation rules of devices and systems for a particular purpose.

The work performed in this thesis applies to OFDM standards only. More specifically to IEEE 802.11 (WiFi), Long Term Evolution (LTE), and Digital Video Broadcasting - Handheld (DVB-H). This chapter tries to place them into context and highlight their noticeable differences. There are many details intentionally left out as they are not considered relevant to the work presented in later chapters.

#### 3.1. APPLICATION-BASED CLASSIFICATION

Since the number of applications is large and some requirements often contradict with others, a set of standard families is created with similar goals in mind. When it comes to wireless communication four large commercial categories can be identified, namely, Wireless Wide Area Networks (WWANs), Wireless Local Area Networks (WLANs), Wireless Personal Area Networks (WPANs), and satellite communication, briefly described.

#### 3.1.1. WIRELESS WIDE AREA NETWORK

The standards belonging to WWAN category are designed to give service to large physical areas. Broadcasting services like radio or television together

Figure 3.1.: Layout of a cellular system network with frequency reuse factor of 1/4.

with cellular systems are some examples. Whereas radio and television provide service in a single direction, cellular systems can provide two-way communication with regional, national, and international coverage. Note that this is possible by the combination of wireless and wired communication combined.

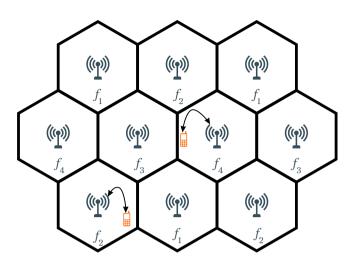

Cellular networks are named as such given their capacity to layout networks based on coverage cells. The concept was invented by Douglas H. Ring at Bell Labs in 1947, to be later patented in the 1972 [22]. Cellular networks takes advantage of the fact that signal power is attenuated by distance, it is possible to reuse frequencies in separate locations. Figure 3.1 illustrates a cellular network layout.

Cellular systems are usually refereed as interference limited systems. When a phone communicates, it does so via a Base Station (BS) servicing the cell where the phone is located. The energy from other cells with the same frequency configuration are perceived as interference, more formally named inter-cell interference. Modern cellular standards may have a heterogeneous deployment, with micro-cells and nano-cells with shorter coverage embedded within a BS with larger coverage; typically called macro-cell. In heterogeneous deployments the inter-cell interference becomes more relevant. Typical examples of cellular systems include all standard defined by 3rd Generation Partnership Project (3GPP), i.e., Global System for Mobile communication (GSM), Wide-band Code Division Multiple Access (WCDMA), High Speed Packet Access (HSPA), Long Term Evolution (LTE), and its newest release Long Term Evolution - Advanced (LTE-A). There are a few other standards that had evolved from WLAN into offering WWAN services, like Worldwide Interoperability for Microwave Access (WiMAX) and city-wide WiFi.

#### 3.1.2. WIRELESS LOCAL AREA NETWORK

The goal of WLAN is to act as the wireless counterpart of the more traditional wired LAN topology. The area to be covered is typically a campus, a building, an office, or a house. Users connecting to a WLAN are expected to be semi-stationary, typically sitting at a desk, or moving at pedestrian speeds.

An important factor for the success and rapid adoption of WLAN standards in almost all modern commodities is the fact that these type of standards use the unlicensed spectrum, which saves costs and avoids licenses. However, for exactly the same reasons, there is a good deal of other technologies using the same spectrum causing a great amount of interference.

Institute of Electrical and Electronics Engineers (IEEE) regulates the standardization 802.11, also known as WiFi. There are substantial differences between each member of the family. e.g., the first release of 802.11 was based on Direct-Sequence Spread Spectrum (DSSS), Frequency-Hopping Spread Spectrum (FHSS), and infrared access technologies, whereas newer versions use OFDM.

The evolution of the WiFi standards has brought higher data-rates, better coverage, and an increased level of security. As an example, the latest release of the family is IEEE 802.11af<sup>1</sup> which provides means to access the white space spectrum (this modern technique is known as cognitive radio), and supports data rates up to 568.9 Mbps [23]. Even higher data-rates are expected with future releases.

#### 3.1.3. WIRELESS PERSONAL AREA NETWORK

The purpose of WPAN devices is to connect devices focusing on a single individual and her surroundings. The application scope is localized within a limited space and due to the typical short-range coverage and low data-rate requirements, these technologies can operate on a tight energy budget.

Besides the low-energy consumption, another typical advantage is the low price, due to the operation of such devices on unlicensed spectrum bands. Some examples of these standardized technologies include, Infrared Data Association (IrDA), Bluetooth, Zig-Bee, some versions of WiFi, Near-Field Communication (NFC), and many others.

There also exists a number of non-standardized technologies operating on the same unlicensed bands that can be categorized as WPAN technology, e.g., cordless phones, radio control modules, *etc.* These are typically developed in-house for a very specific purpose and do not follow any particular standardization body, and thus, not compatible with other vendors.

<sup>&</sup>lt;sup>1</sup>Scheduled to be released in March 2014

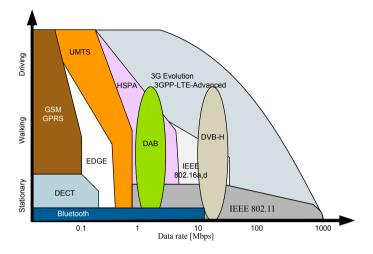

Figure 3.2.: Data Rate transmission vs. Mobility for wireless standards extended from IMEC Scientific Report 2007 [24].

#### 3.1.4. SATELLITE COMMUNICATION

Satellite communication describes the type of communication taken place between an artificial satellite orbiting the earth and one or many devices on the surface of the earth. The intended applications for satellite networks are either broadcast services, such as television, radio, Global Positioning System (GPS), *etc.*, or point-to-point communication. Broadcast services are the ideal application since a satellite can cover a large area and the transmission cost can be shared between large numbers of users. Point-to-point communication, on the other hand is expensive and it is typically confined to inaccessible areas where no other type of communication is possible.

#### 3.1.5. DATA RATE VS. MOBILITY

RATs can also be classified in relation to their data-rate and mobility. Figure 3.2 depicts some of the most popular standards classified in this manner. On the bottom-left corner are the standards that provide the lower data-rate under stationary conditions, which usually results in low energy implementations. Different standards cover different areas in the plot that also place different requirements on the terminals supporting them.

Note from the figure that according to this classification the standards that occupy a larger portion of the plot are more flexible, as they can both provide various data-rates and multiple mobility capabilities. There is, of course, an implicit cost in energy consumption not depicted here, e.g., WiFi operating on low data rate consumes more energy that standard Bluetooth .

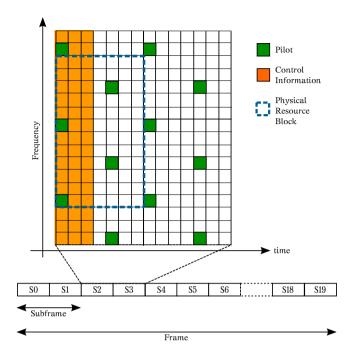

Figure 3.3.: LTE-FDD, DL time-frequency grid with one RB highlighted

#### 3.2. 3GPP LONG TERM EVOLUTION

This section provides a brief introduction to the physical layer procedures and characteristics of LTE during Downlink (DL), more detailed information about this particular RAT can be found in references [12] [25] [26].

#### 3.2.1. PHYSICAL LAYER PARAMETERS.

The Physical Layer (PHY) is one of the abstraction layers defined by LTE's radio protocol architecture, PHY is in charge of coding/decoding, multi-antenna mapping, channel estimation, synchronization and other functions. The PHY provides services to the Medium Access Control (MAC) layer via transport channels.

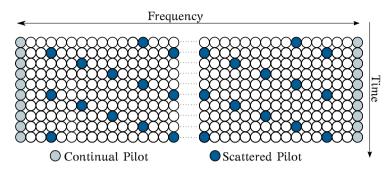

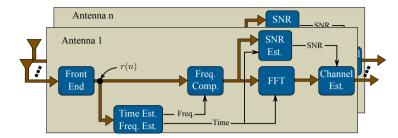

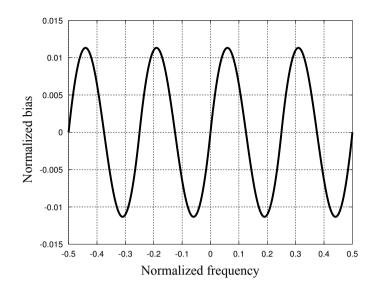

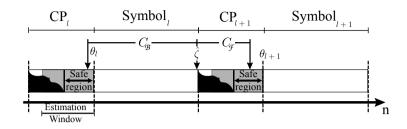

In LTE a physical channel is modeled as a two-dimensional grid where the dimensions correspond to time and frequency, graphically represented in Figure 3.3. Each small square represents a single sub-carrier at a specific OFDM symbol and it is referred as Physical Resource Element (PRE). A Physical Resource Block (PRB) is the minimum amount of time-frequency resources that can be assigned to any particular user and consists of 12 subcarriers within 7 symbols, this accounts for a total of 84 PREs. In the time-frequency grid there are reference symbols (pilots), used for channel estimation purposes, the figure on the previous page shows only one layer for antenna port 0. LTE features MIMO antenna techniques supporting up to 8 antennas. Thus, in reality, there is one such grid per antenna port. The position of the pilots change depending on the antenna ports. The pilots on one antenna most remain silent in all the others in order to avoid interference at pilot positions.

Note also that the first three OFDM symbols in each sub-frame, excluding pilot positions, are reserved for control information. An LTE BS uses these resources to broadcast important information to all users, e.g., number of assigned Resource Blocks (RBs), modulation used, coding used, *etc.* It is important to mention that this control information spans the entire transmission bandwidth regardless the load of the network. However, the number of OFDM symbols used for control information varies from 1 to 3.

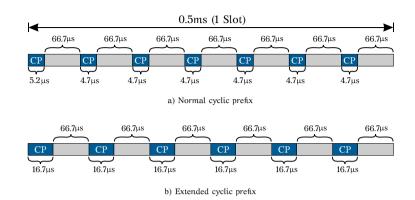

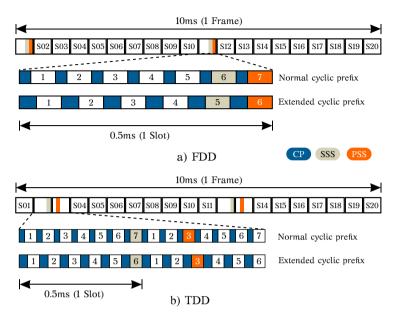

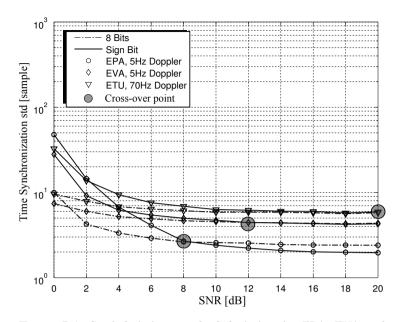

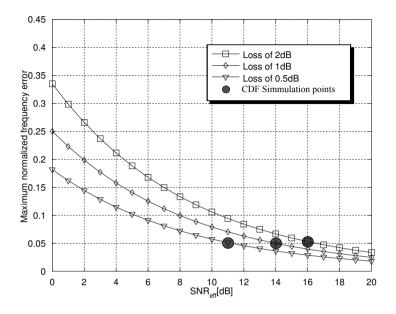

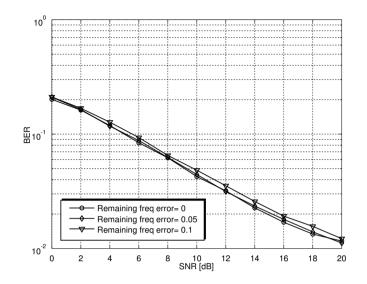

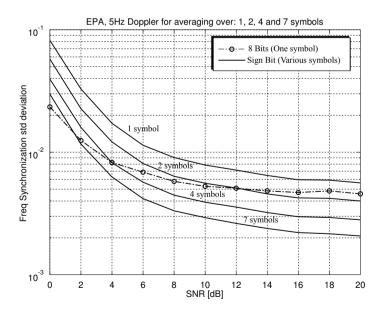

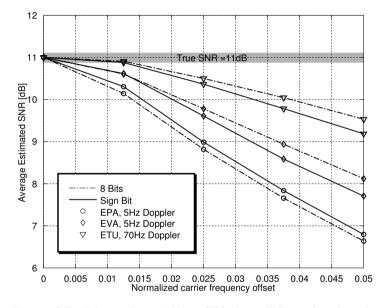

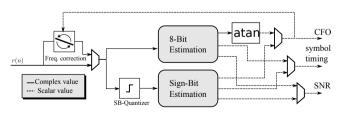

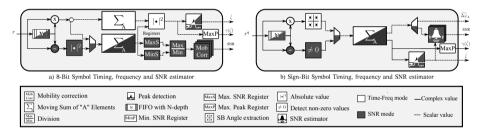

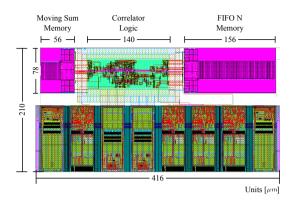

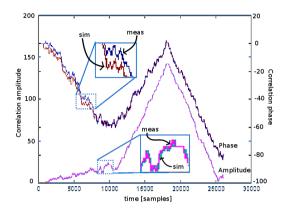

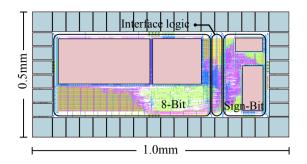

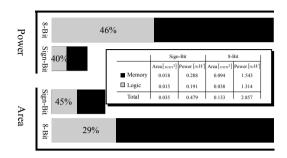

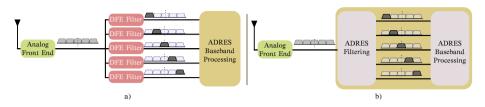

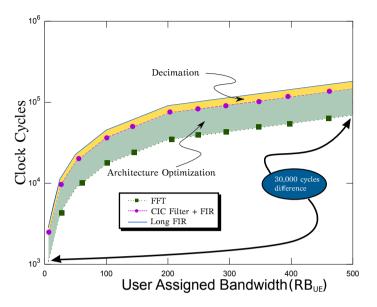

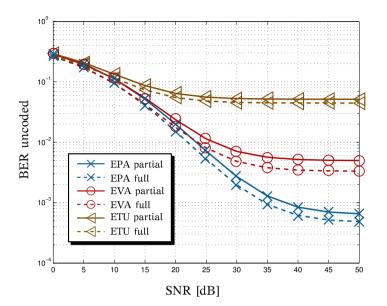

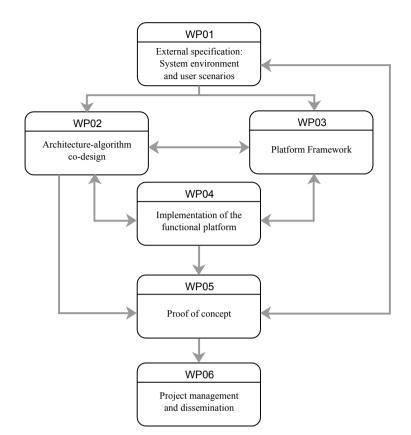

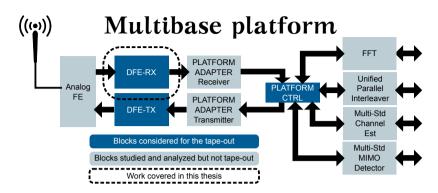

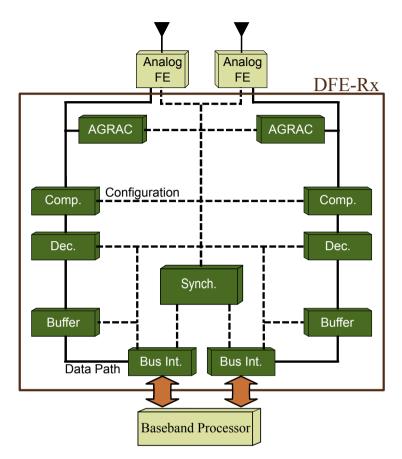

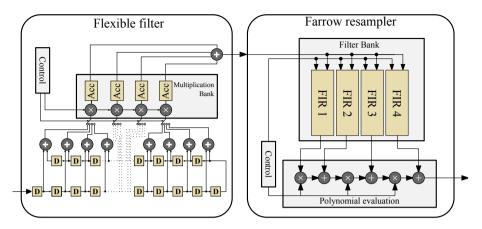

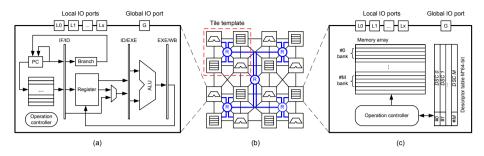

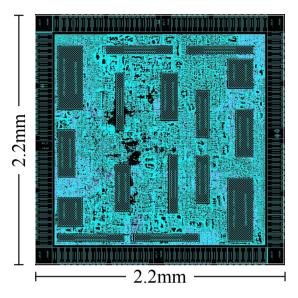

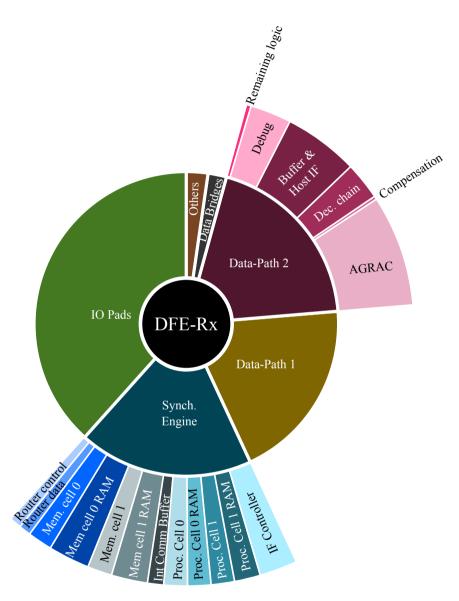

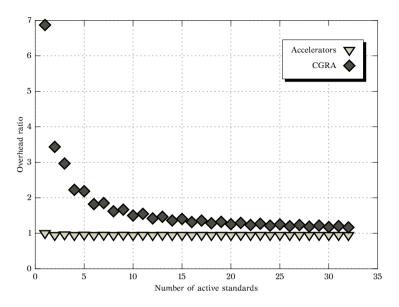

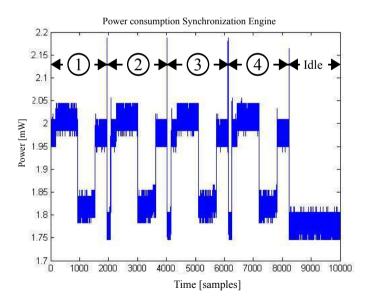

In the time domain, the physical layer is divided into frames, where each frame is 10 ms long and contains 10 sub-frames of 1 ms each. A further partition is done in slots; each sub-frame contains 2 slots of 0.5ms each. The final partition is into OFDM symbols; each slot contains 7, 6, or 3 symbols, in normal CP, extended CP and Multimedia Broadcast Single Frequency Network (MBSFN) mode, respectively.