#### **Electrical Characterisation of III-V Nanowire MOSFETs**

Hellenbrand, Markus

2020

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

Hellenbrand, M. (2020). *Electrical Characterisation of III-V Nanowire MOSFETs*. [Doctoral Thesis (compilation), Lund University]. Department of Electrical and Information Technology, Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# **Electrical Characterisation**of III-V Nanowire MOSFETs

**Doctoral Thesis**

Markus Hellenbrand

Department of Electrical and Information Technology Lund, May 2020

Academic thesis for the degree of Doctor of Philosophy, which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Friday, 12 June, 2020, at 9:15 a.m. in lecture hall E:1406, Department of Electrical and Information Technology, Ole Römers Väg 3, 223 63 Lund, Sweden. The thesis will be defended in English.

The Faculty Opponent will be Professor Tibor Grasser, TU Wien, Austria.

| Organisation: LUND UNIVERSITY Department of Electrical and Information Technology Ole Römers Väg 3 | Document Type:<br>DOCTORAL THESIS                                                                       |  |  |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                    | Date of Issue:<br>May 2020                                                                              |  |  |

| 223 63 Lund<br>Sweden                                                                              | Sponsoring Organisation(s):                                                                             |  |  |

| Author:<br>Markus Hellenbrand                                                                      | Swedish Foundation for Strategic Research (SSF)<br>Swedish Research Council (VR)<br>European Union (FU) |  |  |

Title:

Electrical Characterisation of III-V Nanowire MOSFETs

#### Abstract:

The ever increasing demand for faster and more energy-efficient electrical computation and communication presents severe challenges for the semiconductor industry and particularly for the metal-oxide-semiconductor field-effect transistor (MOSFET), which is the workhorse of modern electronics. III-V materials exhibit higher carrier mobilities than the most commonly used MOSFET material Si so that the realisation of III-V MOSFETs can enable higher operation speeds and lower drive voltages than that which is possible in Si electronics. A lowering of the transistor drive voltage can be further facilitated by employing gate-all-around nanowire geometries or novel operation principles. However, III-V mosterials bring about their own challenges related to material quality and to the quality of the gate oxide on top of a III-V MOSFET channel.

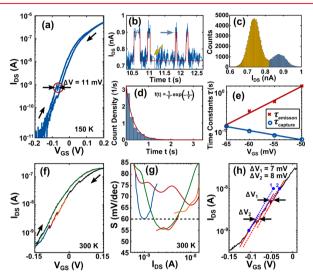

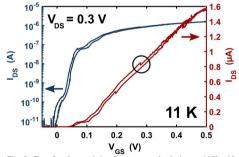

This thesis presents detailed electrical characterisations of two types of (vertical) III-V nanowire transistors: MOSFETs based on conventional thermionic emission; and Tunnel FETs, which utilise quantum-mechanical tunnelling instead to control the device current and reach inverse subthreshold slopes below the thermal limit of 60 mV/decade. Transistor characterisations span over fourteen orders of magnitude in frequency/time constants and temperatures from 11 K to 370 K.

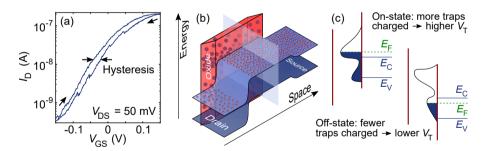

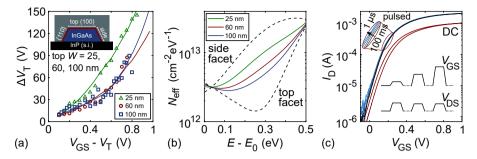

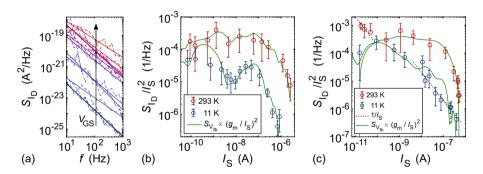

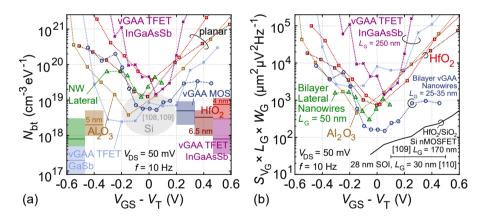

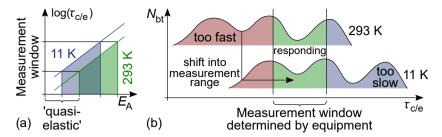

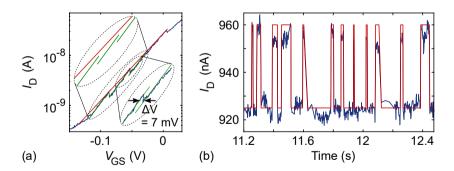

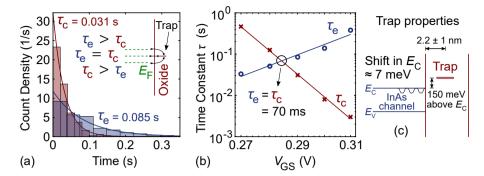

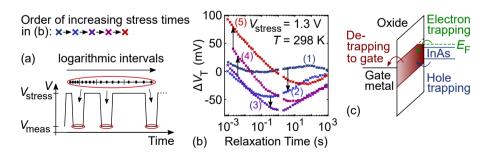

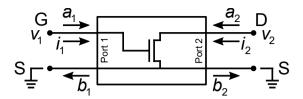

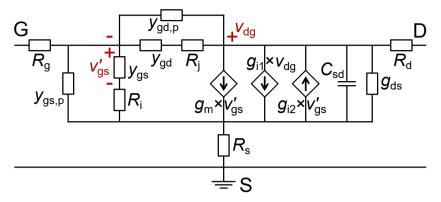

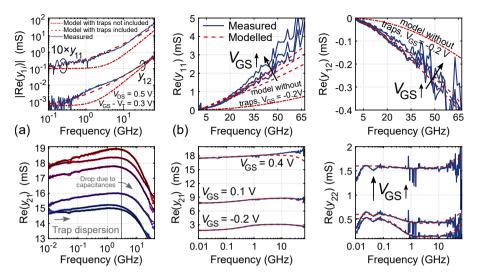

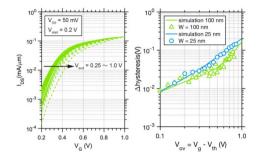

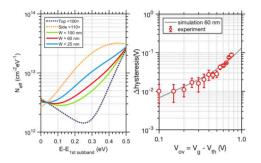

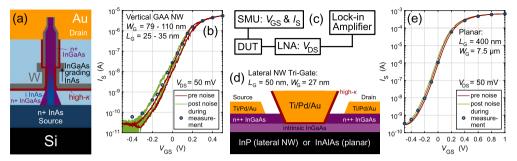

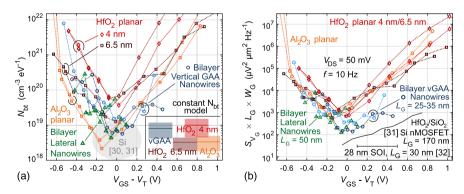

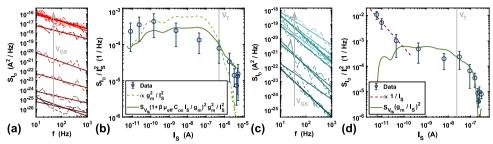

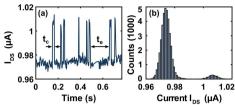

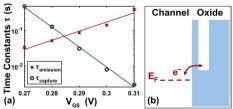

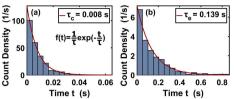

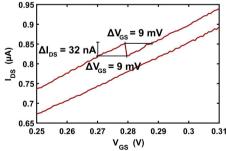

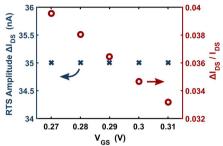

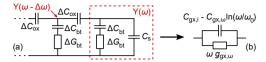

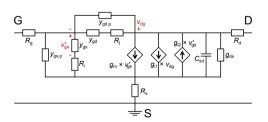

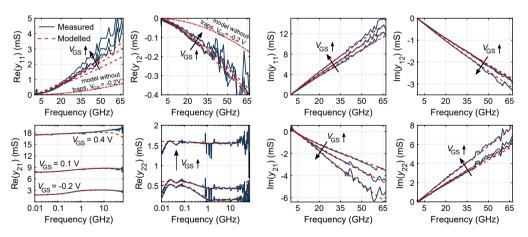

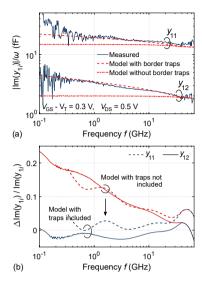

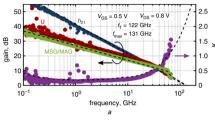

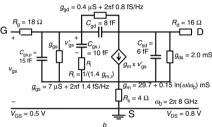

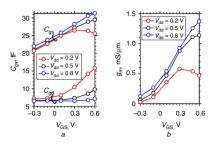

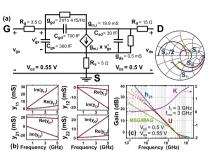

The first part of the thesis focusses on the characterisation of electrically active material defects ('traps') related to the gate stack. Low-frequency noise measurements yielded border trap densities of  $10^{18}$  to  $10^{20}$  cm<sup>-3</sup> eV<sup>-1</sup> and hysteresis measurements yielded effective trap densities – projected to the oxide/semiconductor interface – of  $2 \times 10^{12}$  to  $3 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>. Random telegraph noise measurements revealed that individual oxide traps can locally shift the channel energy bands by a few meV and that such defects can be located at energies from inside the semiconductor band gap all the way into the conduction band. Small-signal radio frequency (RF) measurements revealed that parts of the wide oxide trap distribution can still interact with carriers in the MOSFET channel at gigahertz frequencies. This causes frequency hystereses in the small-signal transconductance and capacitances and can decrease the RF gains by a few decibels. A comprehensive small-signal model was developed, which takes into account these dispersions, and the model was applied to guide improvements of the physical structure of vertical RF MOSFETs. This resulted in values for the cutoff frequency  $f_{\rm T}$  and the maximum oscillation frequency  $f_{\rm max}$  of about 150 GHz in vertical III-V nanowire MOSFETs.

Bias temperature instability measurements and the integration of (lateral) III-V nanowire MOSFETs in a back end of line process were carried out as complements to the main focus of this thesis. The results of this thesis provide a broad perspective of the properties of gate oxide traps and of the RF performance of III-V nanowire transistors and can act as guidelines for further improvement and finally the integration of III-V nanowire MOSFETs in circuits.

#### Keywords:

MOSFET, TFET, III-V, Nanowire, Hysteresis, Low-Frequency Noise, Random Telegraph Noise, cryogenic, Reliability, Radio Frequency, Small-Signal Model.

| Classification System and/or Index Terms Electronic Engineering, Nano Technology    |                                          | Language:<br>English                 |  |

|-------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------|--|

| Supplementary Bibliographical Information:<br>–                                     |                                          | ISBN (printed):<br>978-91-7895-519-0 |  |

| Key title and ISSN:<br>Series of Licentiate and Doctoral Theses; 1654-790X, No. 130 |                                          | ISBN (digital):<br>978-91-7895-520-6 |  |

| Recipient's Notes: Number of Pages: 156                                             |                                          | Price:                               |  |

|                                                                                     | Security Classification:<br>Unclassified | •                                    |  |

General Permissions

I, the undersigned, being the copyright owner and author of the above-mentioned thesis and its abstract, hereby grant to all reference sources permission to publish and disseminate said abstract.

Signature: M. William Date: 11 May 2020

## **Electrical Characterisation** of III-V Nanowire MOSFETs

**Doctoral Thesis**

Markus Hellenbrand

Department of Electrical and Information Technology Lund, May 2020 Markus Hellenbrand Department of Electrical and Information Technology Lund University Ole Römers Väg 3, 223 63 Lund, Sweden

Series of Licentiate and Doctoral Theses ISSN 1654-790X, No. 130 ISBN 978-91-7895-519-0 (printed) ISBN 978-91-7895-520-6 (digital)

#### © 2020 Markus Hellenbrand

This thesis is typeset using  $\LaTeX$  2 $_{\mathcal{E}}$  with the body text in Palatino and Goudy Initials, headings in Helvetica, text in figures in Arial, and the body text in Appendix B in Computer Modern.

Frontispiece: Micrograph of a transistor sample with probe tips in contact.

Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden.

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without restriction. "The Road goes ever on and on

Down from the door where it began.

Now far ahead the Road has gone,

And I must follow, if I can,

Pursuing it with weary feet,

Until it joins some larger way,

Where many paths and errands meet.

And whither then? I cannot say."

The Fellowship of the Ring, J. R. R. Tolkien

### **Abstract**

HE ever increasing demand for faster and more energy-efficient electrical computation and communication presents severe challenges for the semiconductor industry and particularly for the metal-oxide-semiconductor field-effect transistor (MOSFET), which is the workhorse of modern electronics. III-V materials exhibit higher carrier mobilities than the most commonly used MOSFET material Si so that the realisation of III-V MOSFETs can enable higher operation speeds and lower drive voltages than that which is possible in Si electronics. A lowering of the transistor drive voltage can be further facilitated by employing gate-all-around nanowire geometries or novel operation principles. However, III-V materials bring about their own challenges related to material quality and to the quality of the gate oxide on top of a III-V MOSFET channel.

This thesis presents detailed electrical characterisations of two types of (vertical) III-V nanowire transistors: MOSFETs based on conventional thermionic emission; and Tunnel FETs, which utilise quantum-mechanical tunnelling instead to control the device current and reach inverse subthreshold slopes below the thermal limit of 60 mV/decade. Transistor characterisations span over fourteen orders of magnitude in frequency/time constants and temperatures from 11 K to 370 K.

The first part of the thesis focusses on the characterisation of electrically active material defects ('traps') related to the gate stack. Low-frequency noise measurements yielded border trap densities of  $10^{18}$  to  $10^{20}$  cm<sup>-3</sup> eV<sup>-1</sup> and hysteresis measurements yielded effective trap densities – projected to the oxide/semiconductor interface – of  $2 \times 10^{12}$  to  $3 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>. Random

telegraph noise measurements revealed that individual oxide traps can locally shift the channel energy bands by a few millielectronvolts and that such defects can be located at energies from inside the semiconductor band gap all the way into the conduction band.

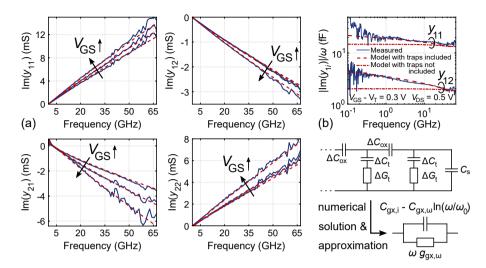

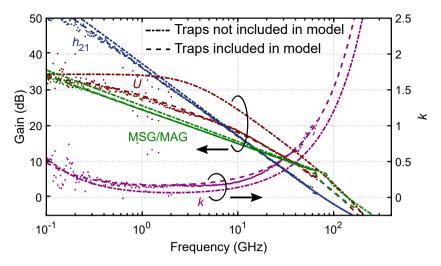

Small-signal radio frequency (RF) measurements revealed that parts of the wide oxide trap distribution can still interact with carriers in the MOSFET channel at gigahertz frequencies. This causes frequency hystereses in the small-signal transconductance and capacitances and can decrease the RF gains by a few decibels. A comprehensive small-signal model was developed, which takes into account these dispersions, and the model was applied to guide improvements of the physical structure of vertical RF MOSFETs. This resulted in values for the cutoff frequency  $f_{\rm T}$  and the maximum oscillation frequency  $f_{\rm max}$  of about 150 GHz in vertical III-V nanowire MOSFETs.

Bias temperature instability measurements and the integration of (lateral) III-V nanowire MOSFETs in a back end of line process were carried out as complements to the main focus of this thesis. The results of this thesis provide a broad perspective of the properties of gate oxide traps and of the RF performance of III-V nanowire transistors and can act as guidelines for further improvement and finally the integration of III-V nanowire MOSFETs in circuits.

### Popular Science Summary

NIMAGINABLE quantities of electrical data are produced, handled and stored all around the globe. It has been estimated that by the year 2030, with the current energy efficiency of computers and networks,

the energy demand related to information and communications technology (ICT) could amount to up to 20 % of the world's total energy consumption. This is in part due to the still increasing spread of ICT to more parts of the world. It is further accelerated by emerging technologies such as the Internet of Things (IoT), Neuromorphic Computing, or Quantum Computing. In view of this, it is clear that a drastic improvement of energy efficiency in computing technology is highly necessary to cover the endless demand for ICT and maybe even to enable its more sustainable employment.

One approach to tackling parts of this enormous problem is the use of *III-V Nanowire Transistors* for advanced electronic circuits. A transistor is an electronic device with three contacts, source, gate, and drain. The gate contact does not conduct any current itself, but controls how much current can flow between source and drain. This can be thought of as similar to a dimmable light switch, which regulates the brightness of the lamps without glowing itself. In a well designed transistor, the highest possible current can be more than 100 000 times as high as the lowest current. Based on this three-contact functionality, transistors are the most fundamental components of ICT systems and act as the 'brain cells' of computers. In this capacity, several billion transistors make up the electronic 'brains' of each of our smartphones and computers and handle all the different tasks that we require of them. In a second capacity, transistors can act as amplifiers and as such, are crucial

for sending and receiving information via internet and telephone communication. An accessible example for this is audio amplifiers, which amplify the small electrical signals containing the audio information so that they can power speakers or headphones. For such communication functionalities, high operation speed is especially important.

In the vast majority of transistors in the world, the *channel*, which conducts the current between source and drain, is made out of silicon, and the gate oxide, by which the gate contact controls the amount of current in the channel, is made out of hafnium oxide. Silicon is widely used, because it is available in large quantities and it is relatively easy to use in fabrication. Unfortunately, current cannot flow very fast in a silicon channel, which imposes severe limitations on transistors in terms of energy efficiency and speed. prediction, in the beginning, of rising energy demand is partly because of this limited channel conductivity. This is where III-V materials - compounds of elements from groups III and V in the periodic table – come into play. Current can flow much faster in these materials, which means that a transistor made out of III-V materials requires less energy to achieve the same performance as a silicon transistor. Alternatively, with the same power consumption, a III-V transistor can operate at a higher speed than a silicon transistor. Further improvements can be achieved by changing the geometry of a transistor, e.g. by making it into the shape of a tiny wire – a 'nanowire' – or by manipulating its physical operation principles.

Unfortunately, with III-V materials it is much more challenging than with silicon to fabricate transistors with a high material quality. It is thus not straightforward to use the superior transport properties of III-V materials to full capacity. For this thesis, I measured the performance of transistors made out of III-V materials and investigated, how their performance is affected by imperfections in the gate oxide. Measurements were carried out at frequencies from 100 µHz to 67 GHz, where the latter is 670 million million(!) times as fast as the former. For comparison, the processor of a normal home computer operates at about 2–4 GHz and typical WiFi links operate at 2.4 GHz or 5 GHz. Furthermore, transistors were measured at temperatures from  $-260\,^{\circ}\text{C}$  to investigate certain physical mechanisms and to explore capabilities for e.g. quantum computing or space applications, up to temperatures of 100 °C to comply with specifications for industrial applications. The thesis thus provides a broad perspective of transistors for applications from ultra-low power IoT and quantum applications to high-speed gigahertz applications for wireless communication.

### Acknowledgments

"It's a dangerous business, going out of your door. You step into the Road, and if you don't keep your feet, there is no knowing where you might be swept off to."

The Fellowship of the Ring, J. R. R. Tolkien

have had the privilege of travelling with many wonderful people and here I express my heartfelt gratitude. First of all, thank you *Lars-Erik* and *Erik*, my supervisors, for pointing the way and guiding me through these years. *Lars-Erik*, thank you for opening the door and allowing me to pursue PhD studies in the *Nanoelectronics* group. I learned a great many things from you, not only about hard science, but also about 'academic diplomacy', the general dealings of research and academia, and especially about positivity. *Erik*, thank you for your endless patience with my unending torrents of questions, and thank you for providing a 'sounding board' for my views on 'how to do science'. I feel very lucky to have had you as my supervisors and I am certain that I will often be taking leaves out of your books in my future scientific endeavours.

Thank you *Johannes* for your enthusiasm about so many things and for all the very practical support. Among my PhD colleagues, a special thanks goes to *Elvedin*, with whom I worked the most in the beginning of my journey and who showed me a lot of 'how things are done' as a PhD student. I thank all my colleagues in our group with whom I had the privilege and the pleasure to work (in loose chronological, but mostly random order) – *Aein*, *Guntrade*, *Cezar*, *Martin*, *Kristofer*, *Jun*, *Karl-Magnus*, *Olli-Pekka*, *Sebastian*, *Lars*, *Fredrik*, *Mattias*, *Adam*, *Stefan*, *Abinaya*, *Lasse*, *Anton*, *Robin*, *Saketh*, *Navya*, *Gautham*, *Heera*, *Zhongyunshen*, *Patrik* – and all colleagues at the department. Thank you all for your fellowship and friendship and for the great working atmosphere. You are all truly special people and I wish I knew you much better than I do.

During the later stage of my PhD I had the fantastic opportunity to work with *Paul* and *Enrico* from the Tyndall Institute in Cork, and *Vamsi* and *Jacopo* from IMEC in Leuven. Thank you for many enlightening discussions and the great (ongoing) collaborations to unravel the mysteries of a few nanometres of oxide.

Thank you *Daniel*, *Anne*, *Pia*, *Dorthe*, both *Elisabeths*, *Linda*, both *Eriks*, *Bertil*, *Göran*, *Andreas*, *Sirvan*, *Martin*, *Josef* – without your administrative and technical support we could not focus on science as much as we do.

Although it is not always apparent as a PhD student, there is a life outside of university. For framing this, first and foremost I thank my oldest and best friends *Kevin* and *Sudha* in 'good old' Heidelberg and in here in Lund, respectively, and also my 'a little bit newer' closest friends *Ali* and *Kush*. Thank you for going out the door with me, for keeping me company on the Road, and for making sure I did not get swept off.

Most of my time outside of university I probably spent at *Domino*, the catholic student community in Lund. I met so many wonderful people here that it is impossible to name all of you. Still I should like to thank some of you by name, whom I have known the best and for the longest – *Magda* and *Magnus*, *Milan*, both *Simons*, *Leonardo*, *Märta* and *Jacob*, *Daniel*, *Imran*, *Kasia*, *Imelda*, *Camila*, *Leny*, *Anna*, *Anna Caterina*, and 'in the old days' *Elin*, *Victor*, *Alexander* and *Cassandra*, *Karin*, *Constantine*, *Ellen*, and *Evelina*. Already the list is quite long, so I hope that everyone missing understands my predicament. At least I maintain that while "I don't know half of you as well as I should like", the second part of this famous quote is certainly not true. Thank you as well for your fellowship and friendship and for keeping me company on the Road. I thank the Dominican brothers in Lund for a spiritual as well as a very physical home for many years; *Björn*, *Paul-Dominique*, *Pierre-André*, *Hani*, *Henrik*, and *Johan*.

Now far ahead the Road has gone indeed, and here at the end, not of all things, but of this very Road, I am glad that my family is with me. *Mama und Papa, Anne und Stefan, Oma und Opa,* thank you for your unconditional love and kindness, for your help and support, for the very ground that my Road has ever been built upon, and thank you for providing the Grey Havens to which I can always return; because in the end, I am "only quite a little fellow in a wide world after all!"

Markers William Lund, April 2020

– -----, - -<u>F</u> ----

<sup>&</sup>lt;sup>†</sup>The Fellowship of the Ring, J. R. R. Tolkien.

<sup>&</sup>lt;sup>‡</sup>The Hobbit, J. R. R. Tolkien.

## Contents

| Abstract                                           |   | V     |

|----------------------------------------------------|---|-------|

| Popular Science Summary                            |   | vii   |

| Acknowledgments                                    |   | ix    |

| Contents                                           |   | xi    |

| Preface                                            | : | xiii  |

| Structure of the Thesis                            |   | xiii  |

| Included Papers                                    |   | xiv   |

| Related Work                                       |   | XV    |

| Acronyms and Symbols                               | > | (vii  |

| Acronyms and Abbreviations                         | : | xvii  |

| Latin Symbols                                      | x | cviii |

| Greek Symbols                                      |   | xxi   |

| INTRODUCTION                                       |   | 1     |

| 1 Survey of the Field                              |   | 3     |

| 1.1 Motivation of the Conducted Research           |   | 3     |

| 1.2 A Brief History of the Field-Effect Transistor |   | 4     |

| 1.3 Basic MOSFET Operation                         |   | 5     |

| 1.4 Dennard Scaling, Moore's Law and Beyond        |   | 6     |

| 1.4.1 Materials and MOSFET Performance                  | 6                                                                |

|---------------------------------------------------------|------------------------------------------------------------------|

| 1.4.2 Geometries                                        | 10                                                               |

| 1.5 Performance Overview                                | 12                                                               |

| 1.5.1 DC Metrics                                        | 12                                                               |

| 1.5.2 High Frequency Metrics                            | 14                                                               |

| 1.6 New Physics – Tunnel FETs                           | 16                                                               |

| 2 Characterisation of Gate Oxide Defects                | 21                                                               |

| 2.1 Physical Origins and Charge Exchange Mechanisms     | 21                                                               |

| 2.2 Hysteresis in IV Curves                             | 24                                                               |

| 2.3 Many Traps – Low-Frequency Noise                    | 26                                                               |

| 2.4 On Elastic and Inelastic Tunnelling in LFN          | 31                                                               |

| 2.5 Individual Traps – Random Telegraph Noise           | 33                                                               |

| 2.6 Reliability and Lifetime                            | 36                                                               |

| 2.7 Outlook – Towards a Unified Trap Distribution       | 38                                                               |

| 3 Radio Frequency Characterisation                      | 39                                                               |

| 3.1 The Small-Signal Model Including Gate Oxide Defects | 39                                                               |

| 3.2 On the Origin of the Oxide Trap Components          | 44                                                               |

|                                                         |                                                                  |

|                                                         | 46                                                               |

| 3.3 Improved RF Performance                             | 46<br>51                                                         |

| 3.3 Improved RF Performance                             |                                                                  |

| 3.3 Improved RF Performance                             | 51                                                               |

| 3.3 Improved RF Performance                             | 51<br><b>53</b>                                                  |

| 3.3 Improved RF Performance                             | <ul><li>51</li><li>53</li><li>55</li><li>69</li></ul>            |

| 3.3 Improved RF Performance                             | <ul><li>51</li><li>53</li><li>55</li><li>69</li><li>71</li></ul> |

| 3.3 Improved RF Performance                             | <ul><li>51</li><li>53</li><li>55</li><li>69</li></ul>            |

### **Preface**

HIS thesis is the culmination of more than five years of work in the *Nanoelectronics* group at Lund University and presents detailed characterisations of vertical III-V nanowire metal-oxide-semiconductor field-effect transistors (MOSFETs) for low power and high frequency applications. The analyses span over fourteen orders of magnitude in frequency and were supported by many different researchers. The work was supervised by Professor *Lars-Erik Wernersson* and Professor *Erik Lind*.

#### STRUCTURE OF THE THESIS

The thesis is divided into three main parts. First, a survey of the part of the field of nanoelectronics related to this thesis will present some fundamental principles underlying the operation of III-V nanowire MOSFETs. This will put the studied transistors into perspective relative to the current state of academic research and industry by comparing some of the key metrics of transistor operation. The second part will present the conducted work pertaining to effects of gate oxide defects in DC operation and at low frequencies, which in the context of this thesis is below about 10 kHz. The third part will summarise radio frequency characterisations of nanowire MOSFETs from 10 MHz to 67 GHz. The analysis of gate oxide defects reaches over into this chapter, but more critical properties are investigated as well.

#### INTRODUCTION

The main body of the thesis consists of the publications appended in the back. The Introduction provides a broader and more comprehensive view than the very focussed publications and ties their work together. The Introduction is intended to be comprehensible for aspiring researchers with a Master's degree in physics or a related subject.

#### APPENDICES

#### A Measurement Setups

Appendix A provides a description of the measurement of low-frequency noise and scattering parameters.

#### B Small-Signal Analysis in Detail

Appendix B provides a detailed treatise of the measurement and modelling of small-signal parameters beyond the content of this thesis.

#### PAPERS

The papers forming the main body of the thesis are reproduced in the back and listed in the following.

It should be noted that while the characterisations in this thesis were carried out in close interaction with the design of processing schemes, processing itself is not a part of this thesis. Samples were provided by E. Memišević, O.-P. Kilpi, A. Jönsson, A. Krishnaraja, C. Zota, and F. Lindelöw.

#### **INCLUDED PAPERS**

The following papers form the main body of this thesis and the respective published or draft versions are appended in the back.

- Paper I: S. Netsu, M. Hellenbrand, C. B. Zota, Y. Miyamoto, and E. Lind, "A Method for Determining Trap Distributions of Specific Channel Surfaces in InGaAs Tri-Gate MOSFETs", *IEEE Journal of the Electron Devices Society*, vol. 6, pp. 408–412, Feb. 2018, doi: 10.1109/JEDS.2018.2806487.

- ▶ *I supervised and helped with the measurements and helped to write the paper.*

- Paper II: M. Hellenbrand, O.-P. Kilpi, J. Svensson, E. Lind, and L.-E. Wernersson, "Low-frequency noise in nanowire and planar III-V MOSFETs", *Microelectronic Engineering*, vol. 215, pp. 110986, May 2019, doi: 10.1016/j.mee.2019.110986.

- ▶ I carried out all measurements and analyses and wrote the paper.

- Paper III: M. HELLENBRAND, E. MEMIŠEVIĆ, M. BERG, O.-P. KILPI, J. SVENSSON, AND L.-E. WERNERSSON, "Low-Frequency Noise in III–V Nanowire TFETs and MOSFETs", *IEEE Electron Device Letters*, vol. 38, no. 11, pp. 1520–1523, Sep. 2017, doi: 10.1109/LED.2017.2757538.

- ▶ I carried out all measurements and analyses and wrote the paper.

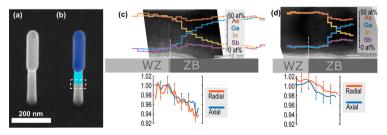

- Paper IV: E. Memisevic, M. Hellenbrand, E. Lind, A. R. Persson, S. Sant, A. Schenk, J. Svensson, R. Wallenberg, and L.-E. Wernersson, "Individual Defects in InAs/InGaAsSb/GaSb Nanowire Tunnel Field-Effect Transistors Operating below 60 mV/decade", *Nanoletters*, vol. 17, no. 7, pp. 4373–4380, Jun. 2017, doi: 10.1021/acs.nanolett.7b01455.

- ▶ I carried out the measurements and analyses pertaining to the effects of gate oxide defects and wrote the corresponding part of the paper.

- Paper V: M. Hellenbrand, E. Memišević, J. Svensson, E. Lind, and L.-E. Wernersson, "Random Telegraph Signal Noise in Tunneling Field-Effect Transistors with S below 60 mV/decade", 2017 47th European Solid-State Device Research Conference (ESSDERC), pp. 38–41, Sep. 2017, doi: 10.1109/ESSDERC.2017.8066586.

- ► I carried out all measurements and analyses, wrote the paper, and presented it at the conference.

- **Paper VI:** M. HELLENBRAND, E. LIND, O.-P. KILPI, AND L.-E. WERNERSSON, "Effects of traps in the gate stack on the small-signal RF response of III-V nanowire MOSFETs", *Solid-State Electronics*, under review with minor revisions pending, May 2020.

- ► I carried out the majority of the measurements, all analyses, developed and implemented the model, and wrote the paper.

- Paper VII: O.-P. KILPI, M. HELLENBRAND, J. SVENSSON, E. LIND, AND L.-E. WERNERSSON, "Vertical nanowire III–V MOSFETs with improved high-frequency gain", *Electronics Letters*, Article in Press, Apr. 2020, doi: 10.1049/el.2020.0266.

- ▶ I carried out part of the high frequency measurements, analysed the small-signal model, and wrote part of the paper.

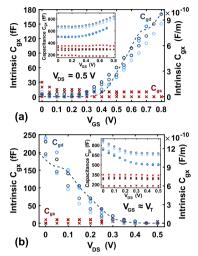

- Paper VIII: M. Hellenbrand, E. Memisevic, J. Svensson, A. Krishnaraja, E. Lind, and L.-E. Wernersson, "Capacitance Measurements in Vertical III–V Nanowire TFETs", *IEEE Electron Device Letters*, vol. 39, no. 7, pp. 943–946, May 2018, doi: 10.1109/LED.2018.2833168.

- ▶ *I carried out all measurements and analyses and wrote the paper.*

#### **RELATED WORK**

The following publications are not included in the thesis, but summarise related work that I was involved in. The work is divided into peer-reviewed journal papers and conference contributions and is listed according to the thematic order of the thesis.

#### **JOURNAL PAPERS**

- Paper ix: E. Memišević, J. Svensson, M. Hellenbrand, E. Lind, and L.-E. Wernersson, "Scaling of Vertical InAs–GaSb Nanowire Tunneling Field-Effect Transistors on Si", *IEEE Electron Device Letters*, vol. 37, no. 5, pp. 549–552, Mar. 2016, doi: 10.1109/LED.2016.2545861.

- Paper x: E. Memisevic, E. Lind, M. Hellenbrand, J. Svensson, and L.-E. Wernersson, "Impact of Band-Tails on the Subthreshold Swing of III–V Tunnel Field-Effect Transistor", *IEEE Electron Device Letters*, vol. 38, no. 12, pp. 1661–1664, Oct. 2017, doi: 10.1109/LED.2017.2764873.

- **Paper xi:** C. Möhle, C. B. Zota, <u>M. Hellenbrand</u>, and E. Lind, "1/f and RTS noise in InGaAs nanowire MOSFETs", *Microelectronic Engineering*, vol. 178, pp. 52–55, May 2017, doi: 10.1016/j.mee.2017.04.038.

- Paper xii: M. Berg, O.-P. Kilpi, K.-M. Persson, J. Svensson, M. Hellenbrand, E. Lind, and L.-E. Wernersson, "Electrical Characterization and Modeling of Gate-Last Vertical InAs Nanowire MOSFETs on Si", IEEE Electron Device Letters, vol. 37, no. 8, pp. 966–969, Jun. 2016, doi: 10.1109/LED.2016.2581918.

#### **CONFERENCE CONTRIBUTIONS**

- Paper xiii: E. Memisevic, J. Svensson, M. Hellenbrand, E. Lind, and L.-E. Wernersson, "Vertical InAs/GaAsSb/GaSb Tunneling Field-Effect Transistor on Si with S = 48 mV/decade and  $I_{on} = 10 \,\mu\text{A}/\mu\text{m}$  for  $I_{off} = 1 \,\text{nA}/\mu\text{m}$  at  $V_{DS} = 0.3 \,\text{V}''$ , 2016 IEEE International Electron Devices Meeting, pp. 19.1.1–19.1.4, Dec. 2016, doi: 10.1109/IEDM.2016.7838450.

- Paper xiv: M. HELLENBRAND, O.-P. KILPI, J. SVENSSON, E. LIND, AND L.-E. WERN-ERSSON, "Comparison of Low-Frequency Noise in Nanowire and Planar III-V MOSFETS", 21st Conference on Insulating Films on Semiconductors (INFOS), Jun. 2019.

- **Paper xv:** C. Möhle, C. B. Zota, <u>M. Hellenbrand</u>, and E. Lind, "1/f and RTS noise in InGaAs nanowire MOSFETs", 20th Conference on Insulating Films on Semiconductors (INFOS), Jun. 2017.

- Paper xvi: M. Hellenbrand, E. Memisevic, J. Svensson, A. Krishnaraja, E. Lind, and L.-E. Wernersson, "Effect of Gate Oxide Defects on Tunnel Transistor RF Performance", 76th Device Research Conference (DRC), pp. 137–138, Jun. 2018, doi: 10.1109/DRC.2018.8442145.

### Acronyms and Symbols

Here, important acronyms, abbreviations, and symbols are listed, which are recurring throughout the thesis. Some parameters, which only occur in a narrow context, are intentionally omitted; some parameters are used in more than one way, but the context is always explicitly clarified in the corresponding text. Some (compound) units are provided with prefixes to reflect the most commonly encountered notations in the literature.

#### **ACRONYMS AND ABBREVIATIONS**

AC Alternating Current

**ALD** Atomic Layer Deposition

**BEOL** Back End of Line

BTBT Bant-to-Band Tunnelling

BTI Bias Temperature Instability

**CMF** Correlated Mobility Fluctuations

**CV** Capacitance-Voltage

DC Direct Current

**DFT** Density Functional Theory

**DOS** Density of States

**GAA** Gate-All-Around

ICT Information and Communications Technology

II Impact Ionisation

IoT Internet of Things

IV Current-Voltage

**LFN** Low-Frequency Noise

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NDR Negative Differential Resistance

NQS Non-Quasi-Static

RC Resistance-Capacitance

**RF** Radio Frequency

RTN Random Telegraph Noise

s-parameter Scattering Parameter

**SEM** Scanning Electron Microscope

**SOI** Silicon on Insulator

**TFET** Tunnel Field-Effect Transistor

WKB Wentzel-Kramers-Brillouin

*y*-parameter Admittance Parameter

**z-parameter** Impedance Parameter

#### **LATIN SYMBOLS**

| $Al_2O_3$         |                           | Aluminium Oxide                                                          |

|-------------------|---------------------------|--------------------------------------------------------------------------|

| $C_{gx}$          | F                         | Small-Signal Gate-to-Drain (x=d) or Gate-<br>to-Source (x=s) Capacitance |

| $C_{it}$          | F, F cm <sup>-2</sup>     | Interface Trap Capacitance, typically normalised by the gated area       |

| $C_{ox}$          | $F, Fm^{-2}, Fm^{-1}$     | Gate Oxide Capacitance, often normalised by area or length               |

| $C_{\mathbf{q}}$  | $F, Fm^{-2}, Fm^{-1}$     | Gate Oxide Capacitance, often normalised by area or length               |

| $C_{\rm sd}$      | F                         | Small-Signal Drain-to-Source Capacitance                                 |

| $D_{\mathrm{it}}$ | $\mathrm{cm^{-2}eV^{-1}}$ | Interface Trap Density                                                   |

| $E_{\mathbf{A}}$  | eV                        | Activation Energy                                                        |

| $E_{ m F}$ eV Fermi Level Energy $E_{ m g}$ eV Band Gap $E_{ m V}$ eV Valence Band Energy                 |           |

|-----------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                           |           |

| E <sub>V</sub> eV Valence Band Energy                                                                     |           |

| f Hz Frequency                                                                                            |           |

| $f_{\max}$ Hz Maximum Oscillation Frequency                                                               |           |

| $f_{\mathrm{T}}$ Hz Cutoff Frequency                                                                      |           |

| g <sub>ik</sub> S Small-Signal Conductance of Band Tunnelling and Impact Ionis                            |           |

| g <sub>ds</sub> S Output Conductance                                                                      |           |

| $g_m$ S, mS $\mu m^{-1}$ Transconductance, often normalise gate width                                     | ed by the |

| <b>Ge</b> Germanium                                                                                       |           |

| $h$ $\approx 6.626 \times 10^{-34}$ Js, Planck Constant                                                   | nt        |

| $\hbar$ $\approx 1.055 \times 10^{-34}$ Js, Reduced Planstant                                             | nck Con-  |

| <i>h</i> <sub>21</sub> dB Forward Current Gain                                                            |           |

| HfO <sub>2</sub> Hafnium Dioxide                                                                          |           |

| $I_{\rm D}$ A, mA $\mu {\rm m}^{-1}$ Drain Current, often normalised gate width                           | l by the  |

| $I_{DS}$ A, mA $\mu$ m <sup>-1</sup> Source-to-Drain Current, often not by the gate width                 | rmalised  |

| $I_{G}$ A, mA $\mu$ m <sup>-1</sup> Gate Current, often normalised by width                               | the gate  |

| InAs Indium Arsenide                                                                                      |           |

| InGaAs Indium Gallium Arsenide                                                                            |           |

| $I_S$ A, mA µm <sup>-1</sup> Source Current, often normalised gate width                                  | d by the  |

| k Stability Factor                                                                                        |           |

| $k_{\rm B}$ $\approx 1.381 \times 10^{-23} \text{ kg m}^2 \text{ K}^{-1} \text{ s}^{-1}$ , Bo<br>Constant | ltzmann   |

| L <sub>G</sub> m Gate Length                                                                              |           |

| $m_0$ $\approx 9.109 \times 10^{-31}$ kg, Electron Rest                                                   | Mass      |

| $m^*$ $m_0$ Effective Mass                                                                                |           |

| MAG dB Maximum Available Gain                                                                             |           |

| MSG                                              | dB                                                              | Maximum Stable Gain                                                                                           |  |  |

|--------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| $n \ N_{ m bt} \ N_{ m eff}$                     | $cm^{-3}, cm^{-2}, cm^{-1}$ $cm^{-3} eV^{-1}$ $cm^{-2} eV^{-1}$ | Carrier Concentration Border Trap Density Effective (Defect) Density                                          |  |  |

| q                                                |                                                                 | $\approx 1.602 \times 10^{-19}$ C, Elemental Charge                                                           |  |  |

| $R_{\rm i}, R_{\rm j}$                           | Ω                                                               | Intrinsic Non-Quasi-Static Channel Resistances                                                                |  |  |

| S<br>Si                                          | mV/decade                                                       | Inverse Subthreshold Slope<br>Silicon                                                                         |  |  |

| $S_{\mathbf{I_D}}$                               | $\mathrm{A^2Hz^{-1}}$                                           | Drain Current Noise Power Spectral Density                                                                    |  |  |

| $SiO_2$<br>$S_{V_G}$                             | $V^2Hz^{-1}$                                                    | Silicon Dioxide<br>Equivalent Gate Voltage Noise Power<br>Spectral Density                                    |  |  |

| $t_{ m ox} \ T_{ m BTB}$                         | m                                                               | Oxide Thickness<br>Band-to-Band Tunnelling Probability                                                        |  |  |

| T                                                | K, °C                                                           | Temperature                                                                                                   |  |  |

| И                                                | dB                                                              | Unilateral Power Gain                                                                                         |  |  |

| $v_{ m inj} \ v_{ m th} \ V_{ m DS} \ V_{ m fb}$ | ${ m ms^{-1}} \ { m ms^{-1}} \ { m V} \ { m V}$                 | Injection Velocity Thermal Velocity Drain-to-Source Voltage Flatband Voltage                                  |  |  |

| $V_{ m GD}$                                      | V                                                               | Gate-to-Drain Voltage                                                                                         |  |  |

| $V_{ m GS}$                                      | V                                                               | Gate-to-Source Voltage                                                                                        |  |  |

| $V_{\mathrm{SD}}$                                | V                                                               | Source-to-Drain Voltage                                                                                       |  |  |

| $V_{\mathrm{T}}$                                 | V                                                               | Threshold Voltage                                                                                             |  |  |

| $W_{G}$                                          | m                                                               | Gate Width                                                                                                    |  |  |

| x                                                | m                                                               | Distance in x-direction                                                                                       |  |  |

| $y_{\mathrm{gx}},y_{\mathrm{gx,p}}$              | S                                                               | Intrinsic and Parasitic (p) Small-Signal Conductances between Gate (g) and either Drain (x=d) or Source (x=s) |  |  |

| $y_{kl}$                                         | S                                                               | y-parameter with indices $k$ and $l$                                                                          |  |  |

#### **GREEK SYMBOLS**

| $\mathrm{eV}^{-1}$                   | Non-Parabolicity Factor                                                   |

|--------------------------------------|---------------------------------------------------------------------------|

| $\mathrm{Vs}\mathrm{C}^{-1}$         | Scattering Factor                                                         |

|                                      | Stress-Time Exponent                                                      |

|                                      | Hooge Parameter                                                           |

|                                      | Frequency Exponent, Voltage Acceleration Factor                           |

|                                      | Dennard Scaling Factor, Relative Permittivity                             |

| m                                    | Tunnelling Attenuation Length                                             |

| ${\rm cm^2V^{-1}s^{-1}}$             | Electron/Hole Mobility                                                    |

| ${\rm cm}^2{\rm V}^{-1}{\rm s}^{-1}$ | Effective Carrier Mobility                                                |

| V                                    | Surface Potential                                                         |

| s                                    | Characteristic Time Constant                                              |

| s                                    | Time Constant Effective Pre-Factor                                        |

| s                                    | Capture/Emission Time Constant                                            |

| ${\rm rad}{\rm s}^{-1}$              | Angular Frequency                                                         |

| ${\rm rad}{\rm s}^{-1}$              | Angular Trap Cutoff Frequency                                             |

|                                      | Universal Relaxation Time                                                 |

| $\rm Vm^{-1}$                        | Maximum Electric Field                                                    |

|                                      | $VsC^{-1}$ $m$ $cm^2V^{-1}s^{-1}$ $V$ $s$ $s$ $s$ $rads^{-1}$ $rads^{-1}$ |

# **INTRODUCTION**

### Survey of the Field

LL our lives as well as the organisation of most human societies are interfused with myriads of electronic applications. Smartphones, computers, networks and databases, advanced medical care and research have all been enabled by the invention and continuous development of a now minute device called *Metal-Oxide-Semiconductor Field-Effect Transistor* (MOSFET); and transistors have become the single most abundantly mass-produced human artefact of all time. Their continuous improvement since their invention in the 1950s has been so rapid that today's smartphones possess a computing power that only a few decades ago would have been impossible to achieve at all.

This chapter provides a brief history of the development of the MOSFET as well as benchmarks of current research in order to provide a context and a motivation for the investigations undertaken in the thesis.

#### 1.1 MOTIVATION OF THE CONDUCTED RESEARCH

The basic functionality of a transistor consists in the regulation of a current over several orders of magnitude by a controlling voltage. Based on this principle, different types of transistors are amongst the most essential components of almost all electrical appliances. As the most prominent example, billions of transistors make up every single processor in our computers, laptops, and smartphones, but transistors are also used in smaller numbers in e.g. audio and wireless communication amplifiers, in power supply controllers or as sensors.

The rapid development of the MOSFET since its invention in the 1950s has been driven mainly by the continuous miniaturisation of device dimensions and by the occasional introduction of a new material or a change in the device geometry. Because feature sizes have now decreased to the thickness of only a few atomic layers, geometric scaling is facing fundamental physical limits. Since about the beginning of the 21st century, for further improvement of the device performance in terms of energy efficiency and speed, new materials, new architectures, and new physical operation principles have thus moved into the focus of research efforts [1].

This thesis summarises detailed characterisation work on III-V nanowire MOSFETs, mostly in vertical device architectures, which employ both new materials with respect to the industry standard Si, and a new device architecture with respect to the conventional lateral device orientation. The appeal of III-V materials will be explained in Section 1.4.1 and the appeal of the vertical nanowire architecture in Section 1.4.2. As a special kind of MOSFET, so-called *Tunnel FETs* (TFETs) have been investigated, which are based on new physical operation principles. They will be introduced in Section 1.6. The different types of measurements in this thesis are divided into those related to defects in the gate oxide and those related to high frequency operation.

#### 1.2 A BRIEF HISTORY OF THE FIELD-EFFECT TRANSISTOR

The theoretical principle of the transistor was conceived in the 1920s by the Polish/American physicist Julius Lilienfeld and patented in 1930 [2]. It would take until the late 1940s, however, before the first practical realisation of a transistor could be achieved. In late 1947, the physicists John Bardeen, Walter Brattain, and William Shockley, working at Bell Labs, New Jersey, demonstrated the field-effect and the point-contact transistor [3,4]. Independently, in 1948, the German physicists Herbert Mataré and Heinrich Welker made the same discovery while working at the Compagnie des Freins & Signaux Westinghouse near Paris [5]. A further important step in the history of transistors was the invention of the bipolar junction transistor by William Shockley [6], but this type of transistor was difficult to mass-produce. So the unstoppable digital revolution only took its course when the Egyptian and the Korean engineers Mohamed Atalla and Dawon Kahng, respectively, both working at Bell Labs, experimentally realised the first MOSFET. Again, the concept of the MOSFET had been known for several years, but the presence of electronic states at the surface of the semiconductor, which was to form the conductive channel of the MOSFET, prevented proper control of the current in the devices. The critical step to set the digital revolution into motion was the passivation of these interface states in the Si/SiO<sub>2</sub> material system [7].

Together with the invention of the Integrated Circuit and the Complementary MOS logic [8], this stable Si material system finally heralded the commercial mass production of electronic applications that we enjoy today.

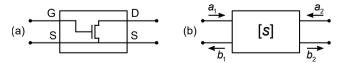

#### 1.3 BASIC MOSFET OPERATION

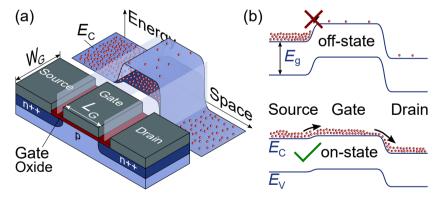

The basic operating principle of a MOSFET is the control of a current between two of its terminals, source and drain, by a voltage at the third terminal, the gate, without a current flowing into or out of the gate itself. The path between source and drain is called *channel* and the control of the gate over the channel as well as their isolation from each other is achieved by the gate oxide, which is a central topic of this thesis. Schematics of the device structure and the described principle of operation are depicted in Fig. 1.1. In such a so-called n-type bulk MOSFET, the source and drain contacts are realised by highly n-doped regions implanted into a p-doped substrate. In a heavily n-doped semiconductor, the Fermi level resides close to the conduction band edge so that a large concentration of electrons is available in the source. In the p-doped channel region on the other hand, the Fermi level lies close to the valance band edge so that without an externally applied voltage  $V_{\rm GS}$  between gate and source, the resulting band structure along a cut from source to drain (Fig. 1.1(b), top) constitutes an energy barrier for the electrons in the source, which the vast majority cannot overcome. The flow of a current is thus not possible between source and drain and the transistor is in its offstate. Upon application of a positive  $V_{GS}$ , an electric field is created via the

**Figure 1.1:** (a) Schematics of a planar MOSFET structure and the corresponding conduction band diagrams for the off- and the on-state (light blue and dark blue, respectively). (b) Corresponding energy band diagrams for the off- and the on-state in 2D along a cut from source to drain in (a).

gate oxide, which modifies the energy barrier in the channel. With increasing  $V_{\rm GS}$ , the barrier decreases, more and more electrons can surmount it, and with a sufficiently large voltage  $V_{\rm DS}$  between source and drain, the source-to-drain current  $I_{\rm DS}$  increases so that the transistor gradually reaches its on-state (Fig. 1.1(b), bottom). Ideally, a MOSFET exhibits high on-currents and low off-currents. The characteristic voltage which separates the on- from the off-state, is called the *threshold voltage*  $V_{\rm T}$ . A fourth contact to the bottom of the device in Fig. 1.1(a) can be used to adjust  $V_{\rm T}$ , but this was not used for any devices in this thesis and is thus disregarded from here on. As mentioned before, in an ideal MOSFET, the gate oxide prevents any current  $I_{\rm G}$  from flowing into the gate contact. In reality, a small leakage current is present, which is however several orders of magnitude lower than  $I_{\rm DS}$ .

#### 1.4 DENNARD SCALING, MOORE'S LAW AND BEYOND

A large part of the route from the first clunky, hand-sized, point-contact transistor to today's high-speed transistors of just a few nanometres was guided by scaling principles known as Dennard scaling. In a paper in 1974 [9], the American electrical engineer Robert H. Dennard and colleagues observed that if the gate length  $L_G$  and width  $W_G$  as well as the gate oxide thickness  $t_{\rm ox}$  (see Fig. 1.1(a)) and the supply voltage are all scaled down by a factor  $1/\kappa$ , while the doping density is scaled up by a factor  $\kappa$ , the switching delay time of the device decreases by  $1/\kappa$ , while its power density (voltage times current per area) remains constant. Widespread adherence to these scaling rules led to Gordon Moore's (co-founder of Intel) famous observation that the number of transistors in an integrated circuit doubles about every two years [10], which ultimately brought us today's state of the art in electronics. In recent years, however, this constant-power scaling has slowed down, because it is facing fundamental physical limits. Other means of improving transistor performance have thus been introduced and the following sections provide an overview of some important developments during the last years.

#### 1.4.1 MATERIALS AND MOSFET PERFORMANCE

The continuous geometric scaling of MOSFETs eventually led to gate oxide thicknesses of just a few atomic layers so that electrons in the transistor channel started tunnelling through these thin oxides. This constituted the first fundamental physical challenge for geometric scaling, since it caused increased gate currents and thus increased power consumption [11]. The challenge could eventually be overcome by the introduction of so-called high- $\kappa$  (not to be confused with Dennard's scaling factor) gate oxides. For a planar capacitor structure, such as the gate stack of a large-area MOSFET,

the capacitance C is calculated as  $C = \epsilon_0 \epsilon_r A/t_{\rm ox}$ , where  $\epsilon_0$  is the vacuum permittivity,  $\epsilon_r$  (called  $\kappa$  in engineering) is the relative permittivity of the capacitor dielectric (i.e. the gate oxide), A is the area, and  $t_{\rm ox}$  the thickness of the oxide. From this it can be seen that instead of thinning down the oxide, the capacitance can be increased by using a material with a higher relative permittivity  $\kappa$ . Since a higher permittivity, however, comes at the cost of a lower band gap  $E_{\rm g}$ , which often leads to a reduced band offset between the oxide and the channel and thus again to increased tunnelling, a compromise had to be found between high values for  $\kappa$  and for  $E_{\rm g}$ . The best compromise proved to be HfO<sub>2</sub> with  $\kappa = 25$  (ideal case) and  $E_{\rm g} \approx 6$  eV [12] so that the too thin SiO<sub>2</sub> ( $\kappa = 3.9$ ) gate oxide was replaced by a thicker HfO<sub>2</sub> gate oxide [13]. At the same time, a metal gate contact was introduced, which suppressed surface scattering at the channel/high- $\kappa$  interface [14] and eliminated the problem of depletion in the previously used polysilicon contacts, which could cause unwanted shifts in the threshold voltage  $V_{\rm T}$  [11].

Besides the change of the MOSFET gate stack, ongoing research is concerned with alternatives to Si as the channel material. III-V materials, which constitute the foundation of devices in this thesis, are one of the most promising options for this due to their outstanding electron transport properties [15]. The materials are referred to as III-V materials, because they are compounds of elements of the (Mendeleev) groups III and V in the periodic table of elements (IUPAC groups 13 and 15) and their outstanding transport characteristics are related to a material property known as the *effective mass m\** of charge carriers. Generally, for parabolic bands, the effective mass can be expressed as a tensor, which depends on the wave vector k. The elements (i, j) of this tensor are defined as [16, p. 243]

$$\left(\frac{1}{m_n^*(\mathbf{k})}\right)_{i,j} = \frac{1}{\hbar^2} \frac{\partial^2 E_n(\mathbf{k})}{\partial k_i \partial k_j},\tag{1.1}$$

where  $E_n(k)$  is the dispersion relation for charge carriers in the nth energy band,  $\hbar$  is the reduced Planck constant, and  $k_i$  and  $k_j$  are the ith and jth element of the wave vector k. In many practical cases, for small energies relative to the band edges, the dispersion relation E(k) can be approximated as parabolic and isotropic so that the second derivative in (1.1) is a constant. This is known as the *effective mass approximation*. For some (doped) III-V materials, due to their low density of states, the Fermi level can move quite far into the energy bands so that E(k) deviates from this parabolic approximation. From  $k \cdot p$  perturbation theory, to a first order, this can be taken into account by a modified dispersion relation as  $E(k)(1 + \alpha E(k)) = \hbar^2 k^2/(2m^*)$  with the non-parabolicity factor  $\alpha$  [17].

In state-of-the-art MOSFETs, the conducting channel is typically formed by a 2D electron gas and the effective gate length is so short that electrons pass the channel ballistically, i.e. without scattering. For a fully ballistic 2D MOSFET in the on-state (i.e. large  $V_{\rm DS}$  and  $V_{\rm GS}\gg V_{\rm T}$ ) the current can be described as [18, p. 100]<sup>†</sup>

$$I^{\rm 2D} \approx \frac{2qW_{\rm G}\sqrt{2m^*}}{3\pi^2\hbar^2} \left(\frac{qC'_{\rm ox}}{C'_{\rm ox} + \frac{C_{\rm q}^{\rm 2D}}{2}}\right)^{3/2} (V_{\rm GS} - V_{\rm T})^{3/2},$$

(1.2)

where q is the elemental charge,  $C'_{\rm ox}$  is the series combination of the oxide capacitance and the centroid capacitance,  $C^{\rm 2D}_{\rm q}$  is the 2D quantum capacitance, and all other parameters are as before. The centroid capacitance, from first-order perturbation theory, takes into account the shift in energy of the bottom of the sub bands when they are occupied by charge carriers. Due to their small channel diameters, the nanowire MOSFETs which have been studied for this thesis approach 1D transport characteristics. In this case, the current can be expressed as [18, p. 146]

$$I^{1D} = \frac{2q^2}{h} \frac{C'_{\text{ox}}}{C'_{\text{ox}} + C_{\text{q}}^{1D}} (V_{\text{GS}} - V_{\text{T}}), \qquad (1.3)$$

where h is the Planck constant and  $C_q^{1D}$  the 1D quantum capacitance.

The general definition of the quantum capacitance  $C_{\rm q}$  (of each occupied sub band) in (1.2) and (1.3) is  $C_{\rm q}=q\partial n/\partial\psi_{\rm s}$  with the carrier density n (in the respective dimensionality) and the surface potential  $\psi_{\rm s}$  at the top of the channel barrier [18, p. 51]. With this,  $C_{\rm q}^{\rm 2D}$  and  $C_{\rm q}^{\rm 1D}$  for each sub band can be expressed as

$$C_{\rm q}^{\rm 2D} = \frac{q^2 m^*}{\pi \hbar^2}$$

(1.4a) and  $C_{\rm q}^{\rm 1D} = \frac{q^2}{\pi \hbar} \sqrt{\frac{2m^*}{E_{\rm F} - \mathcal{E}(0)}}$ , (1.4b)

where  $E_{\rm F}$  and  $\mathcal{E}(0)$  in (1.4b) denote the Fermi level and the bottom of the sub band, respectively. From (1.2)–(1.4) it can be seen that for a constant drive voltage, to a first order, higher on-currents can be achieved by using channel materials with lower effective masses. Furthermore, the quantum capacitances in (1.4) almost directly determine the density of states in a MOSFET channel so that low effective masses also entail low densities of states (DOS) [18, p. 7]. This can be beneficial for high frequency operation, as

<sup>&</sup>lt;sup>†</sup>The expressions differ a little, because [18] uses the MOS limit, i.e. assumes that  $C_q \gg C_{ox}$ , which is usually not appropriate for III-V MOSFETs.

investigated in Chapter 3, since lower DOS lead to lower gate capacitances. As a another useful relation, by employing first-order perturbation theory it can be shown that in materials with parabolic bands, a low effective mass is linked to a small band gap [19, p. 69], which explains the corresponding correlation in Table 1.1.

In the drift-diffusion equation, which describes long channel MOSFETs, the current is often expressed in terms of the mobility  $\mu$  rather than the effective mass. The drift-diffusion model is only valid for effective gate lengths  $L_{\rm eff}\gg 2k_{\rm B}T\mu_{\rm eff}/(qv_{\rm th})$  with the effective carrier mobility  $\mu_{\rm eff}$  and the thermal velocity  $v_{\rm th}=\sqrt{2k_{\rm B}T/(\pi m^*)}$  [18, p. 96]. In ballistic MOSFETs, the corresponding alternative metric to the effective mass is the injection velocity  $v_{\rm inj}$ , which is used in a simpler formulation of the MOSFET on-current,  $I=q(n^+-n^-)v_{\rm inj}$ , where  $n^+$  and  $n^-$  are the concentrations of charge carriers with positive and negative directed moments, respectively [18]. Table 1.1 provides examples of material parameters for III-V materials used in devices in this thesis. Values for graphene are provided as a further reference, since graphene has attracted

**Table 1.1:** Important material parameters (at room temperature) for Si, Ge, two III-V materials used in devices in this thesis, and graphene. Values for semiconductors were obtained from [20] and values for graphene from [21–23]. All values indicate upper limits for pure and free-standing materials and are typically not achieved in actual devices.  $m_0$  is the electron rest mass.

| Material                                           | Si                 | Ge                 | InGaAs <sup>c</sup> | InAs              | Graphene                  |

|----------------------------------------------------|--------------------|--------------------|---------------------|-------------------|---------------------------|

| Band gap $E_g$ (eV)                                | 1.12 <sup>id</sup> | 0.66 <sup>id</sup> | 0.74 <sup>d</sup>   | 0.35 <sup>d</sup> | 0 <sup>d</sup>            |

| Effective electron mass $m_e^*/m_0$                | 0.26               | 0.12               | 0.041               | 0.023             | $\sim \! 0.033^{\dagger}$ |

| Effective light hole mass $m_h^*/m_0$              | 0.16               | 0.043              | 0.052               | 0.026             | $\sim \! 0.045^{\dagger}$ |

| Electron injection velocity $v_{\text{inj}}$ (m/s) | $2.3\times10^5$    | $3.1 \times 10^5$  | $5.5 \times 10^5$   | $7.7 \times 10^5$ | $\sim 1 \times 10^6$      |

| Electron mobility $\mu_e$ (cm <sup>2</sup> /(Vs))  | 1400               | 3900               | 12 000              | 40 000            | 200 000                   |

| Hole mobility $\mu_h \text{ (cm}^2/\text{(Vs))}$   | 450                | 1900               | 300                 | 500               | ‡                         |

$^{c}$ In<sub>0.53</sub>Ga<sub>0.47</sub>As.  $^{id}$  and  $^{d}$  indicate indirect and direct band gaps, respectively.  $^{\dagger}$ Note that a different definition than (1.1) has to be used for graphene, since its dispersion relation is not parabolic.  $^{\ddagger}$ Due to the almost symmetric band structure of graphene,  $\mu_h^*$  should be similar to  $\mu_e^*$ , but values as high as for  $\mu_e^*$  were not reported in [22].

a lot of interest due to its potentially outstanding transport properties as well. Note that a different definition for  $m^*$  than provided by (1.1) has to be used for graphene, since it exhibits an almost linear dispersion relation.

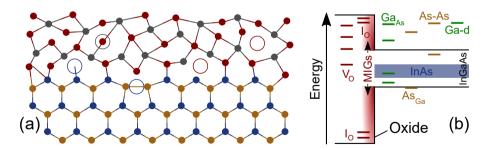

The values in Table 1.1 clearly demonstrate the promising material properties of III-V materials with much lower effective masses and higher mobilities than the most common MOSFET material Si. It should be noted, though, that in transistors, the mobility is often greatly reduced by scattering due to ionised dopants and/or due to material defects at the channel/oxide interface and in the bulk of the oxide [24, 25]. It is much more difficult to obtain high-quality gate oxides and interfaces on III-V channels [26, 27] than on Si and effects resulting from different kinds of gate oxide defects are a central topic of this thesis. The effective mass in Si can be lowered to some degree by inducing strain in the channel [28], but for very-high-frequency and low-power transistors, it constitutes a severe limitation.

Besides III-V materials, many more candidates with promising properties are being studied for transistor applications. Examples encompass carbon nanotubes, the aforementioned graphene, or other 2D materials such as transition metal dichalcogenides, but a more thorough discussion is beyond this overview.

#### 1.4.2 GEOMETRIES

A second major complement to the traditional geometric scaling has been the introduction of new device geometries for MOSFETs. In recent years, FinFET/tri-gate and silicon on insulator (SOI) geometries have replaced the formerly planar MOSFETs in commercial applications, and gate-all-around (GAA) structures are being investigated for the coming generations of tran-

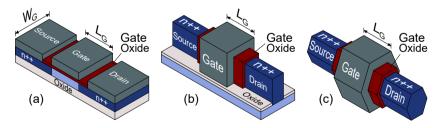

**Figure 1.2:** Schematic representations of advanced MOSFET structures. (a) Silicon on insulator. The buried oxide suppresses substrate leakage and reduces the intrinsic capacitances. (b) FinFET/tri-gate. Electrostatic control is strongly improved by gating the channel from three sides instead of only one. (c) Gateall-around. Optimised electrostatic control due to gating from all sides. The nanowire structure also facilitates the co-integration of different materials.

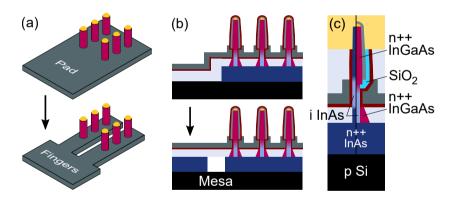

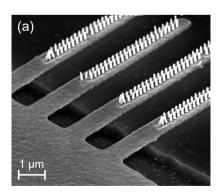

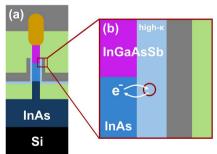

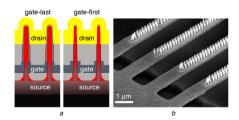

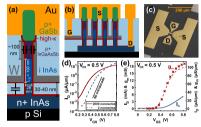

sistors. In this thesis, especially vertical nanowire GAA MOSFETs are investigated extensively. Schematics of the different device structures are presented in Fig. 1.2 and Fig. 1.3, and a performance overview for different architectures can be found in Section 1.5.

In the SOI device structure in Fig. 1.2(a) a buried oxide underneath the channel suppresses leakage current in areas where the gate electric field decreases. It also reduces the intrinsic capacitances of the transistor, which is beneficial for high frequency applications. The FinFET/tri-gate structure in Fig. 1.2(b) takes this approach further by raising up the channel from the substrate into a fin, which can be gated from three sides. With the resulting increased electrostatic control, short-channel effects can be suppressed more efficiently so that thicker gate oxides as well as thicker and/or shorter channels are possible [29]. The ultimate electrostatic integrity can be achieved in GAA nanowire structures such as the one in Fig. 1.2(c), where the gate completely encloses the channel [30]. This structure, especially in a vertical orientation as in Fig. 1.3, also greatly facilitates the co-integration of different semiconductor materials, since the nanowire geometry allows a relatively easy strain relaxation of mismatched lattice constants [31]. This is very beneficial for engineering the band structure along the channel, which is of special

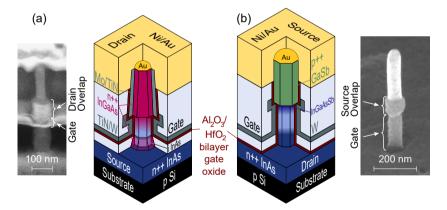

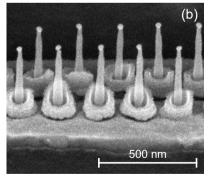

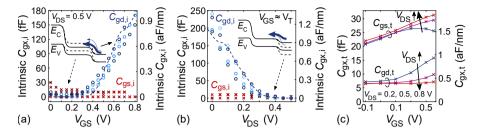

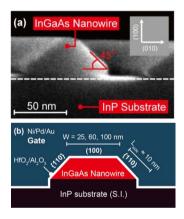

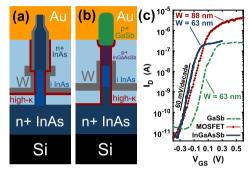

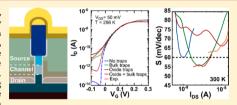

**Figure 1.3:** Schematic representations and scanning electron micrographs ('SEM images') of the vertical nanowire transistors studied in this thesis. (a) MOSFET; operation with the drain contact at the top provides higher oncurrents and lower off-currents, but the device can also be operated with the drain in the bottom. The SEM image (courtesy O.-P. Kilpi) shows a cut (by a focused ion beam) through the sample next to a complete device. (b) TFET; the asymmetric transport principle precludes operation with the source in the bottom. The SEM image (courtesy A. Krishnaraja) was taken during processing after deposition of the gate metal.

importance for the TFETs, as explained in Section 1.6. Furthermore, a vertical geometry decouples the gate length from the area footprint of a device, which allows a dense spacing of devices on a chip even for relatively long gate lengths. Vertical nanowire MOSFETs could also prove instrumental for emerging monolithic 3D integrated chip architectures, which aim to overcome the bottleneck of data transmission between computation and memory [32]. All vertical devices fabricated in Lund and characterised in this thesis are integrated on Si substrates for compatibility with industry fabrication schemes. Details about the vertical nanowire MOSFETs can be found in [33] and about the TFETs in [34].

#### 1.5 PERFORMANCE OVERVIEW

This section summarises state-of-the-art performance at the time of writing this thesis. Different important metrics are briefly explained and benchmarking figures provide a quantitative comparison of how the different approaches described above enhance transistor performance in practice. The section is divided into a DC and a high frequency part. Details and derivations of all metrics and the underlying transport physics can be found in textbooks such as [18] for the DC metrics and [35] for the high frequency metrics.

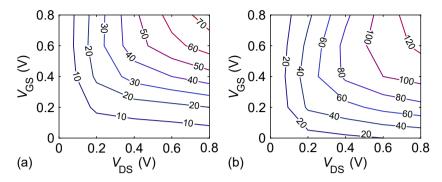

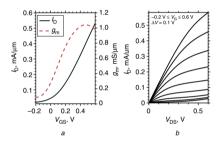

## 1.5.1 DC METRICS

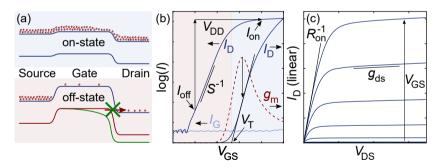

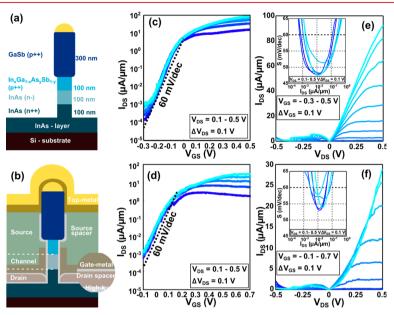

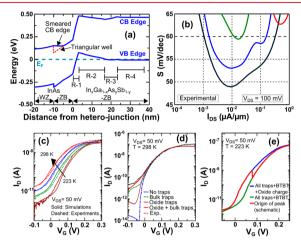

The DC performance of a transistor can be characterised by different metrics, which quantify the relations between the current and the voltages. Examples of the two basic IV curves for this purpose are presented in Fig. 1.4. They are referred to as the *transfer characteristics* (Fig. 1.4(b) currents vs. gate-to-source voltage  $V_{\rm CS}$ ) and *output characteristics* (Fig. 1.4(c) drain current  $I_{\rm D}$  vs. drain-to-source voltage  $V_{\rm DS}$ ). To be able to compare the quality of differently sized transistors, some of these metrics are often normalised by the gate width  $W_{\rm G}$  of the transistor, see Fig. 1.1(a). For fin or GAA structures, typically, the perimeter of the gated surface is used for normalisation.

In industry, typically, an application-dependent off-current  $I_{\rm off}$  is defined (e.g.  $1\,{\rm nA/\mu m}$ ) and used to determine the on-current  $I_{\rm on}$  by moving along the voltage axis of the transfer curve in Fig. 1.4(b) by an amount  $V_{\rm DS}$ , sometimes called the drive voltage  $V_{\rm DD}$ , at which the transfer curve was measured. The minimum off-state current can be limited by detrimental factors such as gate leakage, direct source-to-drain tunnelling for very short channel lengths ( $\lesssim 20\,{\rm nm}$ ), band-to-band tunnelling (BTBT) on the drain side, or thermionic emission from the high-energy tail of the electron distribution. A suppression of BTBT on the drain side can be achieved by grading the channel

material composition, see Fig. 1.4(a), for which vertical III-V nanowires are very suitable [36]. To obtain a specific number, which characterises the transition between off- and on-state, the so-called threshold voltage  $V_T$  can be determined. One way to do so consistently is demonstrated in Fig. 1.4(b) as well:  $V_T$  is given by the point, where the linear extrapolation of  $I_D$  from the point of the maximum transconductance  $g_{\rm m}$  intersects the voltage axis. The transconductance  $g_{\rm m}$  in turn is the derivative of  $I_{\rm D}$  with respect to  $V_{\rm GS}$ ,  $g_{\rm m} = \partial I_{\rm D}/\partial V_{\rm GS}$ . As such,  $g_{\rm m}$  is an important metric in its own right, since it describes how efficiently small changes in the gate voltage modulate the current. Typically, g<sub>m</sub> is an important metric for the on-state performance, since it determines the gain that a transistor can provide and as such, high values for  $g_{\rm m}$  are especially important for high frequency applications. The current modulation by the gate in the off-state is characterised by the inverse subthreshold slope  $S = (\partial \log(I_D)/\partial V_{GS})^{-1}$ , also referred to as subthreshold swing, and indicated in Fig. 1.4(b). Ideally, a MOSFET exhibits high values for  $g_{\rm m}$  for high gain, and low values for S for low off-state leakage. Further on-state metrics, indicated in Fig. 1.4(c), are the on-resistance  $R_{\rm on}$  and the output conductance  $g_{ds}$ , which are ideally as small as possible. The inverse subthreshold slope S in a conventional MOSFET is physically limited to  $\sim$ 60 mV/decade, which will be discussed in more detail in Section 1.6. As an overview of state-of-the-art MOSFET performance, Fig. 1.5 presents reported

**Figure 1.4:** The most important IV curves to characterise the DC performance of a MOSFET alongside the band diagrams from Fig. 1.1 to illustrate the relation between currents and band alignment. (a) Band diagrams. The red valence band in the off-state illustrates band-to-band tunnelling as one of the possible sources for increased off-state current, the green valence band illustrates a compositionally graded channel with a larger band gap material on the drain side to suppress this. (b) Transfer characteristics, currents as a function of  $V_{\rm GS}$ . Important metrics are indicated together with ways to extract them. (c) Output characteristics,  $I_{\rm D}$  as a function of  $V_{\rm DS}$ , with important metrics.

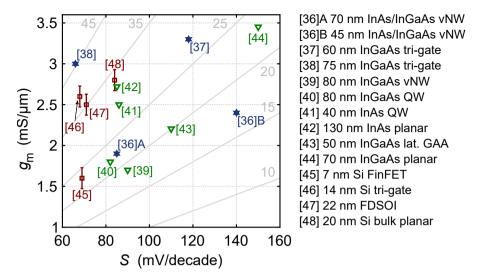

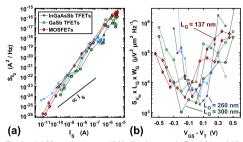

**Figure 1.5:** Maximum transconductance  $g_{\rm m}$  vs. minimum inverse subthreshold slope S for different reported state-of-the-art MOSFETs (with different gate lengths). Blue stars and green triangles are for III-V [36–44], where blue stars indicate the types of transistors characterised in this thesis. Grey lines indicate the quality factor  $Q=g_{\rm m}/S$ .  $g_{\rm m}=3.1{\rm mS/\mu m}$  was demonstrated for vertical III-V nanowire RF devices in [33], but the devices did not turn off properly and thus do not appear in the figure. Si devices (red squares, [45–48]) are provided as references and error bars are provided since the values were not reported explicitly, but calculated from reported IV curves. Values for III-V MOSFETs are for  $V_{\rm DS}=0.5$  V and values for Si are for  $V_{\rm DS}=0.7$ –0.9 V. Acronyms in the legend: vNW – vertical nanowire; QW – quantum well; lat. GAA – lateral gate-all-around; FDSOI – fully depleted silicon on insulator.

values for  $g_m$  vs. S for different MOSFETs. III-V devices, among them the ones fabricated in Lund and characterised in this thesis, compare very well with commercial Si devices despite the largely different efforts of optimisation that have gone into the respective technologies.

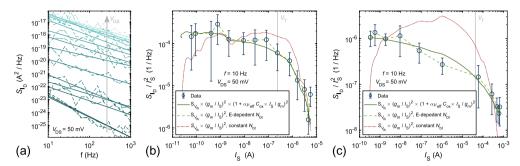

## 1.5.2 HIGH FREQUENCY METRICS

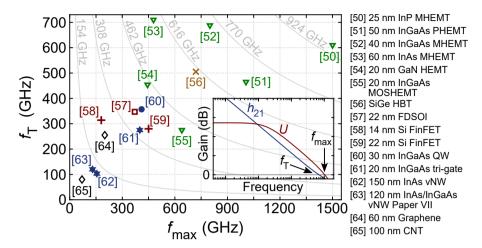

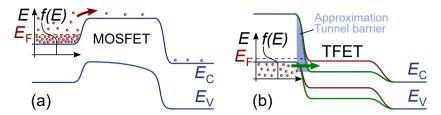

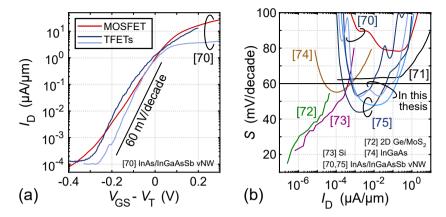

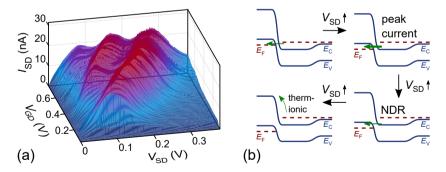

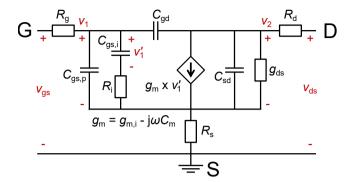

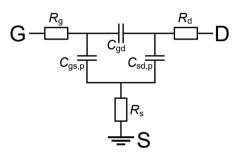

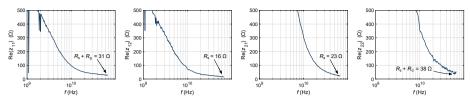

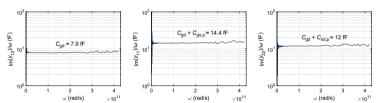

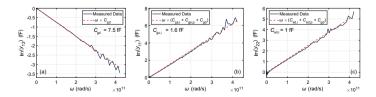

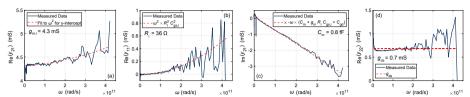

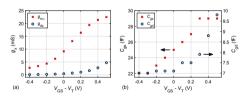

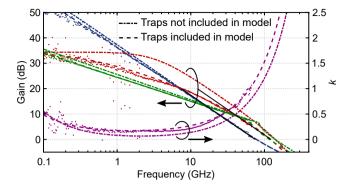

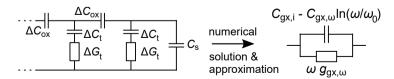

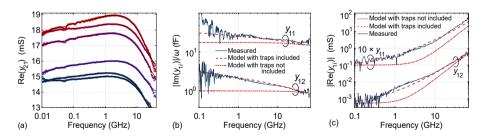

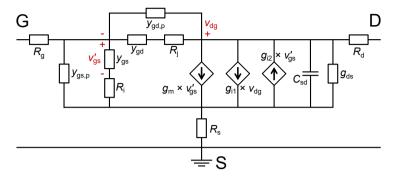

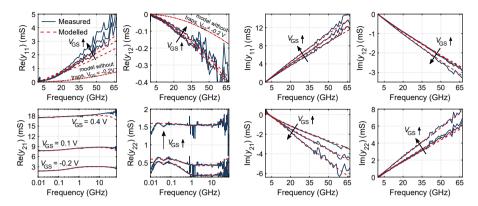

Besides the metrics which can be obtained from DC operation, there are some metrics which describe the high frequency performance of a transistor. The most important ones in the context here are the cutoff frequency  $f_T$  and the maximum oscillation frequency  $f_{max}$ , which denote the frequencies, at which the forward current gain  $h_{21}$  and the unilateral power gain U, respectively, decrease to one so that the transistor cannot act as an amplifier anymore at